概述

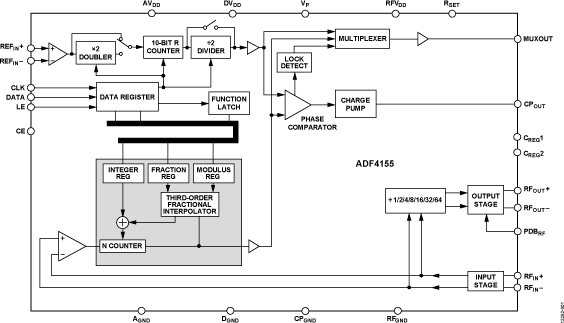

ADF4155结合外部环路滤波器、外部压控振荡器(VCO)和外部基准频率使用时,可实现小数N分频或整数N分频锁相环(PLL)频率合成器。

ADF4155能够与外部VCO器件配合使用,工作频率高达8 GHz。 高分辨率可编程模块允许精确频率合成,误差为0 Hz。

VCO频率可进行1、2、4、8、16、32或64分频,因此用户可以产生低至7.8125 MHz的RF输出频率。

所有片内寄存器均通过简单的三线式接口进行控制。 该器件采用3.3 V ± 5%标称电源供电,不用时支持关断功能。

ADF4155采用24引脚4 mm x 4 mm LFCSP封装。

数据表:*附件:ADF4155整数N 小数N分频PLL频率合成器技术手册.pdf

应用

特性

- 输入频率范围: 500 MHz至8,000 MHz

- 小数N分频频率合成器和整数N分频频率合成器

- 高达125 MHz的鉴频鉴相器(PFD)

- 高分辨率38位模块

- 独立的电荷泵电源(VP)可在5 V系统中提供扩展的调谐电压

- 可编程1/2/4/8/16/32/64分频输出

- 差分和单端基准输入

- 电源: 3.3 V ± 5%

- 逻辑兼容性: 1.8 V

- 可编程双模预分频器(P):4/5或8/9

- 可编程的输出功率

- 三线式串行接口

- 模拟和数字锁定检测

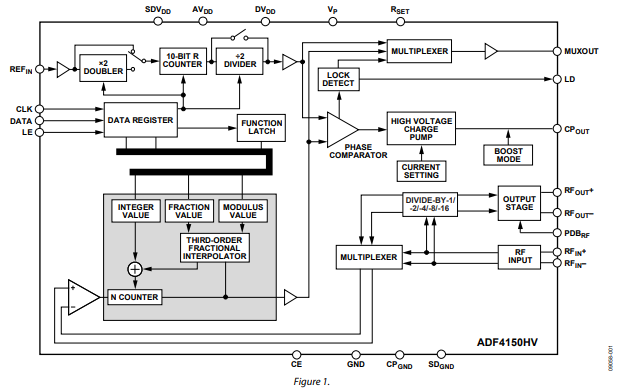

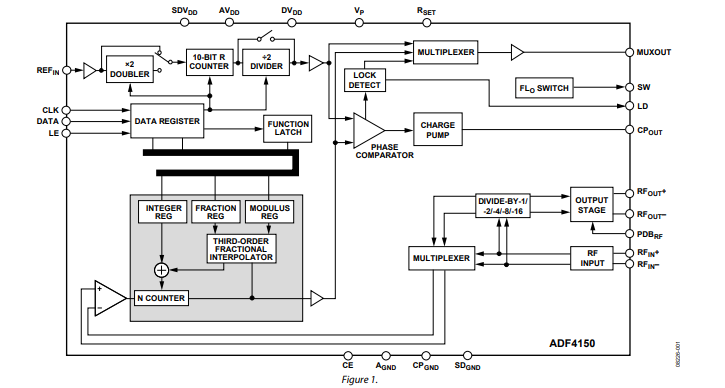

框图

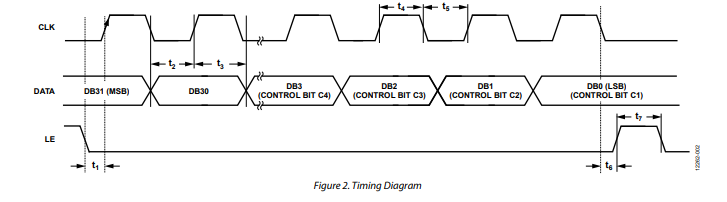

时序图

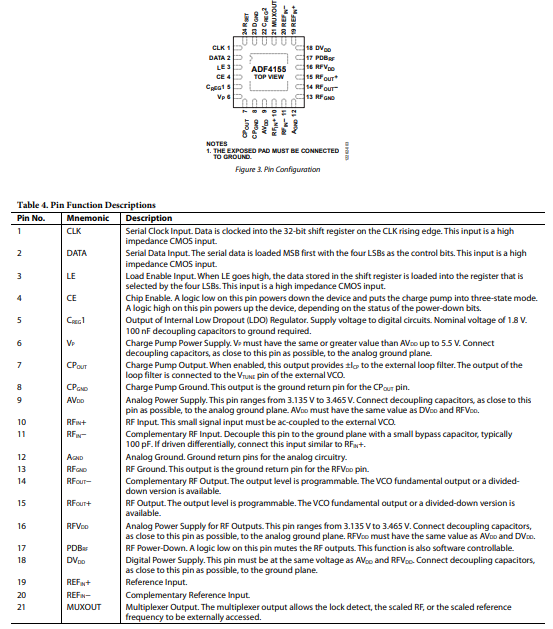

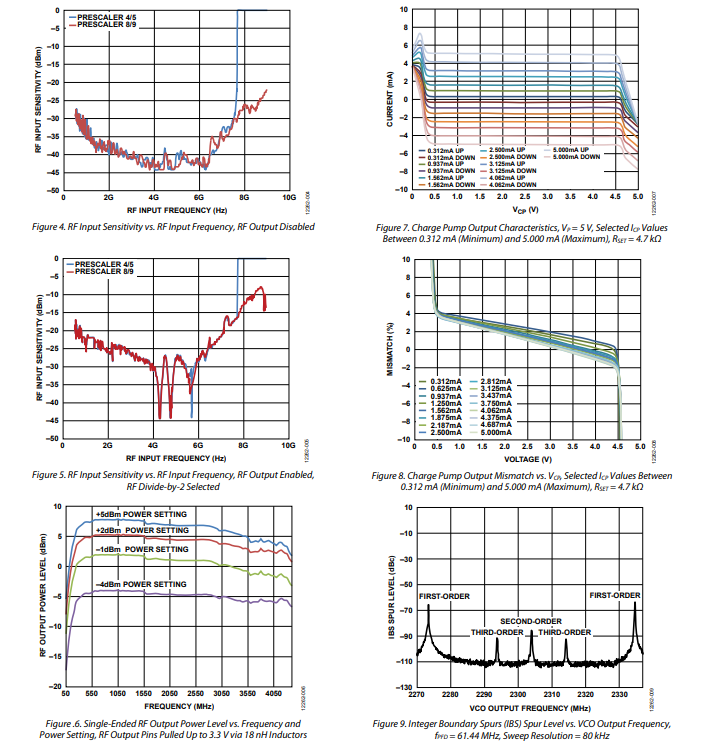

引脚配置描述

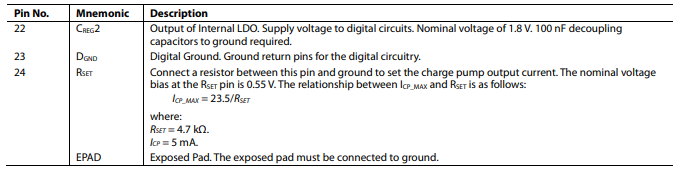

典型性能特征

电路描述

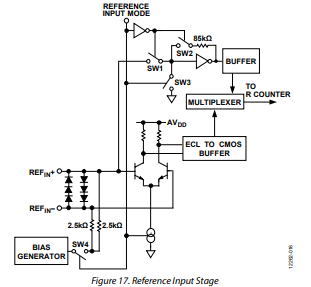

参考输入部分

参考输入级如图17所示。参考输入可接收单端和差分信号,其选择由参考输入模式位(寄存器6中的DB30位)控制。若要使用差分信号作为参考输入,该位必须编程为高电平。此时,SW1和SW2断开,SW3和SW4闭合,驱动差分对晶体管的电流源开启。差分信号经缓冲后,在提供给CMOS转换器之前先转换为发射极耦合逻辑(ECL)信号。当使用单端信号作为参考信号时,寄存器6中的DB30位必须编程为0。此时,SW1和SW2闭合,SW3和SW4断开,驱动差分对晶体管的电流源关闭。

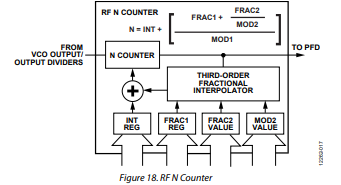

射频N计数器

射频N计数器可在锁相环(PLL)反馈路径中实现分频比。该分频比由INT、FRAC1、MOD1、FRAC2和MOD2这些值决定,如图18所示。请注意,MOD1是一个固定的不可编程值,等于$2^{24}$。

INT、FRAC、MOD和R计数器关系

INT、FRAC1、FRAC2、MOD1和MOD2这些值与R计数器配合,能够生成间隔为鉴频鉴相器(PFD)频率分数倍的输出频率。更多信息请参见“射频合成器——实例”部分。

使用以下公式计算射频压控振荡器(VCO)频率(RF_{OUT}):

其中:

- **RF_{OUT}**是外部VCO压控振荡器的输出频率(不使用输出分频器 )。

- **f_{PFD}**是鉴频鉴相器频率。

- N是反馈计数器N的目标值。

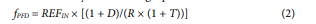

使用以下公式计算f_{PFD}:

其中:

- **REF_{IN}**是参考输入频率。

- D是**REF_{IN}**倍频位。

- R是10位二进制可编程参考计数器的预设分频比(1至1023 )。

- T是**REF_{IN}**二分频位(0或1 )。

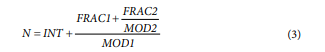

N由以下公式计算:

其中:

- INT是16位整数值(对于4/5预分频器,为23至32,767;对于8/9预分频器,为75至65,535 )。

- FRAC1是主模数(1至16,777,215 )的分子。

- FRAC2是14位辅助模数(1至16,383 )的分子。

- MOD2是可编程的14位辅助分数模数(2至16,383 )。

- MOD1是固定值为$2^{24}$ = 16,777,216的24位主模数。

此计算可实现非常精细的频率分辨率,且无残留频率误差。要应用此公式,请按以下步骤操作:

- 用RF_{OUT}除以f_{PFD}计算N。

- 取该数值的整数部分作为INT。

- 从完整的N值中减去INT。

- 将余数乘以$2^{24}$ 。

- 取该数值的整数部分作为FRAC1。

- 根据信道间隔(f_{CHSP}),使用以下公式计算MOD2:

其中:

- **GCD(f_{PFD}, f_{CHSP})**是PFD频率和信道间隔频率的最大公约数。

- **f_{CHSP}**是所需的信道间隔频率。

- 使用以下公式计算FRAC2:

-

频率合成器

+关注

关注

5文章

368浏览量

33915 -

pll

+关注

关注

6文章

991浏览量

138415 -

VCO

+关注

关注

14文章

321浏览量

71450

发布评论请先 登录

ADF4155 整数N/小数N分频PLL频率合成器

ADF4155整数N/小数N分频PLL频率合成器技术手册

ADF4155整数N/小数N分频PLL频率合成器技术手册

评论