在使用 AMD Vivado Design Suite 对开发板(Evaluation Board)进行 FPGA 开发时,我们通常希望在创建工程时直接选择开发板,这样 Vivado 能够自动配置

2025-07-15 10:19:43 1523

1523

基于FPGA vivado 17.2 的数字钟设计

2018-06-08 09:41:47 11515

11515

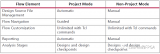

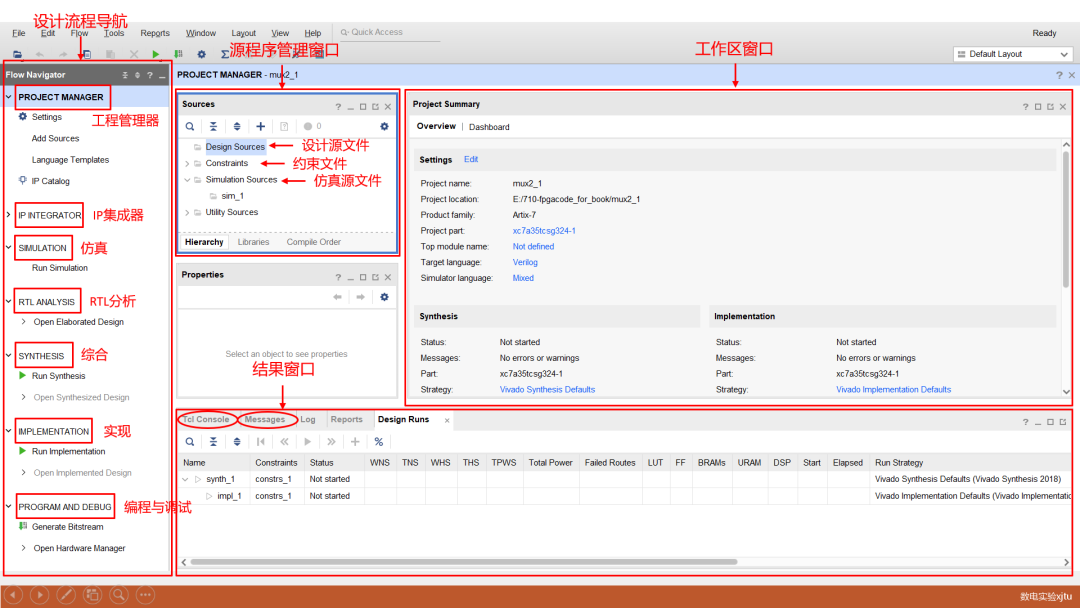

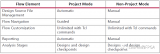

01. Vivado的两种工作模式 Vivado设计有工程和非工程两种模式: 1. 工程模式: 工程模式是使用Vivado Design Suite自动管理设计源文件、设计配置和结果,使用图形化

2020-11-09 17:15:47 5785

5785

作者:Mculover666 1.实验目的 通过例程探索Vivado HLS设计流 用图形用户界面和TCL脚本两种方式创建Vivado HLS项目 用各种HLS指令综合接口 优化Vivado HLS

2020-12-21 16:27:21 4357

4357 仿真功能概述 仿真FPGA开发中常用的功能,通过给设计注入激励和观察输出结果,验证设计的功能性。Vivado设计套件支持如下仿真工具:Vivado Simulator、Questa、ModelSim

2020-12-31 11:44:00 6234

6234

FPGA 的设计流程简单来讲,就是从源代码到比特流文件的实现过程。大体上跟 IC 设计流程类似,可以分为前端设计和后端设计。

2023-04-23 09:08:49 3022

3022

为了尽快把新产品推向市场,数字系统的设计者需要考虑如何加速设计开发的周期。设计加速主要可以从“设计的重用”和“抽象层级的提升”这两个方面来考虑。Xilinx 推出的 Vivado HLS 工具可以

2025-04-16 10:43:12 1432

1432

。Axcelerator和Vivado是常用的综合工具,其中Vivado是由Xilinx公司开发的EDA工具。

在布局布线方面,FPGA工程师需要使用工具将逻辑网表传输到物理布局中。在这个过程中

2023-11-09 11:03:52

一、总体流程开发工具:Vivado2020VerilogARTIX-7 FPGA AX7035这是我做的完整流程,涉及到初级开发的功能;新建工程:(RTL Project)芯片选型;编写程序:源文件

2021-07-22 07:35:26

,这也就要求设计者从设计一开始就要非常认真细致,来不得半点的马虎,否则后续的很多工作量可能就是不断的返工。(特权同学版权所有)1.6 FPGA开发流程当然了,对于没有实际工程经验的初学者而言,这个流程

2015-03-31 09:27:38

,这也就要求设计者从设计一开始就要非常认真细致,来不得半点的马虎,否则后续的很多工作量可能就是不断的返工。(特权同学版权所有)图1.6 FPGA开发流程当然了,对于没有实际工程经验的初学者而言,这个

2019-01-28 04:24:37

今天主要介绍一下整个FPGA板下载运行调试流程。

1、首先,参考网址https://doc.nucleisys.com/hbirdv2/soc_peripherals/ips.html#gpio 第

2025-10-29 06:37:01

今天主要介绍一下整个FPGA板下载运行调试流程。

1、首先,参考网址https://doc.nucleisys.com/hbirdv2/soc_peripherals/ips.html#gpio 第

2025-10-29 06:57:46

II、Vivado等)、仿真软件(ModelSim等)的使用5、熟悉FPGA设计流程(仿真,综合,布局布线,时序分析)。6、熟练掌握资源估算(特别是slice,lut,ram等资源的估算)。7、同步

2020-10-22 17:08:15

Vivado概述 / 251.3.1 Vivado下的FPGA设计流程 / 251.3.2 Vivado的两种工作模式 / 261.3.3 Vivado的5个特征 / 30参考文献 / 31第2章

2020-10-21 18:24:48

`Vivado 开发环境简介及设计流程`

2017-12-12 10:15:48

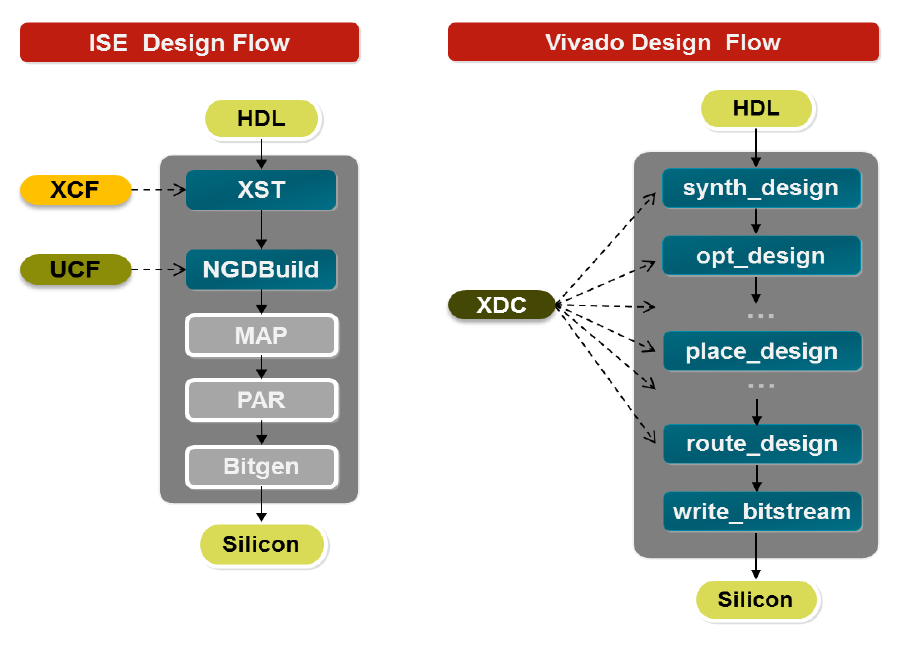

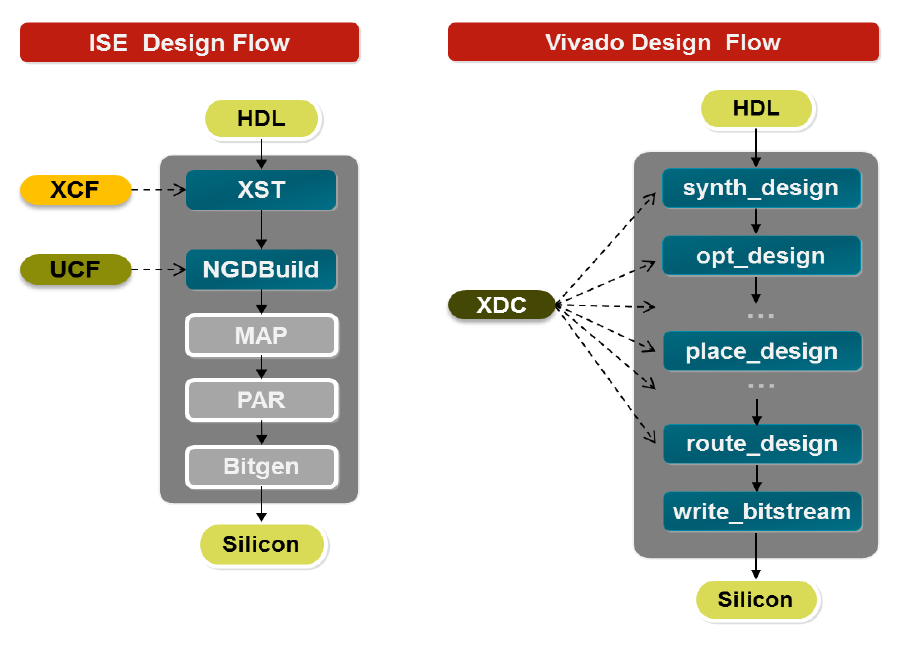

不支持更老的设备(Spartan, Virtex-6 以及之前的 FPGA) 。同样 ,ISE 也不再支持 7 系列之后的设备ISE 和 Vivado 之间另一个重要的区别就是约束文件的类型。在 ISE

2021-01-08 17:07:20

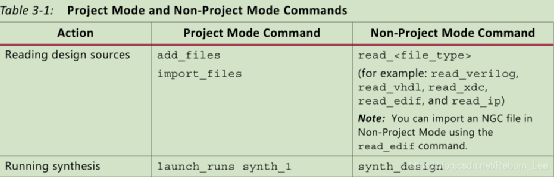

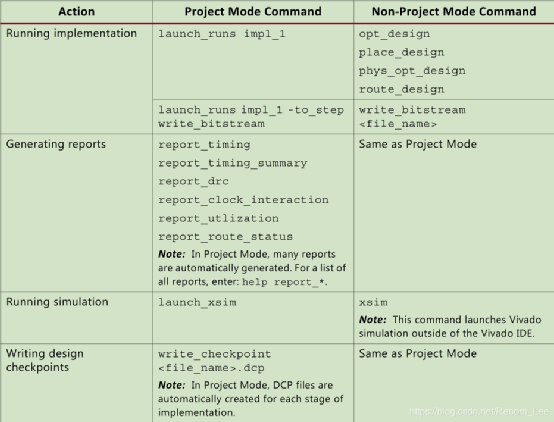

Vivado 设计分为 Project Mode 和 Non-project Mode 两种模式,一般简单设计中,我们常用的是 Project Mode。在本手册中,我们将以一个简单的实验案例,一步一步的完成 Vivado的整个设计流程。

2023-09-20 07:37:39

下面b) 采用manage IP的设计流程11.把自己的代码封装成一个IP,初学xilinx的fpga设计,好多东西都没有概念,真是一头雾水,比起Altera的开发环境,这个vivado真的是困难太多

2016-11-09 16:08:16

本书收集整理了作者在FPGA学习和实践中的经验点滴。书中既有日常的学习笔记,对一些常用设计技巧和方法进行深入探讨;也有很多生动的实例分析,这些实例大都是以特定的工程项目为依托,具有一定的借鉴价值

2014-12-29 16:57:26

分析,这些实例大都是以特定的工程项目为依托,具有一定的借鉴价值;还有一些适合于初学者入门和进阶学习的实验例程;另外还给出了两个比较完整的DIY工程,让读者从系统角度理解FPGA的开发流程。第一部

2012-02-27 10:45:37

LabVIEW 深入探索

2015-07-01 10:54:43

LabVIEW_深入探索

2012-08-31 13:53:31

`LabVIEW_深入探索`

2012-08-19 13:38:42

Labview 深入探索

2013-04-11 18:09:31

Labview深入探索的很好资料哦

2012-04-27 21:29:59

在拨号界面输入“*#*#3646633#*#*”会出现一个界面,这个界面就是工程模式设置界面。下面对听筒音量进行调整。选择Hardware Testing --> AUDIO,先修改

2016-09-18 21:06:00

我刚刚在 STMCubeIDE 中为 STM32MP157A-DK1 创建了一个项目,并尝试在工程模式和生产模式下运行 MCU 调试。我使用 ST-LINK 线和 Ethernet Over USB

2022-12-12 08:25:41

本帖最后由 夏良涛FPGA 于 2020-4-9 12:33 编辑

XILLINX VIVADO快速上手-HDL流程-内含视频、工程和中文版ppt200多M大小 只能网盘了。链接:https://pan.baidu.com/s/1wNkSIJeO7G86YGjy0CtJ6g 提取码:zjev

2020-04-09 11:30:45

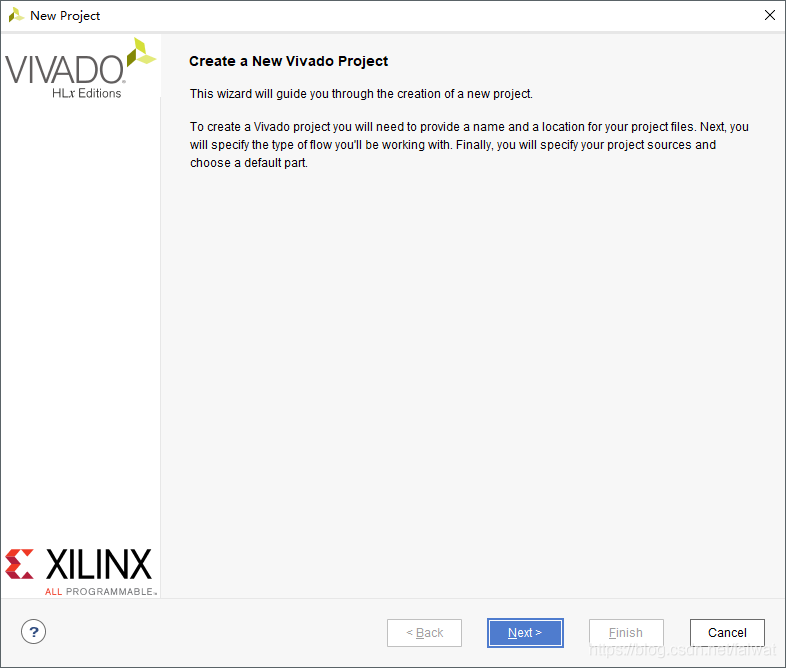

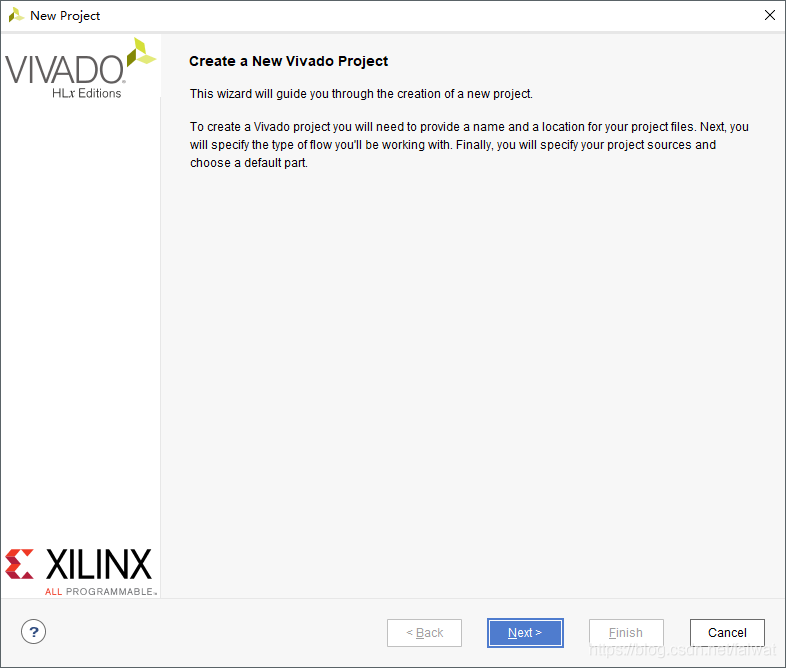

开发设计流程。话不多说,上货。Xilinx FPGA Vivado 开发流程在做任何设计之前,我们都少不了一个工作,那就是新建工程,我们设计的一些操作,必须在工程下完成,那么接下来就向大家介绍一下新建工程的步骤

2023-04-13 15:18:52

开发过程中的一个重要特点,这就要求设计者从一开始就要非常认真细致,否则后续的很多工作量可能就是不断的返工。图1.32 FPGA开发流程 基于Xilinx的Vivado开发工具,我们对以上开发流程所涉

2019-04-01 17:50:52

《大语言模型“原理与工程实践”》是关于大语言模型内在机理和应用实践的一次深入探索。作者不仅深入讨论了理论,还提供了丰富的实践案例,帮助读者理解如何将理论知识应用于解决实际问题。书中的案例分析有助于

2024-05-07 10:30:50

善用Vivado工程配置文件xpr快速工程创建对于第一次新建工程,没啥捷径,建议大家规规矩矩的使用Vivado的GUI创建工程。完成工程创建后,我们找到这个新建工程下的.xpr文件,它是工程配置文件

2016-10-19 18:05:13

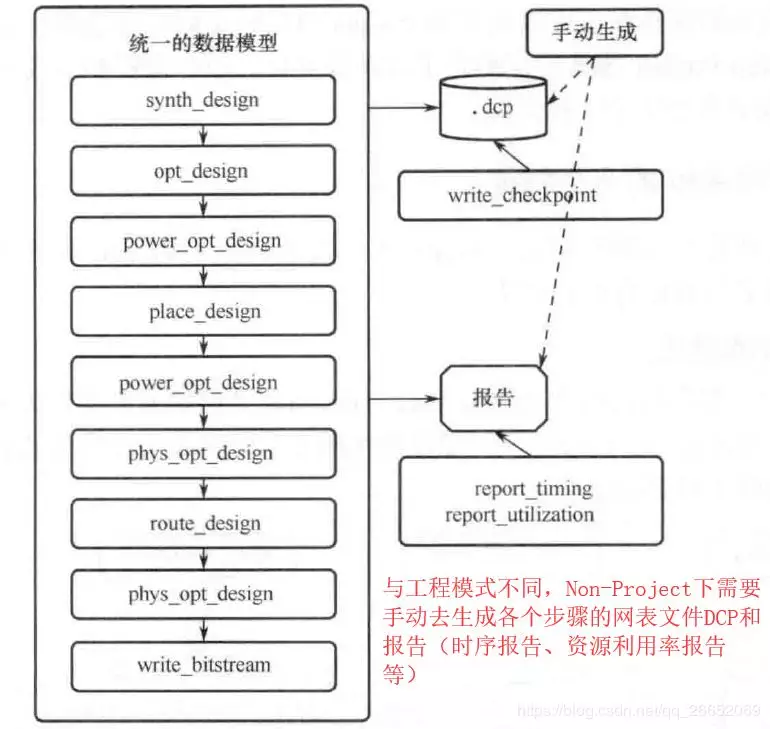

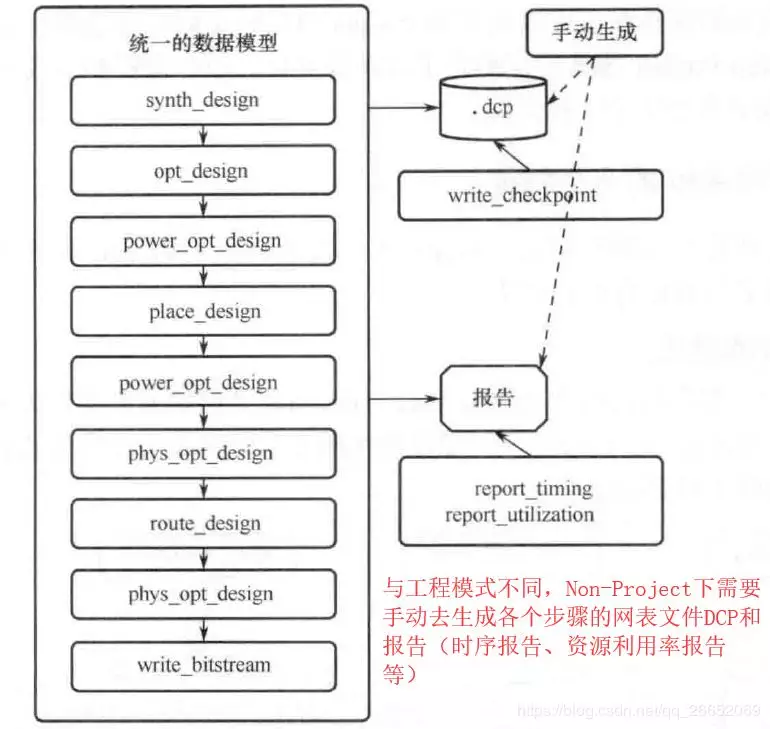

,Vivado工具可自动管理设计流程和设计数据,各种数据都比较直观。非工程模式是一直内存编译流程,所有步骤都需要开发者手动编辑脚本,命令和参数,这样的模式开发者对设计流程有完全的掌控力。目前,更多的人

2022-06-17 14:52:14

、书籍、源码、技术文档…(2023.07.09更新)

本篇掌握基于 FPGA Vivado 信号发生器设计(附源工程),掌握基于添加文件和IP的Vivado工程设计流程,掌握基于Tcl

2023-08-15 19:57:56

今天给大侠带来基于 FPGA Vivado 的数字钟设计,开发板实现使用的是Digilent basys 3。话不多说,上货。

需要源工程可以在以下资料获取里获取。

资料汇总|FPGA软件安装包

2023-08-18 21:18:47

今天给大侠带来基于 FPGA Vivado 示波器设计,开发板实现使用的是Digilent basys 3,话不多说,上货。

需要源工程可以在以下资料获取里获取。

资料汇总|FPGA软件安装包

2023-08-17 19:31:54

【流水灯样例】基于 FPGA Vivado 的数字钟设计前言模拟前言Vivado 设计流程指导手册——2013.4密码:5txi模拟

2022-02-07 08:02:04

基于FPGA vivado 17.2 的数字钟设计目的:熟悉vivado 的开发流程以及设计方法附件:

2017-12-13 10:16:06

、SW拨码开关以下是官网提供的资料链接:arty a7开发板资料Pmod DA4资料vivado安装说明board files添加基于microblaze的vivado开发流程以下是在vivado2017.4_MicroBlaze_ArtyA735t上的开发流程新建工程注:路径不要有中文名,电

2022-01-18 08:09:43

程序来选择工具。 3. 创建Vivado工程 3.1 首先建立按键的测试工程,添加verilog测试代码,完成编译分配管脚等流程。 `timescale1ns/1ps module

2021-01-06 17:48:21

看了《小梅哥和你一起深入学习FPGA之FPGA设计流程》受益匪浅,所以做个pdf方便大家。

2015-02-04 09:39:22

、USB、Micro SD、CAN、UART等接口,支持LCD显示拓展及Qt图形界面开发,方便快速进行产品方案评估与技术预研。HLS基本开发流程如下:HLS工程新建/工程导入编译与仿真综合IP核封装IP核

2021-11-11 09:38:32

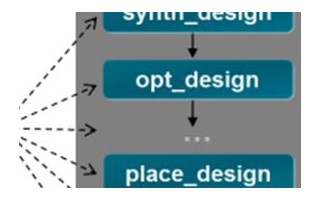

非工程模式下对应的Tcl 命令。右图所示是 Vivado 中设计实现的基本流程,蓝色部分表示实现的基本 步骤(尽管opt_design 这一步理论上不是必选项,但仍强烈建议用户执行),对应

2023-06-28 19:34:58

转帖:采用高级语言开发FPGA的探索近年来,由于人工智能和金融数据分析等计算密集型领域的日益兴起,异构计算越来越受到大家的重视。异构计算是指使用不同类型指令集和体系架构的计算单元组成系统的计算方式

2017-09-25 10:06:29

MTK平台手机进入工程测试模式指令大全

目前MTK平台的开发手机型号越来越多,对应的进工程模式的指令也随之五

2009-12-28 08:13:29 7681

7681 东芝液晶电视工程模式的常用功能(4:3电视不适用): 开机状态下,按一次遥控器的Mute键(静音键),然后按住遥控器的Mute键的同时按电视机的Menu键,即可进入工程菜单

2012-05-14 17:07:04 22046

22046 Introduction to FPGA Design with Vivado High-Level Synthesis,使用 Vivado 高层次综合 (HLS) 进行 FPGA 设计的简介

2016-01-06 11:32:55 65

65 其实Tcl在Vivado中还有很多延展应用,接下来我们就来讨论如何利用Tcl语言的灵活性和可扩展性,在Vivado中实现定制化的FPGA设计流程。 基本的FPGA设计实现流程 FPGA的设计流程简单来讲,就是从源代码到比特流文件的实现过程。大体上跟IC设计流程类似,可以分为前端设计和后端设计。

2017-11-18 01:48:01 4100

4100

资源、速度和功耗是FPGA设计中的三大关键因素。随着工艺水平的发展和系统性能的提升,低功耗成为一些产品的目标之一。功耗也随之受到越来越多的系统工程师和FPGA工程师的关注。Xilinx新一代开发工具Vivado针对功耗方面有一套完备的方法和策略,本文将介绍如何利用Vivado进行功耗分析和优化。

2017-11-18 03:11:50 7860

7860 关于Tcl在Vivado中的应用文章从Tcl的基本语法和在Vivado中的应用展开,介绍了如何扩展甚至是定制FPGA设计实现流程后,引出了一个更细节的应用场景:如何利用Tcl在已完成布局布线的设计上

2017-11-18 18:26:46 5856

5856

本视频教程主要主要介绍Xilinx公司开发设计流程中的各个功能模块,包括ISE中的设计输入,综合,设计实现及验证等内容,此专题将为广大FPGA工程师深入理解EDA工具实现原理与FPGA开发完整流程提供帮助,从而为未来更复杂的设计打下基础。

2018-06-06 13:46:00 4820

4820 本视频教程主要主要介绍Xilinx公司开发设计流程中的各个功能模块,包括ISE中的设计输入,综合,设计实现及验证等内容,此专题将为广大FPGA工程师深入理解EDA工具实现原理与FPGA开发完整流程提供帮助,从而为未来更复杂的设计打下基础。

2018-06-08 02:35:00 5829

5829 Vivado不仅是xlinx公司的FPGA设计工具,用它还可以学习Verilog描述,你造吗?

2018-09-20 09:29:22 10534

10534 我们以8-bit 的LFSR(线性反馈移位寄存器)做一个流水灯为例,介绍Vivado的基本使用。

2018-09-25 16:16:36 16307

16307

单片机是基于FLASH结构的,所以单片机上电直接从本地FLASH中运行。但SRAM 架构的FPGA是基于SRAM结构的,掉电数据就没了,所以需要借助外部电路来配置运行的数据,其实我们可以借助Vivado来学习FPGA的各种配置模式。

2018-11-05 15:12:57 8477

8477 这两个选项可帮助降低控制集。但这两个选项不能与-directive同时使用,所以如果是工程模式下,可将其放置在Hook文件中(Tcl.pre或Tcl.post)。非工程模式下,可在执行完-directive之后,再次执行这两个选项;

2018-11-07 11:11:32 5995

5995

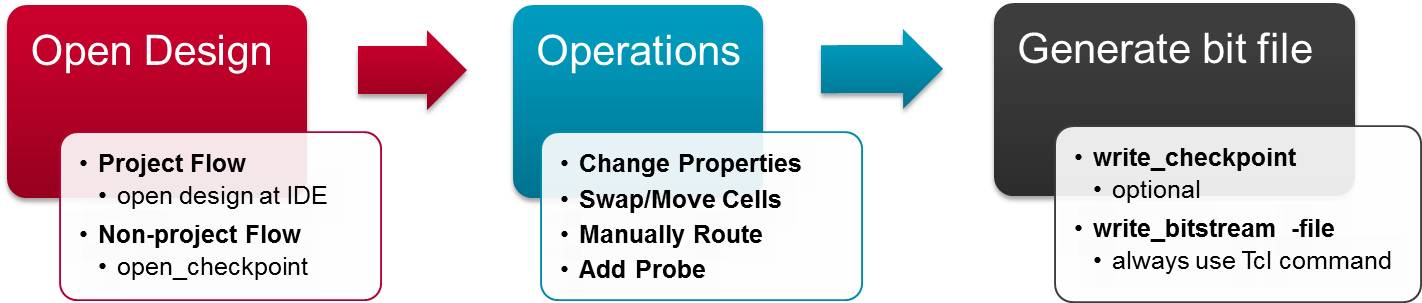

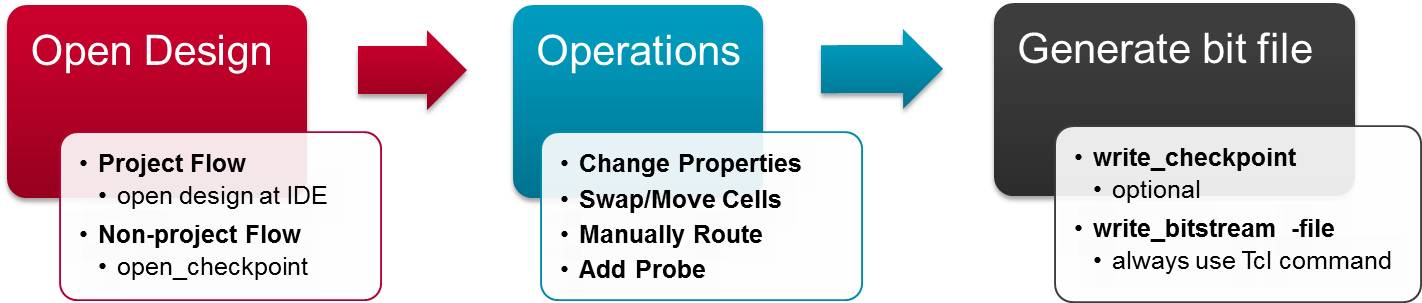

了解如何在Vivado中执行工程变更单(ECO)。

本视频将向您介绍ECO的常见用例,我们推荐的完成ECO的流程,优势和局限性,并将演示功能设计的ECO。

2018-11-21 06:40:00 5770

5770

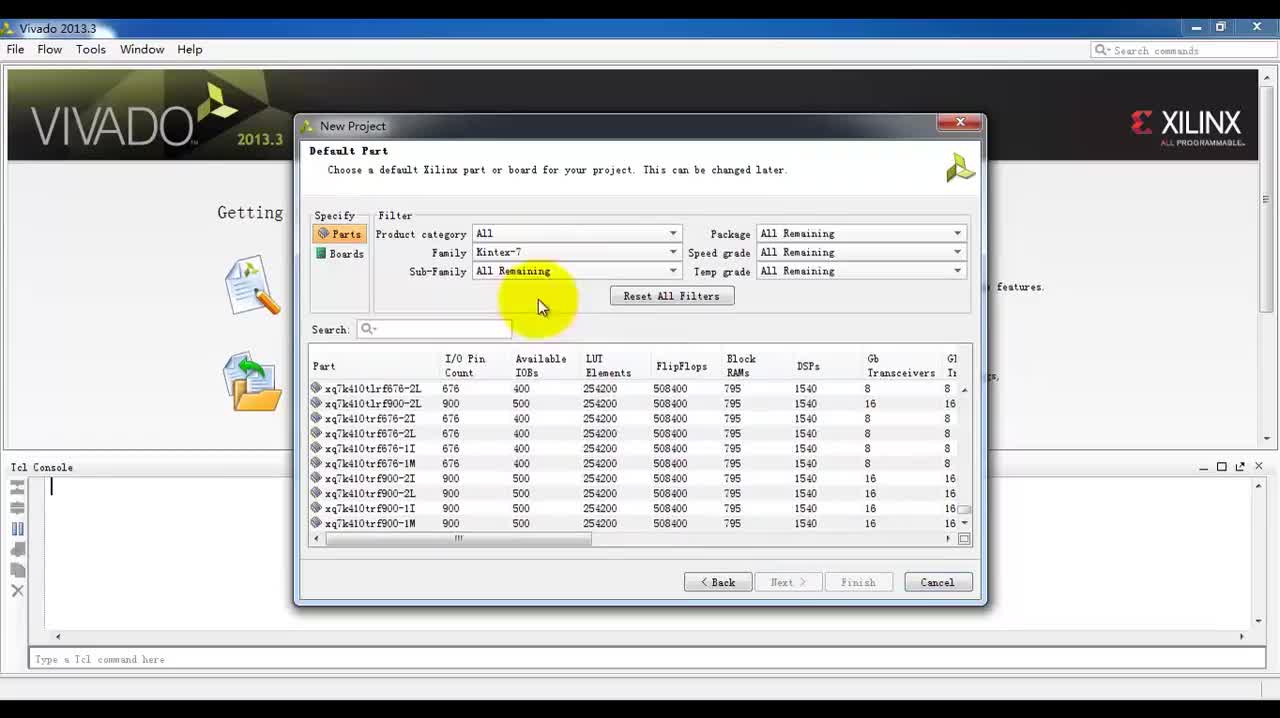

选择器件或者板卡。Parts表示器件,当然如果是板卡就点击Boards。器件可以根据系列去选,也可以直接在Search栏搜索器件型号。器件的选择根据你的FPGA芯片来定,一般在你所用的开发板手册里面可以找到。选择完毕点击Next。

2018-12-21 10:44:50 28198

28198 本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-12-05 07:06:00 2845

2845

中国大学MOOC

本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-12-04 07:05:00 1760

1760

本文档的主要内容详细介绍的是Vivado的安装生成bit文件及烧录FPGA的简要流程教程免费下载。

2019-06-18 08:00:00 25

25 第一步所指的Design通常是完全布局布线后的设计,如果是在工程模式下,可以直接在IDE中打开实现后的设计,若是仅有DCP文件,不论是工程模式或是非工程模式产生的DCP,都可以用open_checkpoint命令打开。

2019-07-25 09:27:05 3453

3453

工程模式的关键优势在于可以通过在Vivado 中创建工程的方式管理整个设计流程,包括工程文件的位置、阶段性关键报告的生成、重要数据的输出和存储等。

2019-07-24 17:30:38 5388

5388

从 Vivado 2019.1 版本开始,Vivado 综合引擎就已经可以支持增量流程了。这使用户能够在设计变化较小时减少总的综合运行时间。

2019-07-21 11:02:08 2129

2129 Tcl介绍 Vivado是Xilinx最新的FPGA设计工具,支持7系列以后的FPGA及Zynq 7000的开发。与之前的ISE设计套件相比,Vivado可以说是全新设计的。无论从界面、设置、算法

2020-11-17 17:32:26 3306

3306 Xilinx公司的FPGA中有着很多的有用且对整个工程很有益处的IP核,比如数学类的IP核,数字信号处理使用的IP核,以及存储类的IP核,本篇文章主要介绍BRAM IP核

2020-12-29 15:59:39 13270

13270 Vivado有两种工作模式:project模式和non-project模式。这两种模式都可以借助VivadoIDE或Tcl命令来运行。相比之下,VivadoIDE给project模式提供了更多的好处,而Tcl命令使得non-project模式运行起来更简单。

2020-10-21 10:58:07 4270

4270

FPGA的开发流程是遵循着ASIC的开发流程发展的,发展到目前为止,FPGA的开发流程总体按照下图进行,有些步骤可能由于其在当前项目中的条件的宽度的允许,可以免去,比如静态仿真过程,这样来达到项目

2020-10-25 10:05:37 4709

4709

本文主要介绍如何使用Vivado 开发套件创建硬件工程。

2022-02-08 10:41:59 2015

2015

本文主要介绍如何使用Vivado 开发套件创建硬件工程。

2021-02-02 07:13:32 18

18 Vivado 设计分为 Project Mode 和 Non-project Mode 两种模式,一般简单设计中,我们常用的是 Project Mode。在本手册中,我们将以一个简单的实验案例,一步一步的完成 Vivado的整个设计流程。

2021-03-22 11:39:53 51

51 Vivado 设计分为 Project Mode 和 Non-project Mode 两种模式,一般简单设计中,我们常用的是 Project Mode。在本手册中,我们将以一个简单的实验案例,一步一步的完成 Vivado的整个设计流程

2021-03-25 14:39:13 28

28 参考:UG892 UG835 Vivado集成开发工具为设计者提供了非工程模式下的FPGA设计流程。在Vivado非工程模式下,FPGA开发人员可以更加灵活地对设计过程的每个阶段进行控制,从而进一步

2021-06-19 10:52:47 3397

3397

赛灵思近日宣布推出 Vivado ML 版,这是业内首个基于机器学习(ML )优化算法以及先进的面向团队协作的设计流程打造的 FPGA EDA 工具套件,可以显著节省设计时间与成本,与目前

2021-07-02 16:40:13 3410

3410

【流水灯样例】基于 FPGA Vivado 的数字钟设计前言模拟前言Vivado 设计流程指导手册——2013.4密码:5txi模拟

2021-12-04 13:21:08 27

27 传统的FPGA开发都是通过GUI界面进行相关的“按钮”式操作,Vivado则在引入Tcl解释器后,可以通过非工程模式进行操作,一个Tcl脚本即可自动化建立工程,对工程进行分析。

2022-04-07 15:02:29 6371

6371 Vivado可以导出脚本,保存创建工程的相关命令和配置,并可以在需要的时候使用脚本重建Vivado工程。脚本通常只有KB级别大小,远远小于工程打包文件的大小,因此便于备份和版本管理。下面把前述脚本升级到Vivado 2020.2为例,讨论如何升级Vivado工程脚本。

2022-08-02 10:10:17 2471

2471 一个完整的vivado工程往往需要占用较多的磁盘资源,少说几百M,多的甚至可能达到上G,为节省硬盘资源,可以使用Tcl命令对vivado工程进行备份,然后删除不必要的工程文件,需要时再恢复即可。

2022-08-02 15:01:06 6814

6814 vivado有project模式和non-project模式,project模式就是我们常用的方式,在vivado里面新建工程,通过GUI界面去操作;non-project模式就是纯粹通过tcl来指定vivado的流程、参数。

2022-10-17 10:09:29 4603

4603 系统性的掌握技术开发以及相关要求,对个人就业以及职业发展都有着潜在的帮助,希望对大家有所帮助。本次带来Vivado系列,Vivado开发软件开发设计流程。话不多说,上货。

2023-02-21 09:16:44 5063

5063 今天推出Xilinx已发布的《Vivado使用误区与进阶》系列:用TCL定制Vivado设计实现流程。

2023-05-05 09:44:46 2068

2068

关于 Tcl 在 Vivado中的应用文章从 Tcl 的基本语法和在 Vivado 中的 应用展开,继上篇《用 Tcl 定制 Vivado 设计实现流程》介绍了如何扩展甚 至是定制 FPGA

2023-05-05 15:34:52 4104

4104

FPGA开发过程中,vivado和quartus等开发软件都会提供时序报告,以方便开发者判断自己的工程时序是否满足时序要求。

2023-06-26 15:29:05 2343

2343

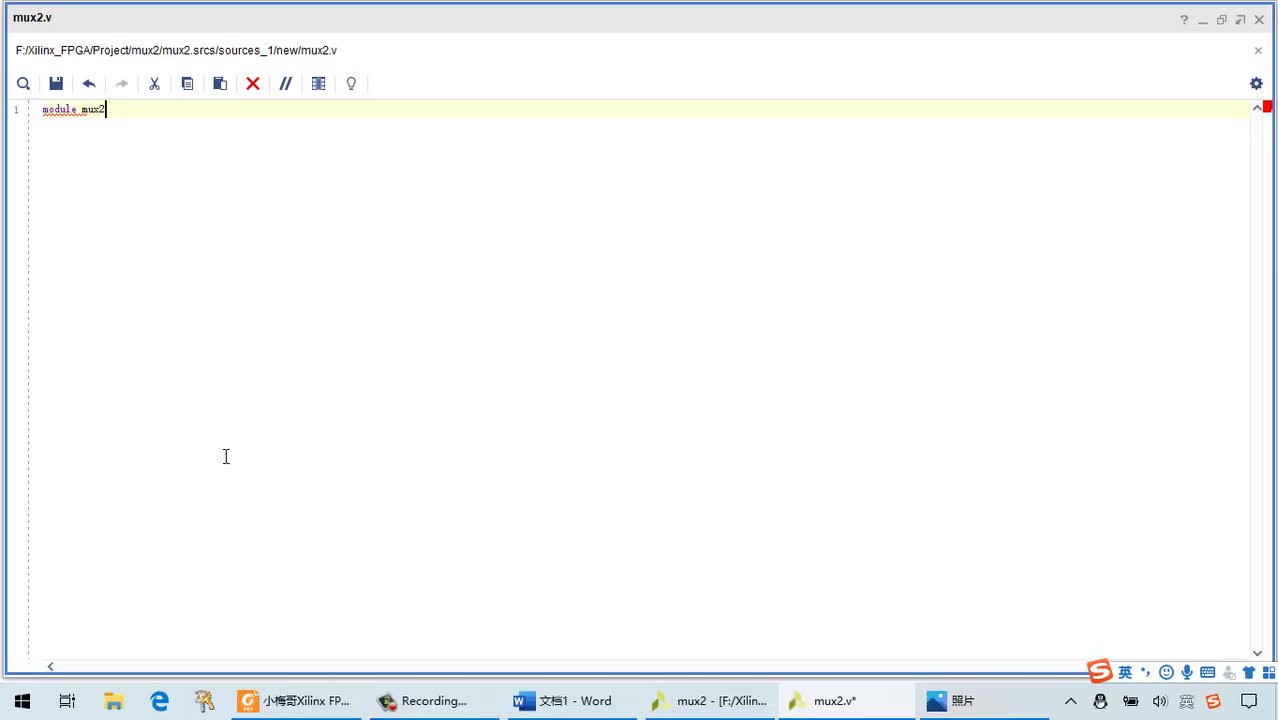

vivado的工程创建流程对于大部分初学者而言比较复杂,下面将通过这篇博客来讲解详细的vivado工程创建流程。帮助自己进行学习回顾,同时希望可以对有需要的初学者产生帮助。

2023-07-12 09:26:57 3767

3767

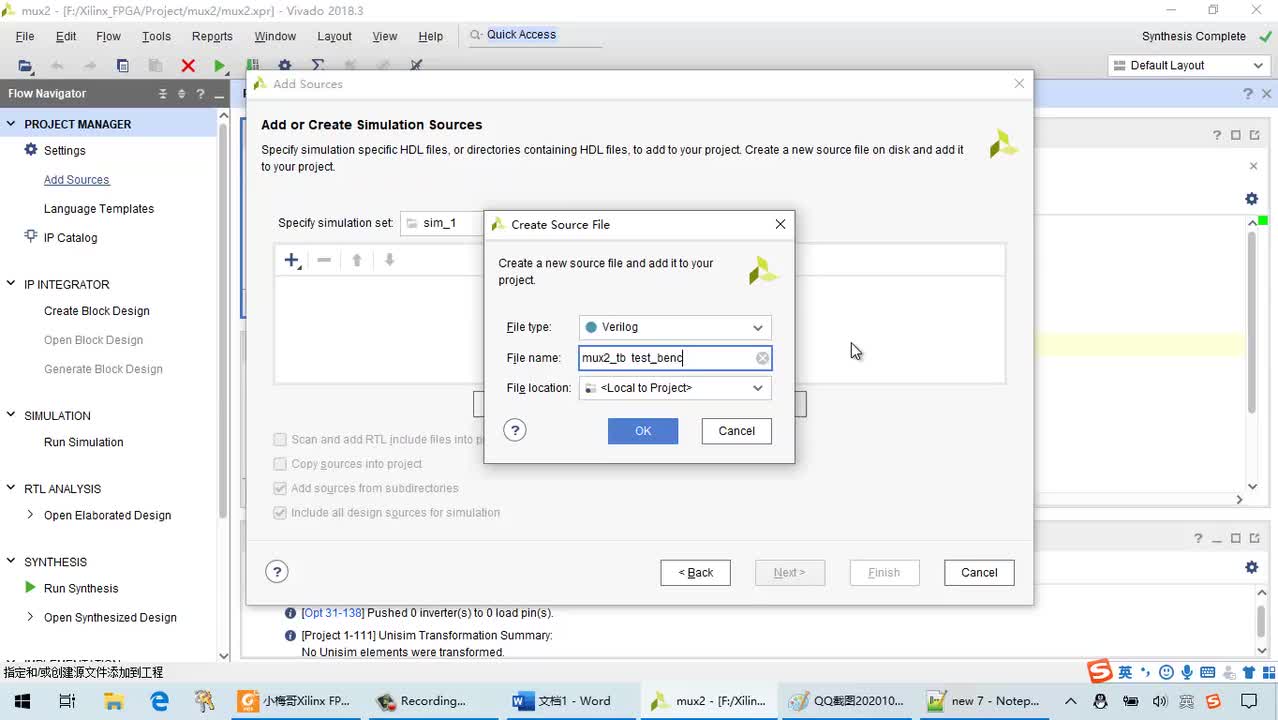

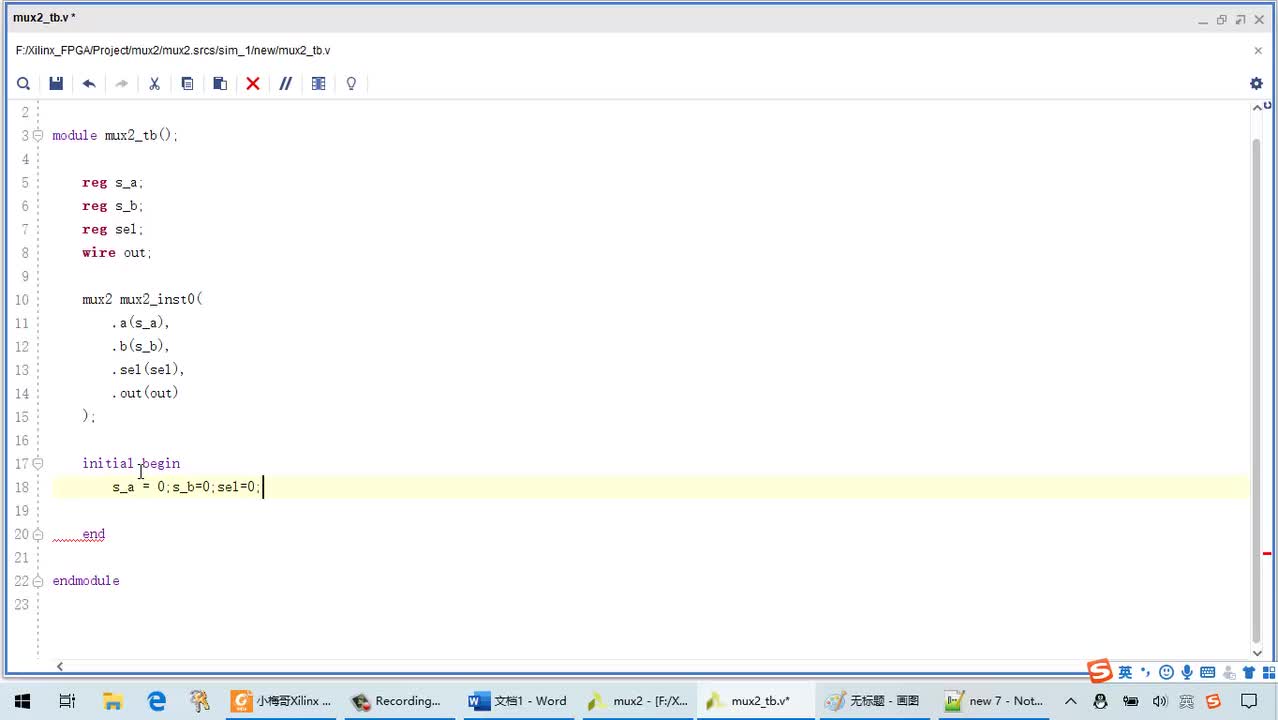

vivado开发软件自带了仿真工具,下面将介绍vivado的仿真流程,方便初学者进行仿真实验。

2023-07-18 09:06:59 6641

6641

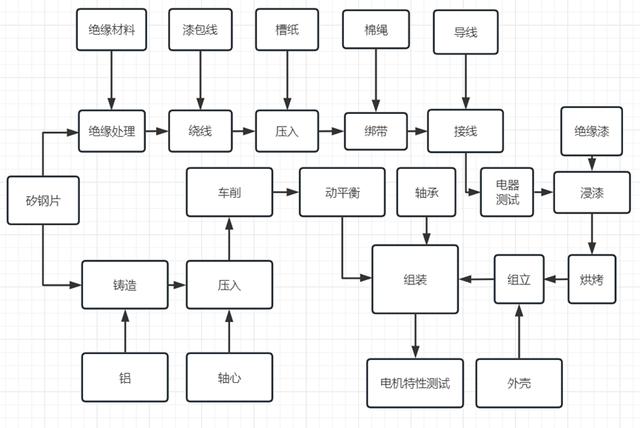

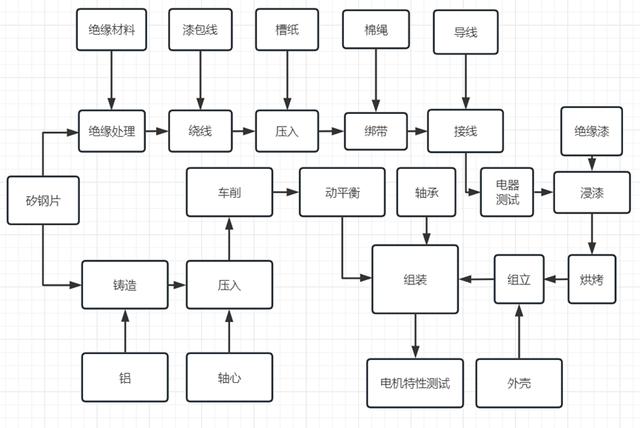

本文将深入探索感应马达的生产过程。尽管各厂商的马达细节设计有所异同,我们还是将以最基础的生产模式为主要脉络来进行阐述。

2023-08-16 16:23:30 2032

2032

电子发烧友网站提供《Vivado设计套件用户指南(设计流程概述).pdf》资料免费下载

2023-09-15 09:55:07 2

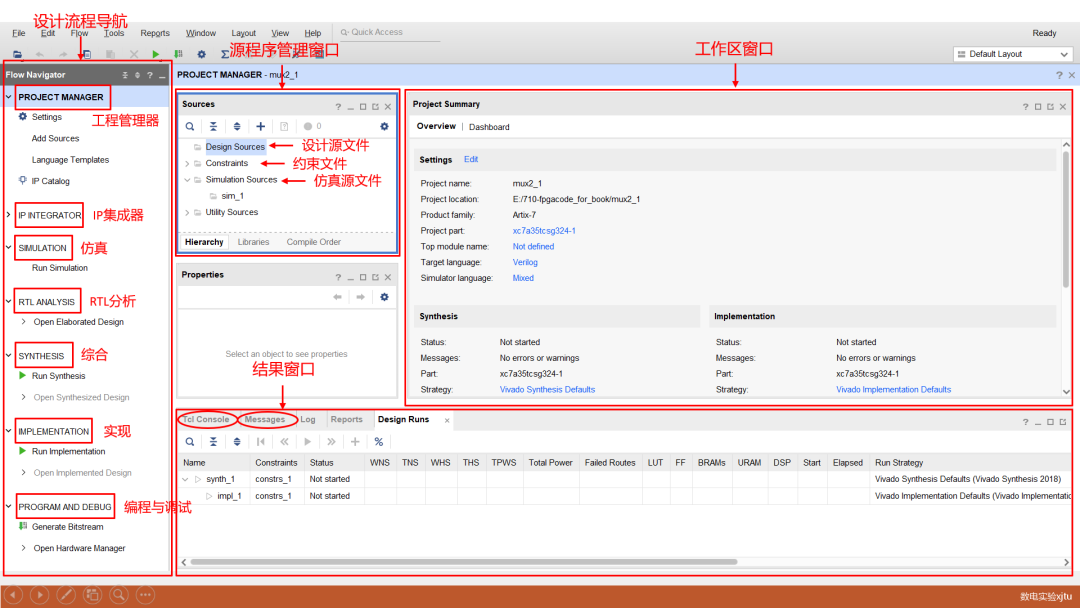

2 Vivado设计主界面,它的左边是设计流程导航窗口,是按照FPGA的设计流程设置的,只要按照导航窗口一项一项往下进行,就会完成从设计输入到最后下载到开发板上的整个设计流程。

2023-09-17 15:40:17 4711

4711

Xilinx公司的FPGA中有着很多的有用且对整个工程很有益处的IP核,比如数学类的IP核,数字信号处理使用的IP核,以及存储类的IP核,本篇文章主要介绍BRAM IP核的使用。 BRAM是FPGA

2023-12-05 15:05:02 3291

3291 将设置设计的输出路径,设置设计输出路径的步骤如下所示。 第一步:如图4.3所示,在“Vivado%”提示符后输入命令“set outputDir ./gate_Created_Data/top_output”。

2024-04-03 09:34:05 3188

3188

本文介绍了在 AMD Vivado™ Design Tool 中用工程模式使用 DFX 流程以及需要注意的地方。在使用 DFX 工程模式的过程中要把具体步骤映射到相应的 DFX 非工程模式的步骤,这样才能更好地理解整个流程的运行逻辑。

2024-04-17 09:28:23 2280

2280

电子发烧友App

电子发烧友App

评论