赛灵思近日宣布推出 Vivado ML 版,这是业内首个基于机器学习(ML )优化算法以及先进的面向团队协作的设计流程打造的 FPGA EDA 工具套件,可以显著节省设计时间与成本,与目前的 Vivado HLx 版本相比,Vivado ML 版将复杂设计的编译时间缩短了 5 倍,同时还提供了突破性的平均达 10% 的结果质量( QoR )提升。

Vivado ML 概述

1、基于 ML 的设计优化

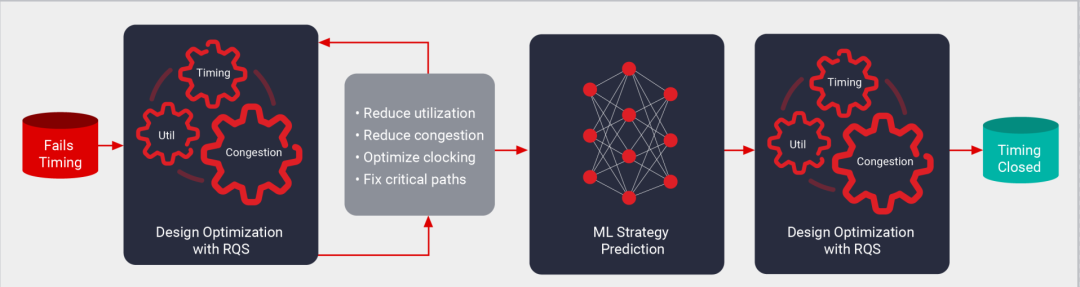

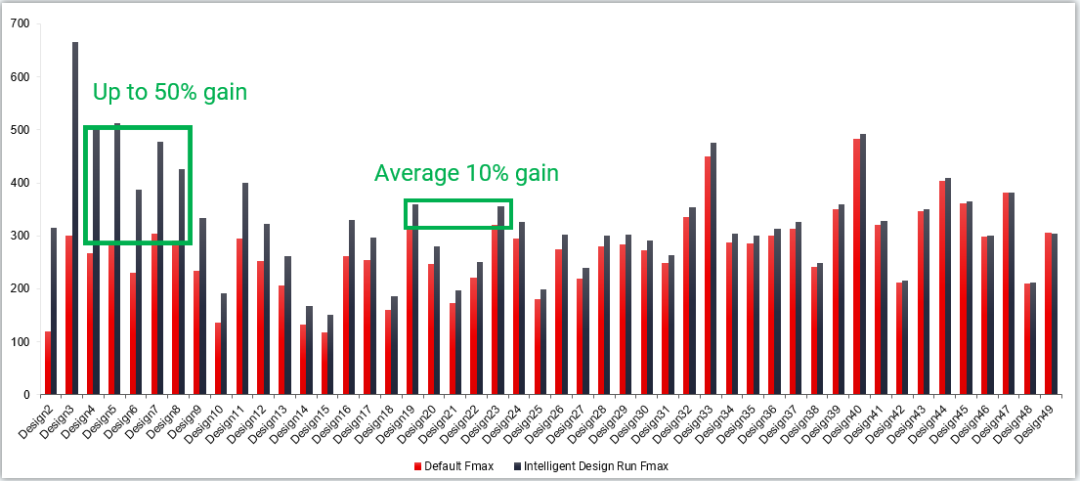

加速设计收敛

与当前的 Vivado HLx 版本相比,全新w Vivado ML 版本在复杂设计上实现了高达 50%(平均 10%)的突破性结果质量 (QoR) 提升。

基于 ML 的逻辑优化、拥塞估计、延迟估计和智能设计运行等新功能和算法有助于自动化策略以减少时序收敛迭代。

2、协同设计环境

提升生产力

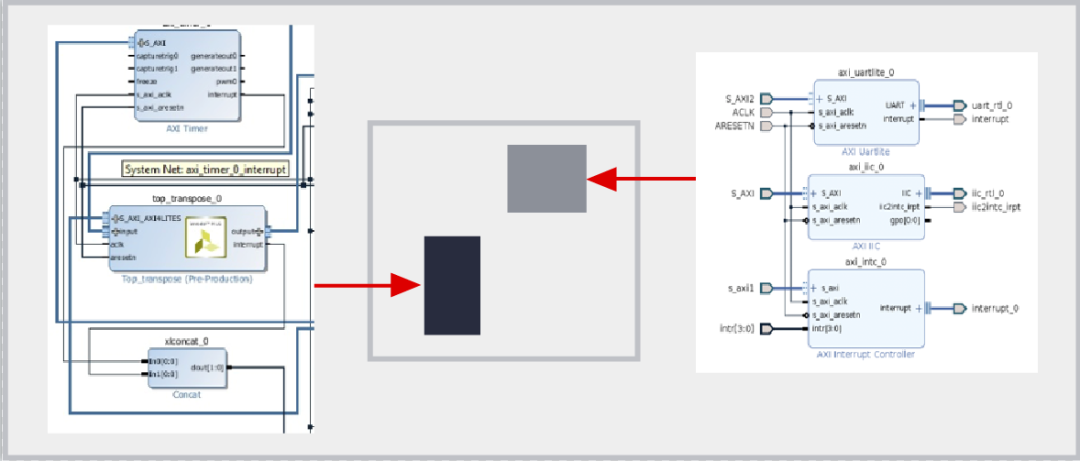

使用 Vivado IP Integrator 改进协作设计,使用全新的“块设计容器”功能实现模块化设计。

推广基于团队的设计方法,并允许采用分而治之的策略来处理具有多站点协作的大型设计。

3、全新高级 DFX 功能

编译时间减少

Xilinx 引入了抽象 Shell 的概念,允许用户在系统中定义多个模块以进行增量和并行编译。

与传统的完整系统编译相比,此功能可将平均编译时间缩短 5 倍,最多可缩短 17 倍。

Abstract Shell 通过将设计细节隐藏在模块之外来帮助保护客户的 IP

功能介绍

1、高层次设计

Vivado IP Integrator 可提供基于 Tcl、设计期正确的图形化设计开发流程。设计团队在接口层面上工作,能快速组装复杂系统,充分利用 Vitis HLS、Vitis Model Composer、Xilinx IP、联盟成员 IP 和自己的 IP。通过利用全新提升的 Vivado IPI 和 HLS 的完美组合,客户能将开发成本相对于采用 RTL 方式而言节约高达 15 倍。

2、验证

应对当前复杂器件的验证挑战,需要在各种设计层面上应用大量工具及技术。Vivado 设计套件在紧密结合的环境中提供这些工具和技术,从而可加速模块及芯片级设计的验证。

3、实现

具有高级机器学习算法的 Vivado ML 设计套件提供了在运行时和性能方面具有显着优势的最佳实现工具。凭借用于综合、布局、布线和物理优化的一流编译工具以及 Xilinx 编译方法建议,设计者可以加快设计周期的实现阶段。

平台版本

Vivado ML 标准版

Vivado ML 的器件受限免费版本。

Vivado ML 企业版

包括对所有 Xilinx 器件的支持。

文章出处:【微信公众号:FPGA开发圈】

责任编辑:gt

-

FPGA

+关注

关注

1655文章

22287浏览量

630326 -

赛灵思

+关注

关注

33文章

1797浏览量

133151 -

机器学习

+关注

关注

66文章

8541浏览量

136236

原文标题:Vivado ML 版,让设计更智能化

文章出处:【微信号:FPGA-EETrend,微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

强强联合进军万亿晶振市场,赛思电子与一晶科技成立合资公司

【精选直播】openDACS2025开源EDA与芯片赛宣讲 赛题一:网表评估和优化

易灵思与思特威第二届机器视觉方案大会圆满收官

睿思芯科灵羽处理器获得国家级权威认可

创“芯”舞台!思尔芯邀您挑战2025 EDA精英赛

授时系统厂家,授时系统哪家好?赛思高精度授时系统助力华福证券授时服务新升级!

赛思快讯 | 嘉兴市委书记陈伟一行莅临赛思调研

易灵思2025 FPGA技术研讨会北京站圆满结束

国产EDA亿灵思®接入DeepSeek

赛灵思低温失效的原因,有没有别的方法或者一些见解?

EDA精英挑战赛赛果公布!思尔芯“战队”薪火相承斩获“麒麟杯”

赛灵思Vivado ML版优化应用设计

赛灵思Vivado ML版优化应用设计

评论