vivado开发软件自带了仿真工具,下面将介绍vivado的仿真流程,方便初学者进行仿真实验。

1、前期准备工作

在上一篇博客中我们已经详细介绍了vivado建立工程的流程,有需要的朋友可以移步https://www.elecfans.com/d/2179253.html进行查看;本次我们在建立的工程基础上进行仿真文件的添加和仿真演示。

2、添加仿真文件

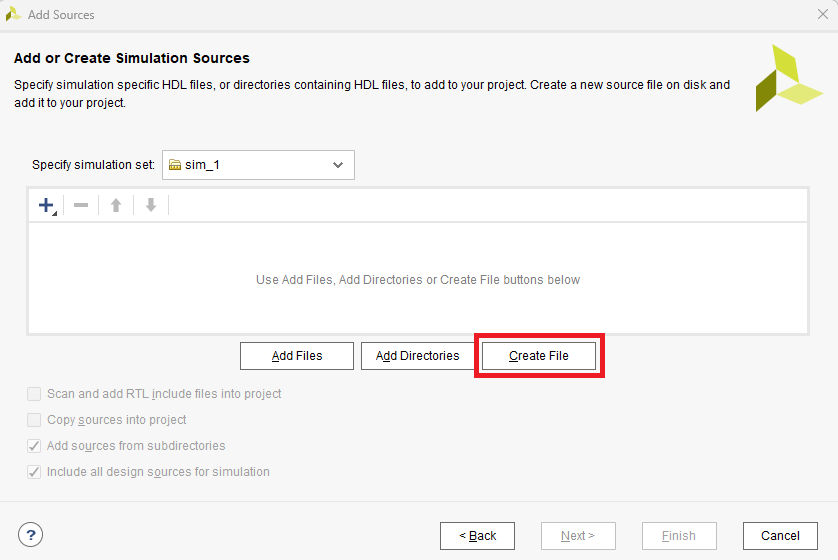

第一步点击Add Sources添加仿真文件,具体步骤如下:

接下来点击Add or create simulation sources,再点击Next

点击Create File创建文件

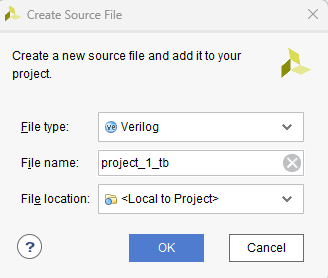

一般将其命名为文件名_tb,其中tb为testbench的缩写,一般为仿真测试文件,再点击OK

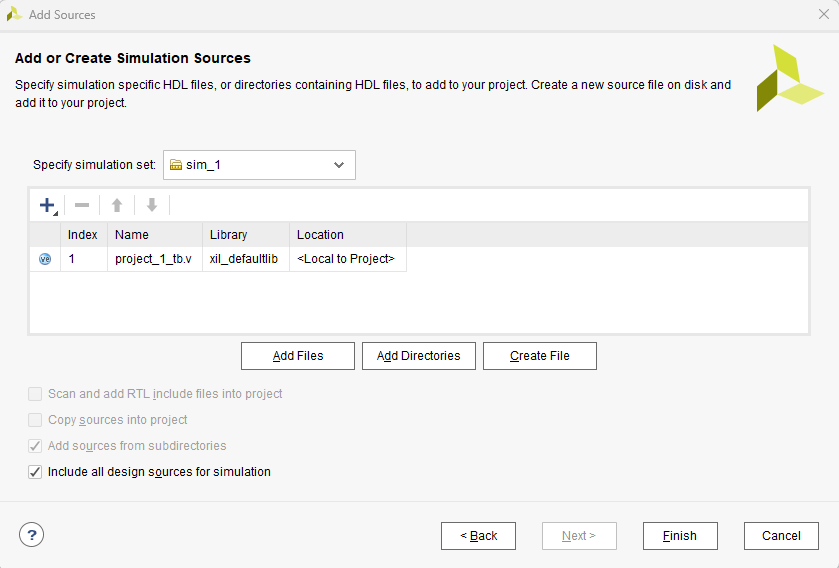

最后点击Finish完成文件创建

3、编写仿真文件代码

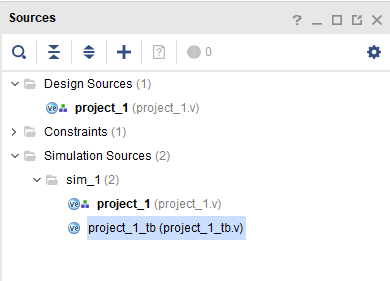

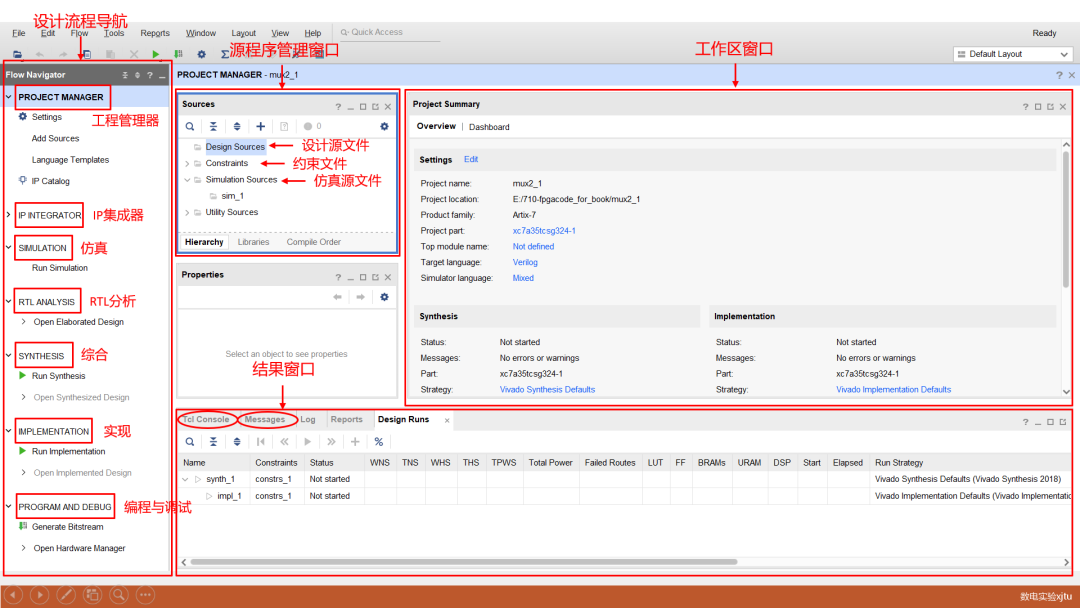

之后在sim_1文件夹下可以找到创建的文件

在上述部分完成仿真代码的编写之后点击保存按钮

4、进行仿真设置

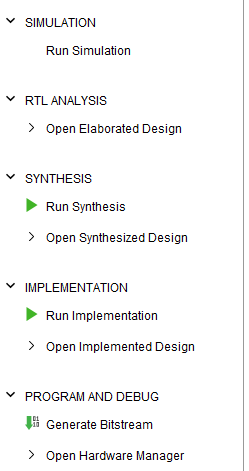

鼠标右键点击SIMULATION,之后再点击Simulation Settings

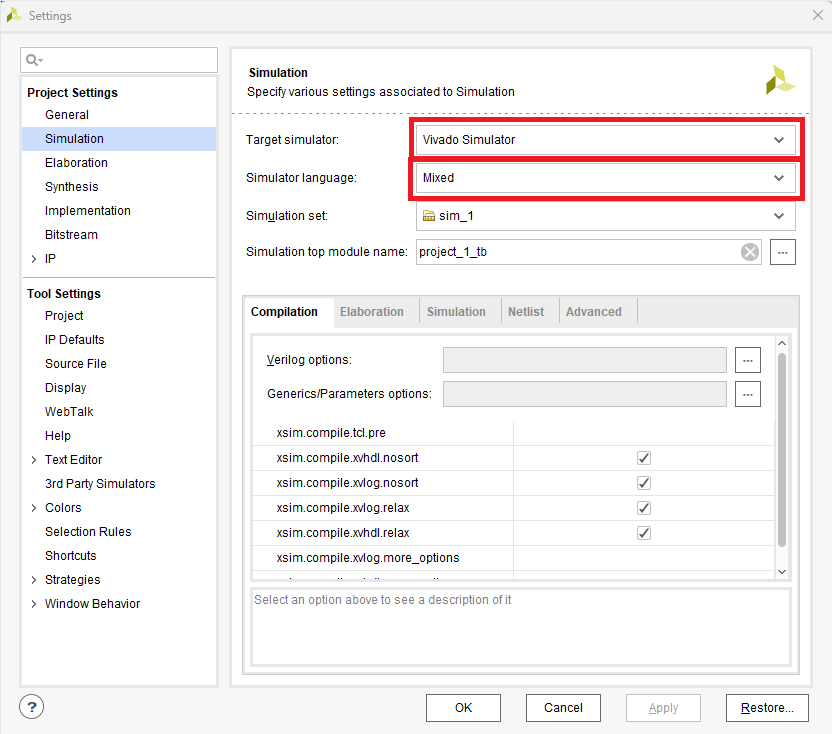

上方红框为仿真软件,我们选择Vivado Simulator也即vivado自带的仿真软件;下方为仿真语言类型我们选择Mixed也即混合型

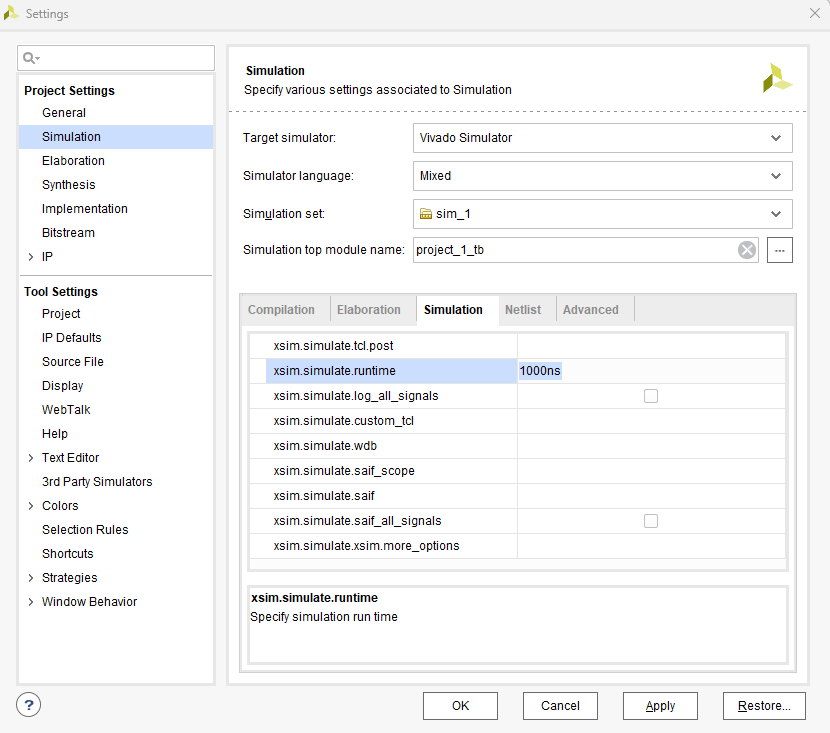

在Simulation中所示位置可以调节仿真的步进时长,此处设置为10ms;之后点击OK完成设置

5、功能仿真

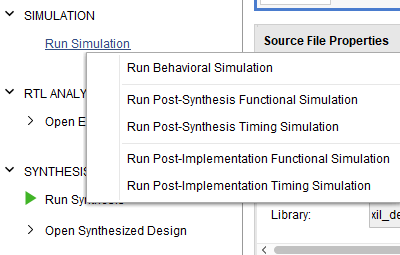

点击Run Simulation 之后点击第一个Run Behavioral Simulation 进行功能仿真

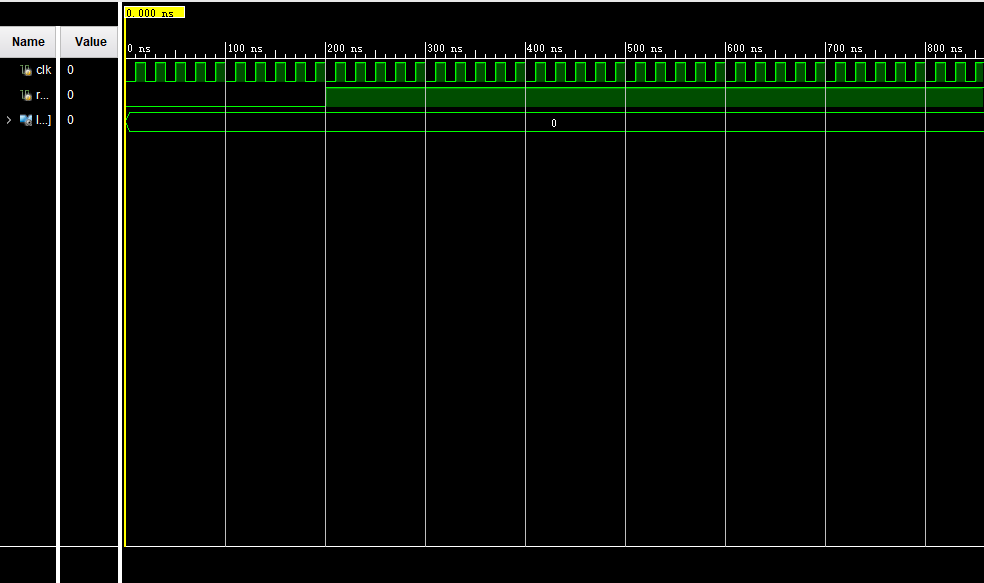

运行结束后即可查看仿真结果并且进行相应的调节观察仿真波形图

-

仿真

+关注

关注

53文章

4407浏览量

137671 -

文件

+关注

关注

1文章

587浏览量

25917 -

开发软件

+关注

关注

1文章

25浏览量

13308 -

Vivado

+关注

关注

19文章

846浏览量

70476

发布评论请先 登录

FPGA开发Vivado的仿真设计案例分析

基于microblaze的vivado开发流程

Vivado设计之Tcl定制化的实现流程

Vivado综合引擎的增量综合流程

Vivado设计流程指导手册

Vivado设计流程指导说明

Vivado调用Questa Sim或ModelSim仿真小技巧

Xilinx FPGA Vivado开发流程介绍

vivado主界面及设计流程

vivado仿真流程

vivado仿真流程

评论