系统性的掌握技术开发以及相关要求,对个人就业以及职业发展都有着潜在的帮助,希望对大家有所帮助。本次带来Vivado系列,Vivado开发软件开发设计流程。话不多说,上货。

Xilinx FPGAVivado 开发流程

作者:李西锐校对:陆辉

在做任何设计之前,我们都少不了一个工作,那就是新建工程,我们设计的一些操作,必须在工程下完成,那么接下来就向大家介绍一下新建工程的步骤。那么我以简单的二输入与门为例向大家介绍一下操作步骤。

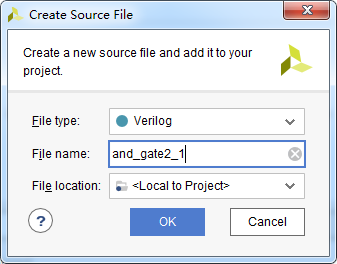

在后续的开发设计中,我们会做各种各样的设计。每个设计都有自己的名字,在上述文件内,用实验的名字命名一个文件夹。名字的话一定要带有某种含义,不建议随便给个字母序列当做名字。例如:第一个要做的二输入与门的设计,命名为and_gate2_1。

做好设计前准备后,我们开始新建工程。

* 新建工程

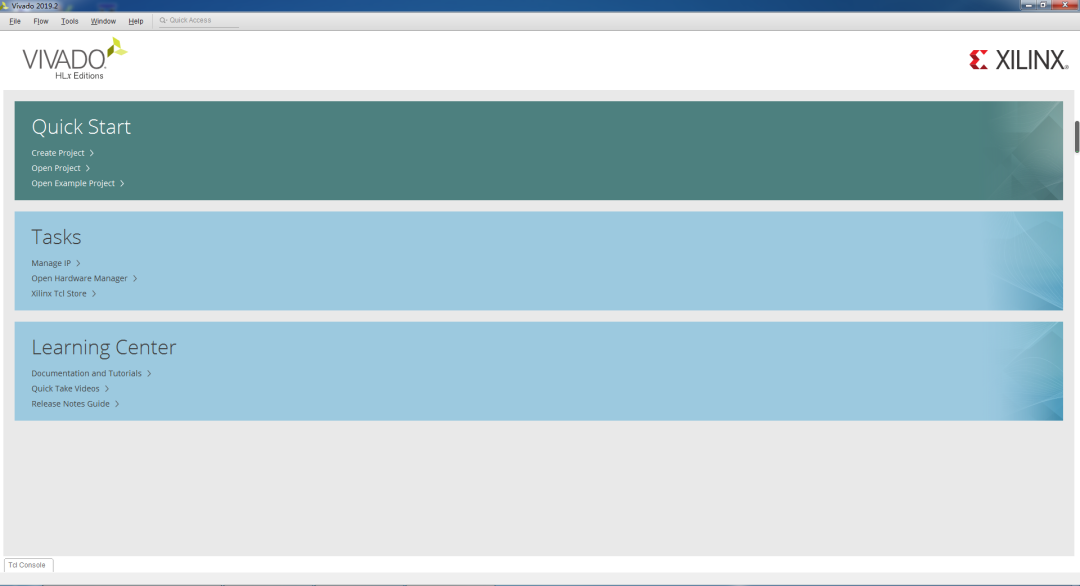

双击打开Vivado。

在Quick Start中,我们选择Creat Project。打开新建工程向导,如下:

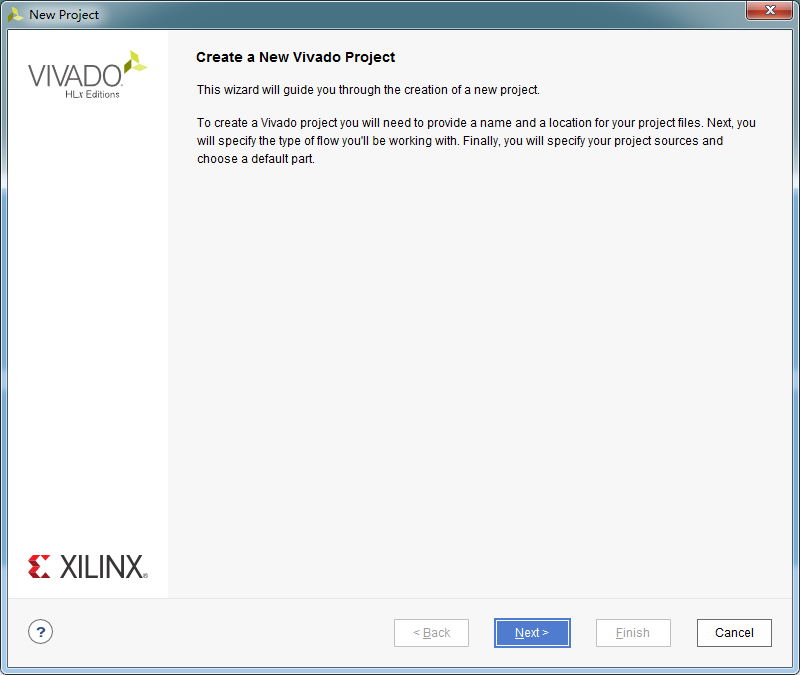

此界面为新建工程引导,此步骤没有可以设置的内容,所以直接点击NEXT。

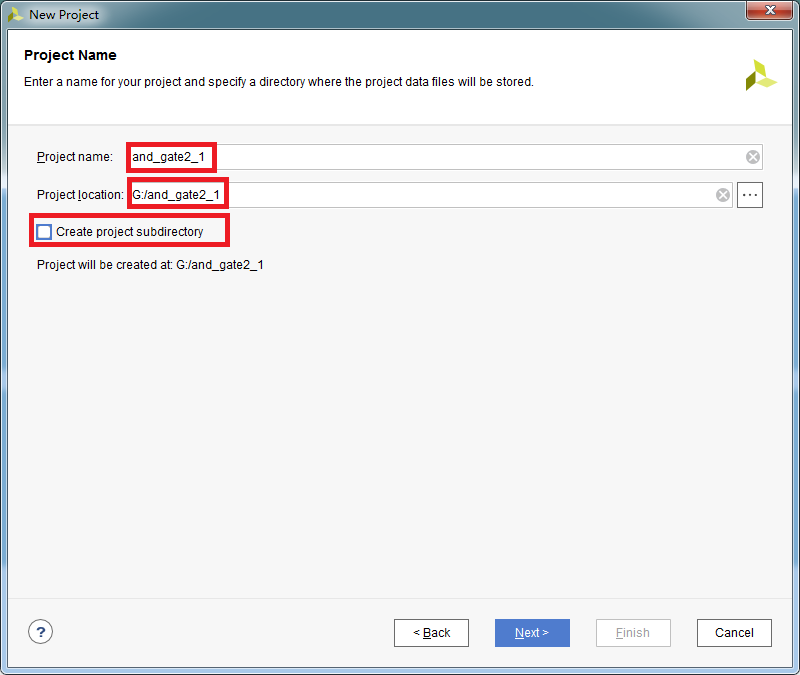

在此界面,我们第一步,需要给我们的工程起一个名字,在此我们起名为and_gate2_1。在第二步设置工程存放路径,要求无中文路径。第三步,如果你指定路径位置没有对应的and_gate2_1文件夹,那么我们就可以勾选上,软件会自动帮我们新建。由于我已经新建过了文件夹,所以此处我没有勾选此选项。设置好之后,点击NEXT。

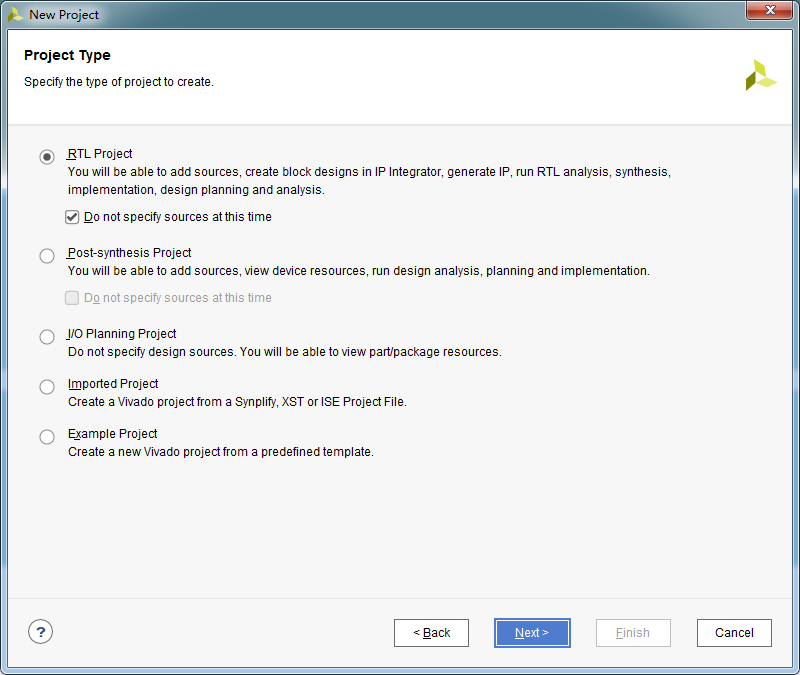

此界面我们设置工程类型,选择RTL Project。在这个选项下面,还有另外的一个选项。这个是让我们选择是否创建源文件。图示中选择不新建,在建完工程之后我们在新建源文件。继续点击NEXT。

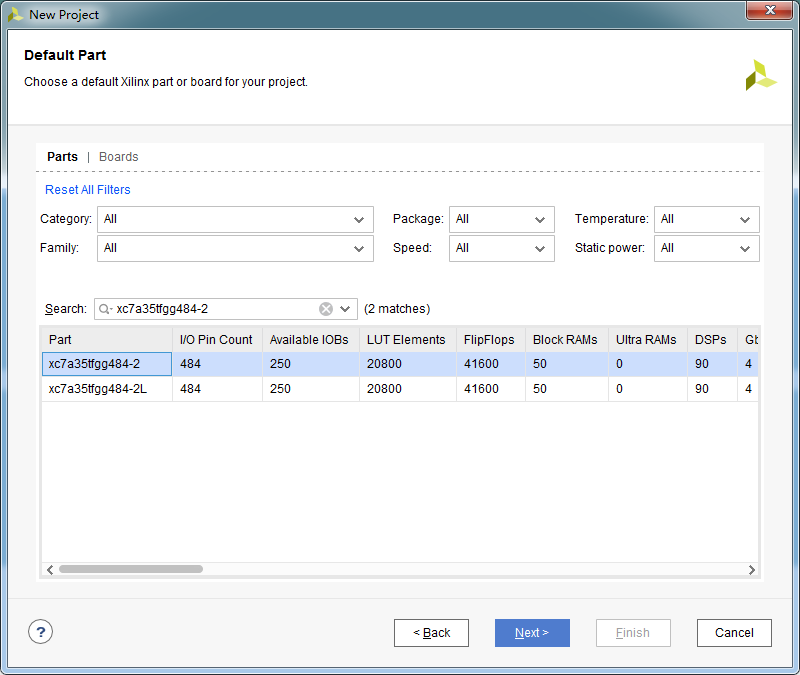

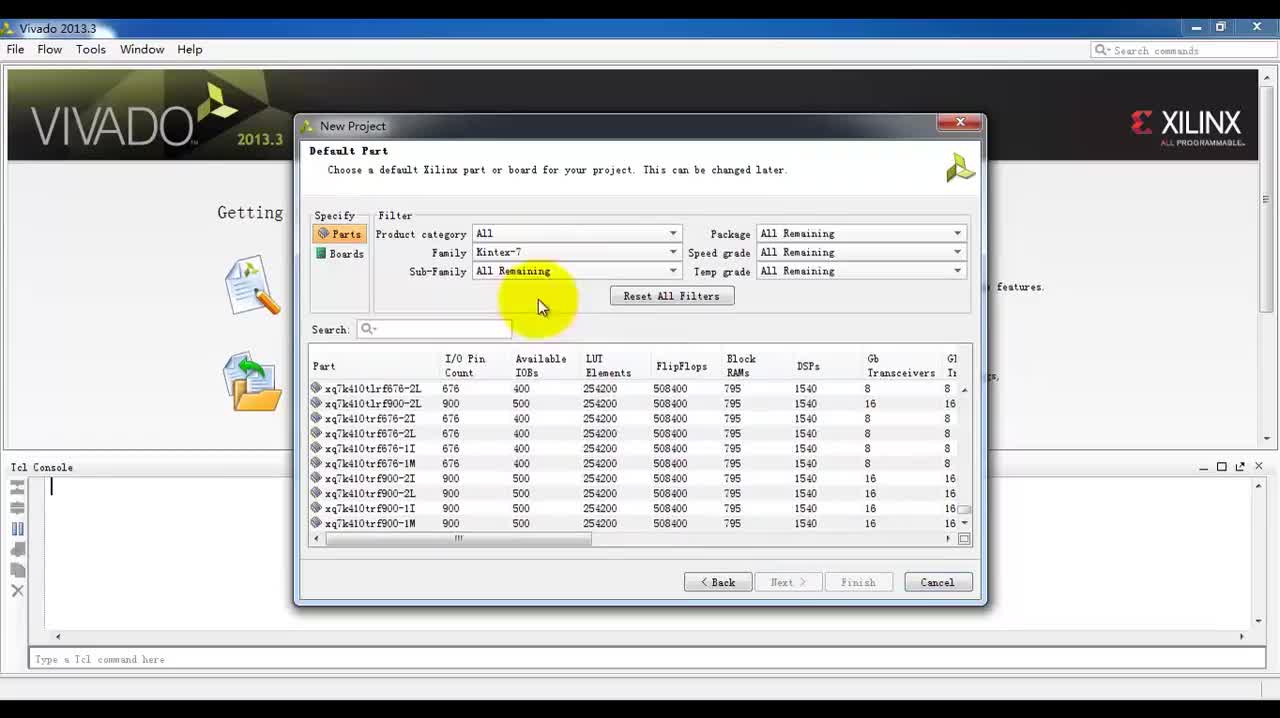

在这个步骤里面,我们选择对应开发板的芯片型号。我以SANXIN-B04为例,芯片型号为XC7A35TFGG484-2。可以在搜索框里直接输入,在下面的选项里面我们选择第一个,如图所示。选中之后点击NEXT。

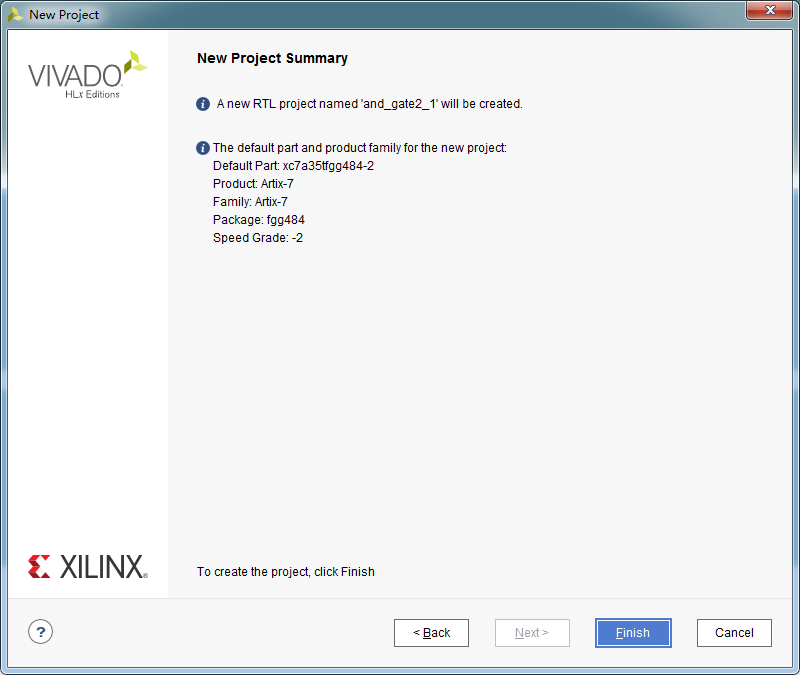

最后一步,为工程的信息展示。确认信息无误后,点击Finish。至此,我们的工程就新建完成了。

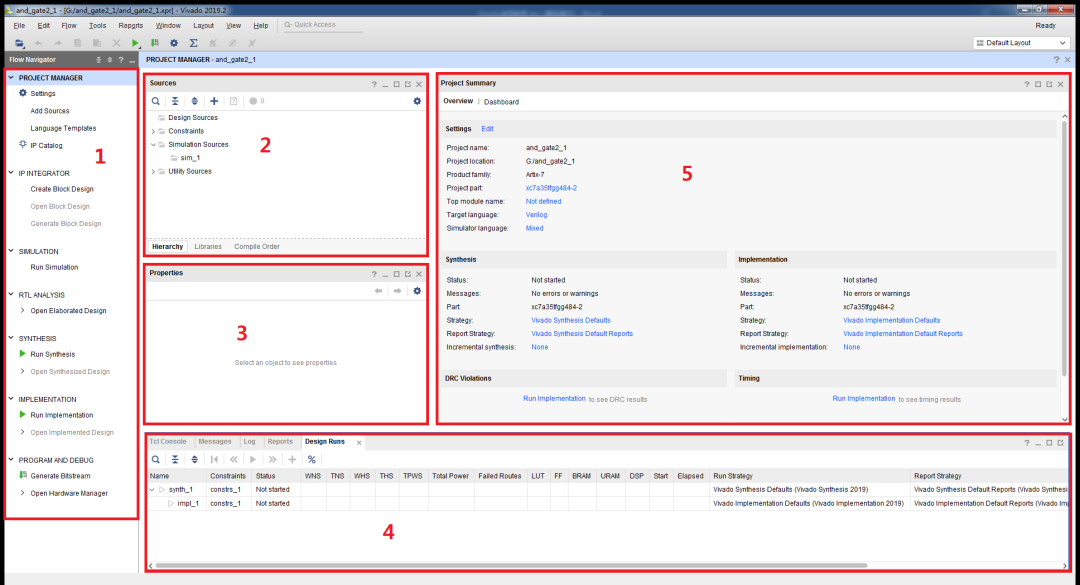

我们把整个界面分为5个区域,如上图所示。

1、菜单;

软件的常用功能全在此区域,方便我们进行后续操作。每一项的作用,会在后续的讲解中为大家介绍。

2、源文件;

新建文件可以在此区域,在这个窗口下面,有三个选项,我们在第一个选项中可以看到代码文件的层次结构。

3、属性;

窗口会显示所选内容的具体信息

4、信息;

展示任务进度,编译信息等内容。

5、报告;

展示工程信息以及状态。此外编写代码也是在此区域。

通过以上的介绍,我们明白了各个区域的作用,接下来我们就新建文件开始编写代码:

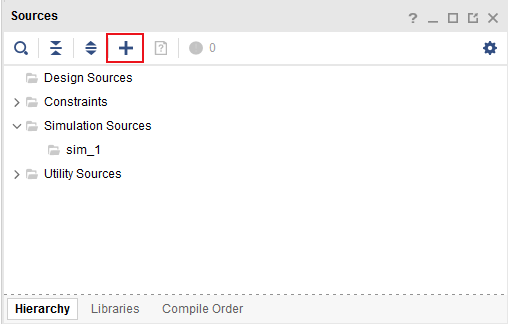

在源文件窗口,点击+号。如下图:

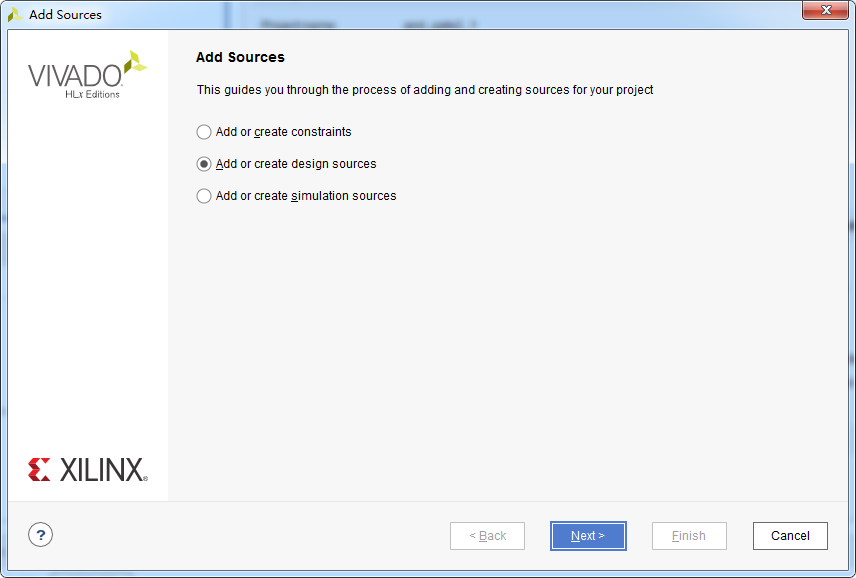

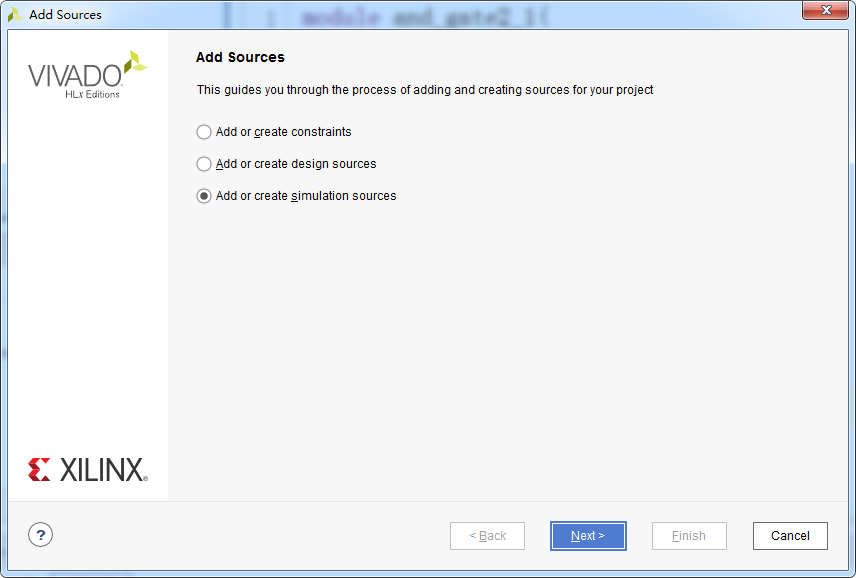

三个选项,第一个是添加或者新建管脚约束文件,第二个是添加或者新建源文件,第三个是添加或者新建仿真文件。那么我们选择第二个选项。

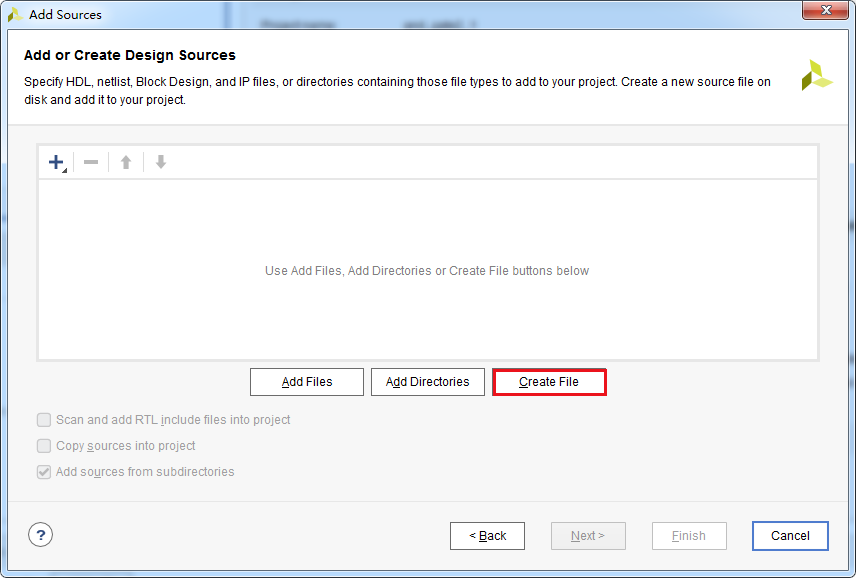

选择好之后,点击NEXT。然后按照上图中所示,点击Creat File;

在File name一项中,填入文件名,其他保持默认,然后点击OK,再点击Finish。

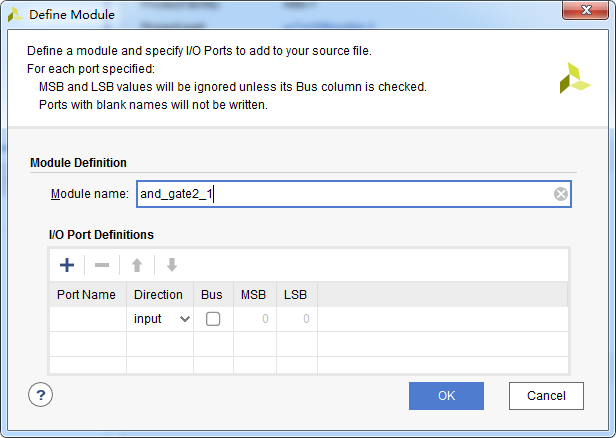

此界面我们可以提前填入端口,选择好端口方向以及位宽。然后软件就可以帮我们写好代码的端口定义部分。如果不需要可以直接点击OK。

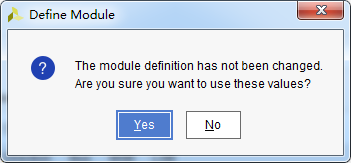

再点击YES。

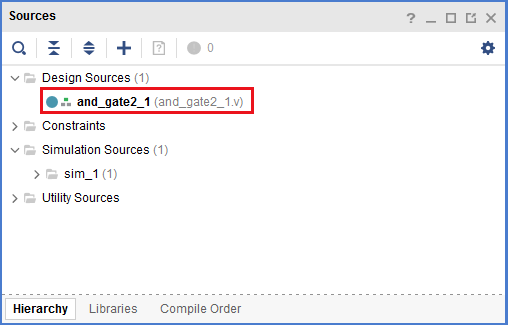

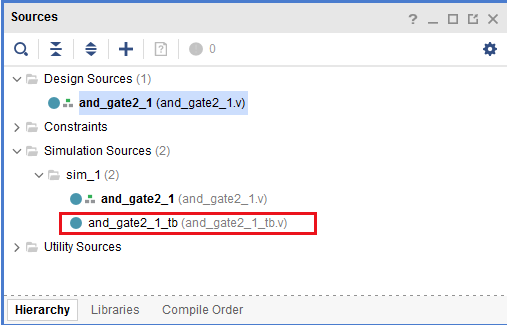

新建好之后,会出现如下图:

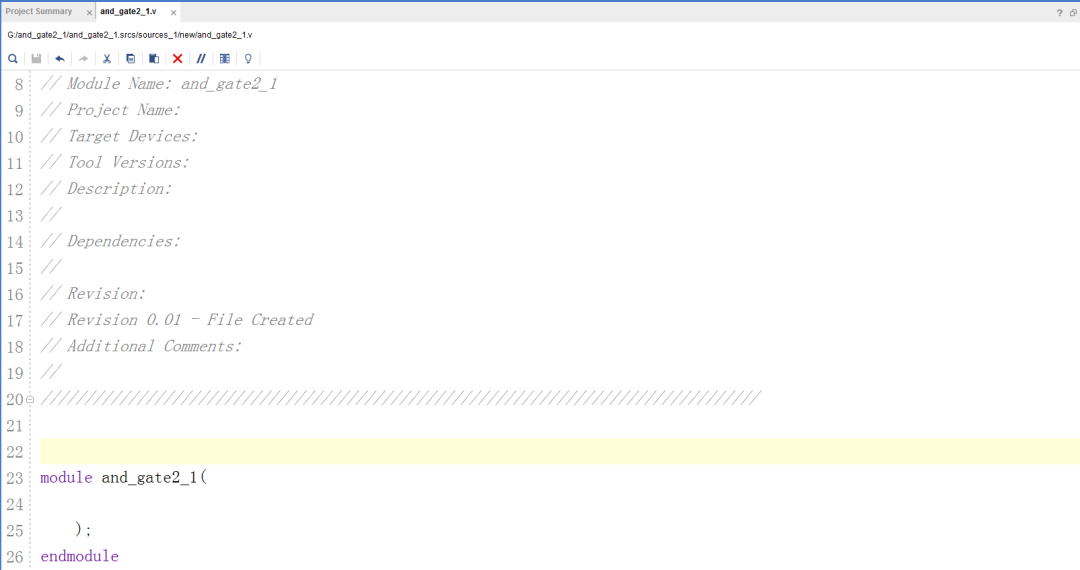

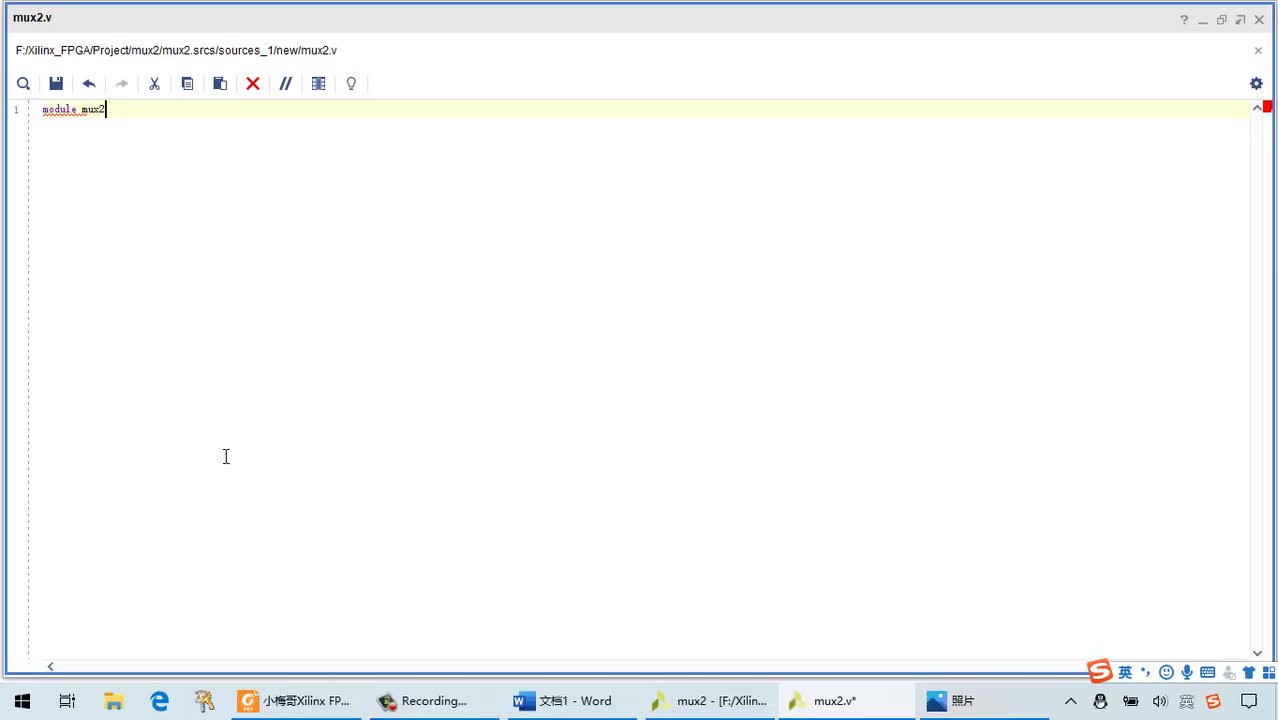

在Design Sources中,可以看到我们新建的文件。双击打开开始写代码。自动生成的代码如下:

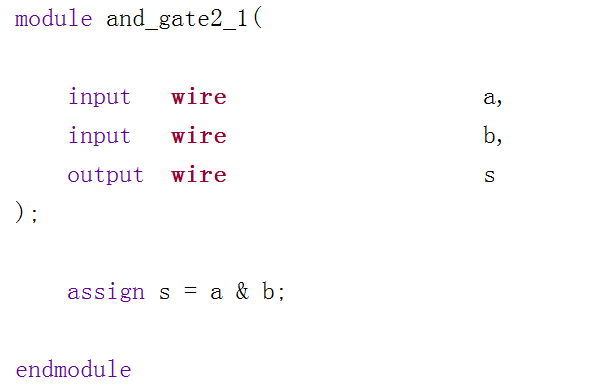

为了更好的向大家展示,我将代码文件中的注释先删除掉。代码如下:

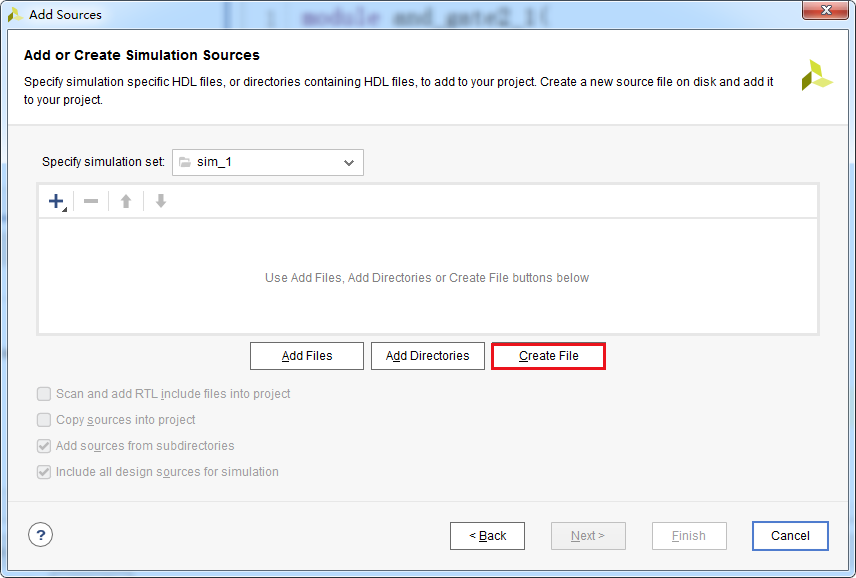

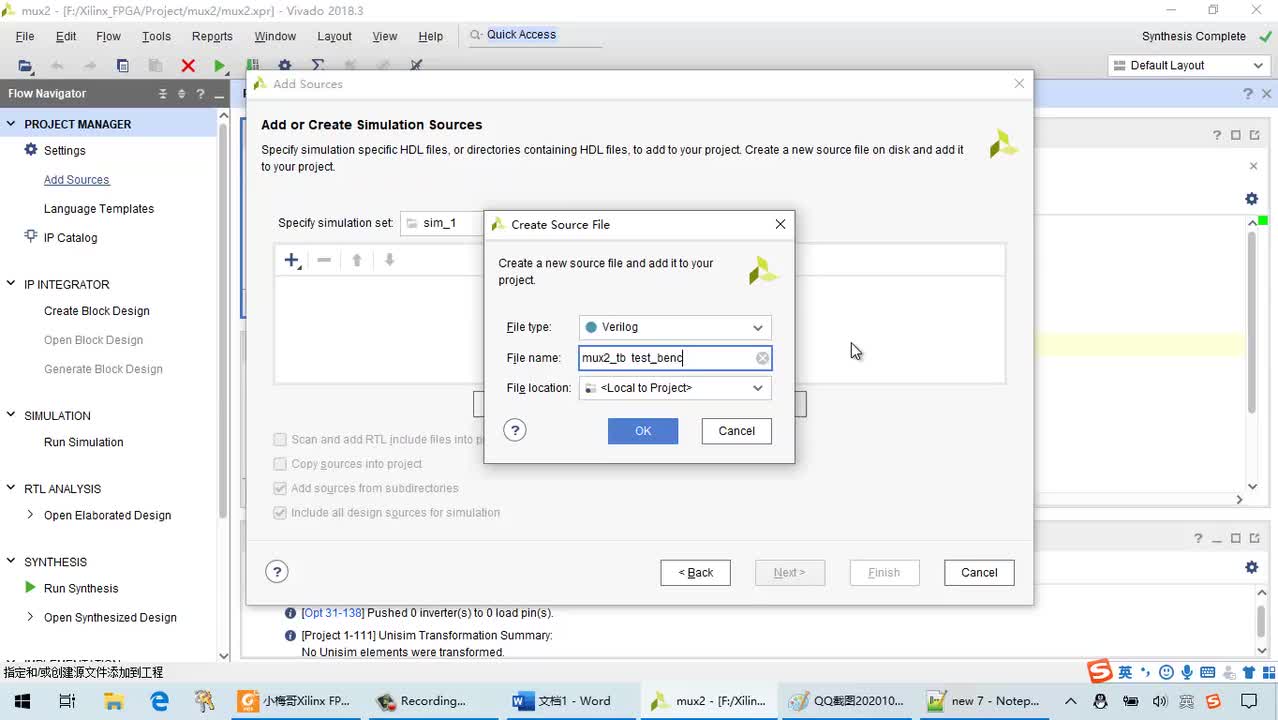

为了验证代码的正确性,还需要写测试文件进行仿真测试。仍然点击+号新建文件,只不过这次我们选择第三个选项:

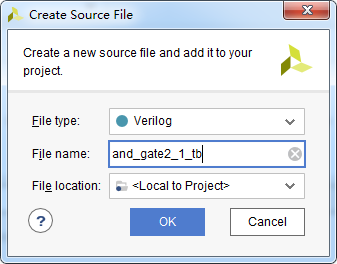

点击NEXT;选择Creat File:

点击OK,点击Finish。定义端口界面直接跳过,因为我们的仿真文件没有端口。

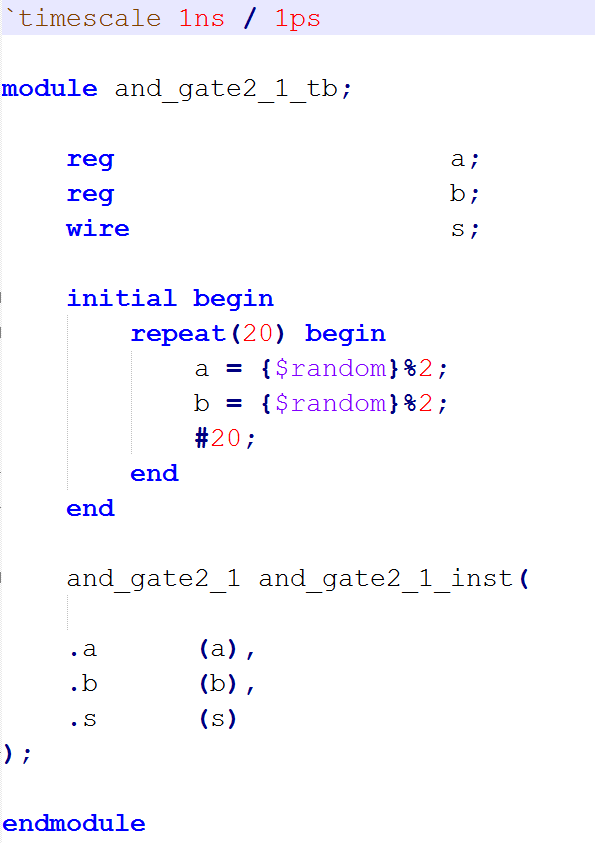

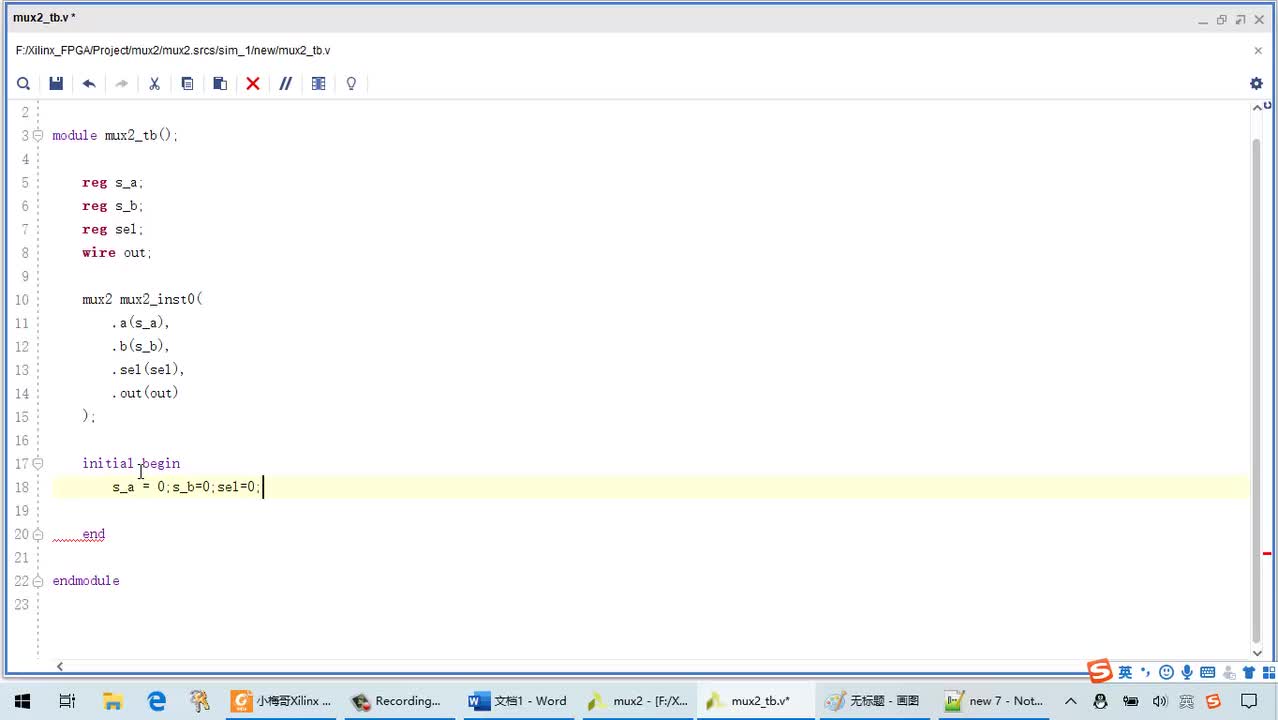

新建好之后,按照上图所示,双击打开文件。代码如下:

我们可以使用随机数来产生我们需要的输入,代码写完之后,我们可以直接打开仿真。

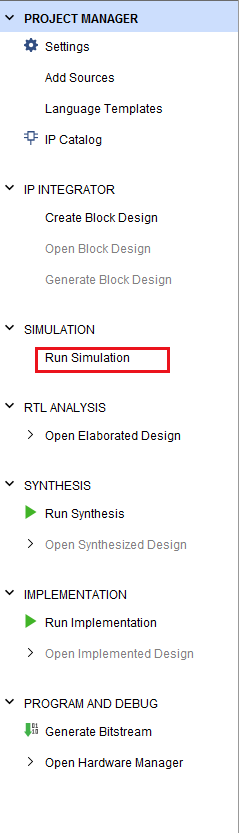

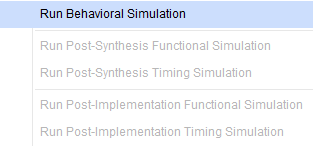

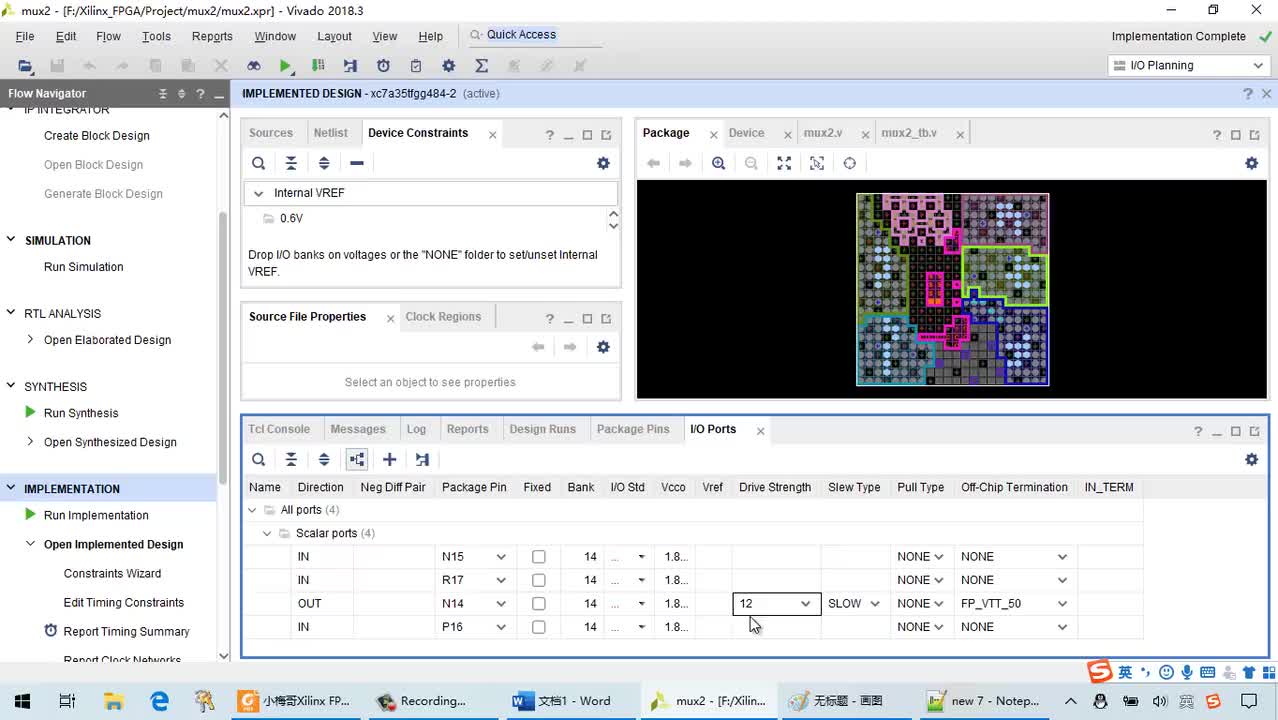

点击如图所示的选项,打开软件的仿真器。

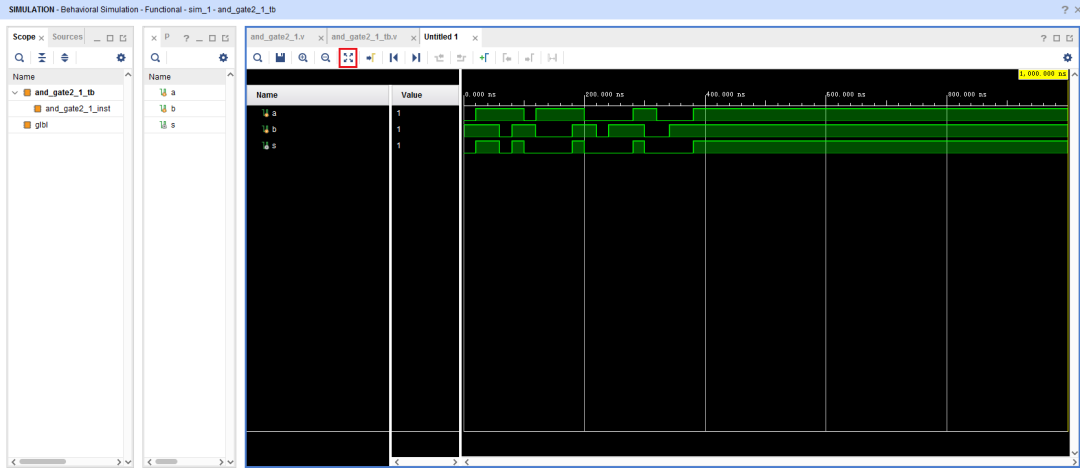

仿真图打开后,我们点击如图所示的按钮,可以看到全部波形。在仿真图中,我们可以看到后半部分波形没有变化,这是因为我们随机数生成了20组,每组20ns,所以总时长为400ns。但是仿真软件是默认运行1us的,所以就看到了如图所示的情况,在此,大家可以随意生成随机数的个数。我们验证仿真时,只需要看前400ns的波形就可以了。按照波形显示,我们可以验证到波形输出与与门真值表相同,所以最终结果是正确的。至于下板验证后续再出相关文章说明。

-

FPGA

+关注

关注

1655文章

22283浏览量

630186 -

Xilinx

+关注

关注

73文章

2192浏览量

129915 -

Quick

+关注

关注

0文章

17浏览量

12671 -

开发软件

+关注

关注

1文章

25浏览量

13308 -

Vivado

+关注

关注

19文章

846浏览量

70466

原文标题:Xilinx FPGA Vivado 开发流程

文章出处:【微信号:HXSLH1010101010,微信公众号:FPGA技术江湖】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Xilinx FPGA Vivado开发流程介绍

Xilinx FPGA Vivado开发流程介绍

评论