在给FPGA做逻辑综合和布局布线时,需要在工具中设定时序的约束。通常,在FPGA设计工具中都FPGA中包含有4种路径:从输入端口到寄存器,从寄存器到寄存器,从寄存器到输出,从输入到输出的纯组合逻辑

2023-10-12 12:00:02 2179

2179

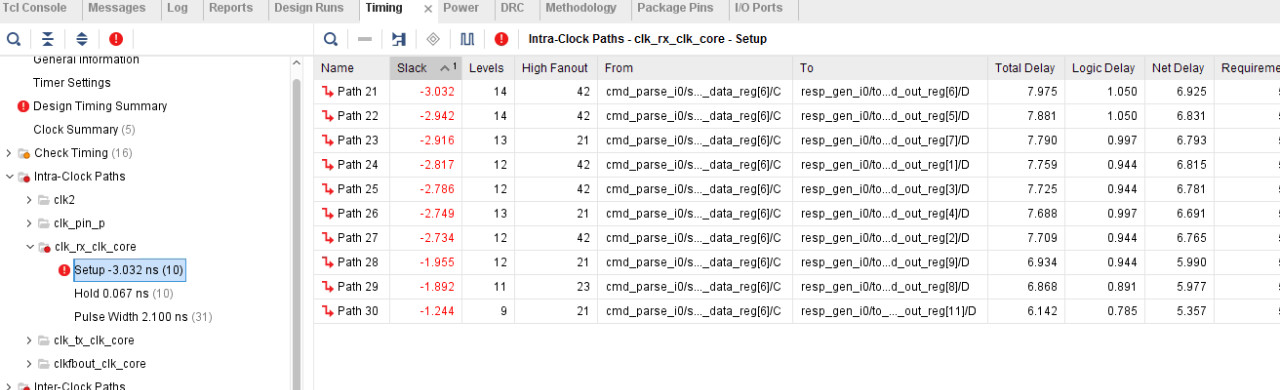

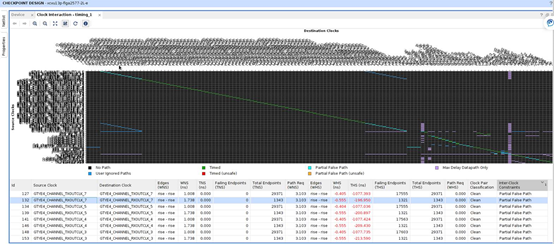

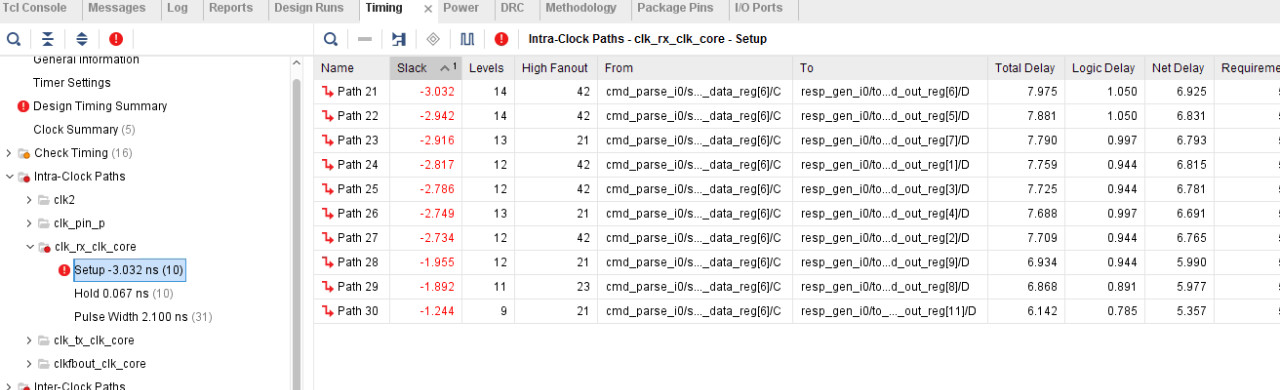

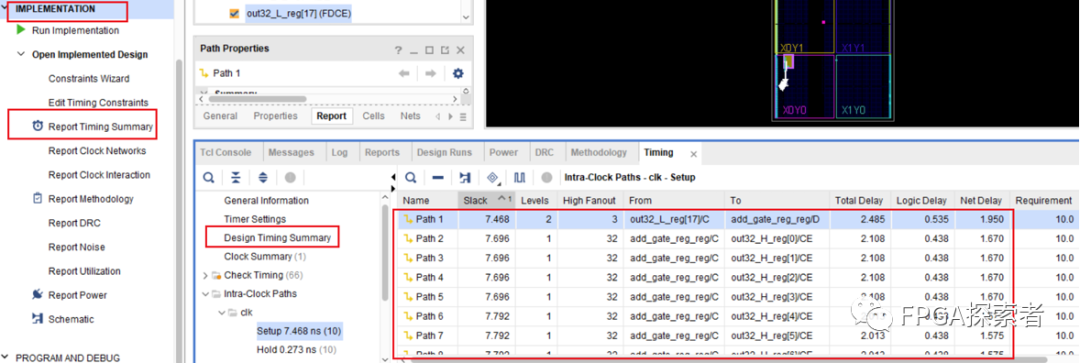

首先来看带有使能的数据,在本工程中的Tming Report中,也提示了同一个时钟域之间的几个路径建立时间不满足要求

2020-11-14 11:13:12 6042

6042

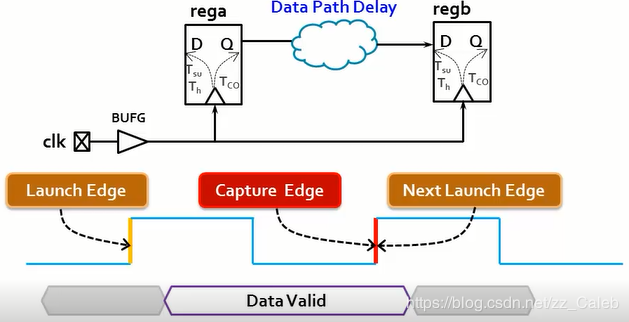

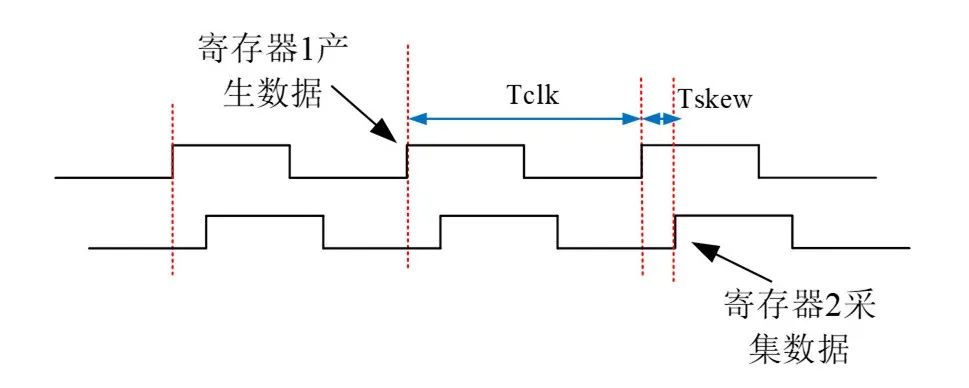

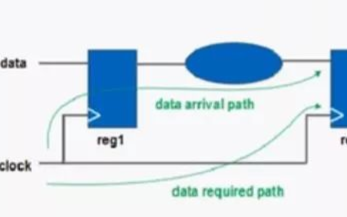

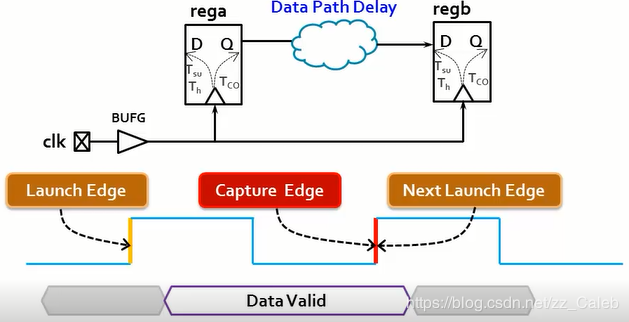

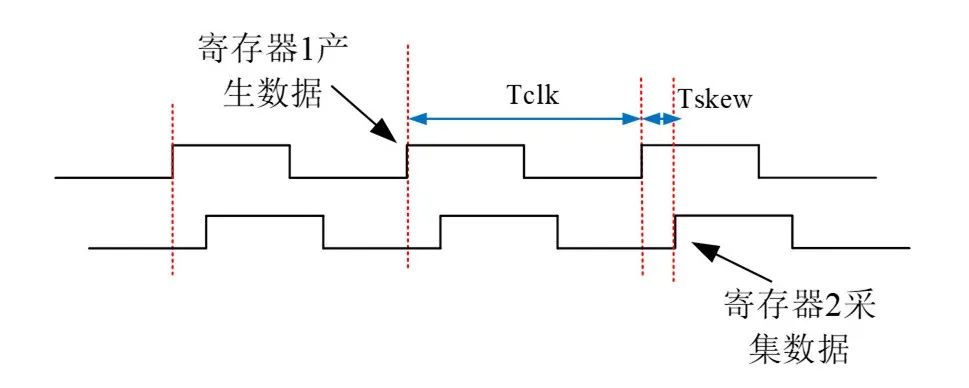

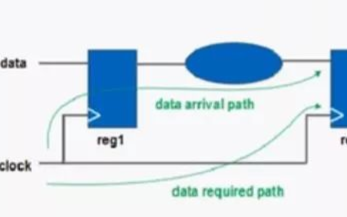

表。 这4类路径中,我们最为关心是②的同步时序路径,也就是FPGA内部的时序逻辑。 时序模型 典型的时序模型如下图所示,一个完整的时序路径包括源时钟路径、数据路径和目的时钟路径,也可以表示为触发器+组合逻辑+触发器的模型。 该

2020-11-17 16:41:52 3687

3687

边沿。 ④ 通常情况下这两个边沿会有一个时钟周期的差别。 2、时序路径 (Timing path典型时序路径有四种) ① ② 第一类时序路径(红色) - 从device A的时钟到FPGA的第一

2020-11-25 15:27:21 10856

10856

路径分析问题作一介绍: 1、时钟网络分析 时钟网络反映了时钟从时钟引脚进入FPGA后在FPGA内部的传播路径。 报告时钟网络命令可以从以下位置运行: ① VivadoIDE中的Flow

2020-11-29 10:34:00 10164

10164 在高速系统中FPGA时序约束不止包括内部时钟约束,还应包括完整的IO时序约束和时序例外约束才能实现PCB板级的时序收敛。因此,FPGA时序约束中IO口时序约束也是一个重点。只有约束正确才能在高速情况下保证FPGA和外部器件通信正确。

2022-09-27 09:56:09 2392

2392 FPGA开发过程中,离不开时序约束,那么时序约束是什么?简单点说,FPGA芯片中的逻辑电路,从输入到输出所需要的时间,这个时间必须在设定的时钟周期内完成,更详细一点,即需要满足建立和保持时间。

2023-06-06 17:53:07 1938

1938

在FPGA设计中,时序约束的设置对于电路性能和可靠性都至关重要。在上一篇的文章中,已经详细介绍了FPGA时序约束的基础知识。

2023-06-06 18:27:13 12757

12757

在FPGA设计中,时序约束对于电路性能和可靠性非常重要。在上一篇的文章中,已经详细介绍了FPGA时序约束的主时钟约束。

2023-06-12 17:29:21 4234

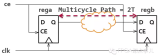

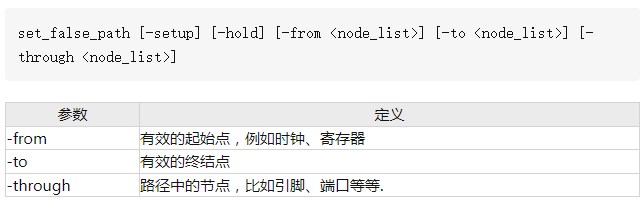

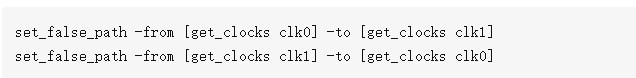

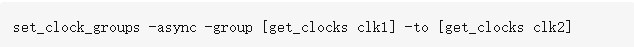

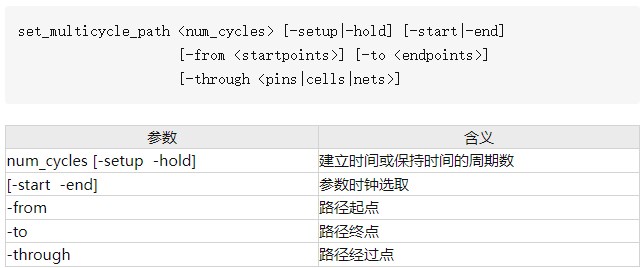

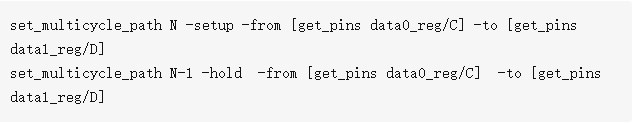

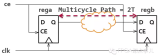

4234 前面几篇FPGA时序约束进阶篇,介绍了常用主时钟约束、衍生时钟约束、时钟分组约束的设置,接下来介绍一下常用的另外两个时序约束语法“伪路径”和“多周期路径”。

2023-06-12 17:33:53 3055

3055 关键路径通常是指同步逻辑电路中,组合逻辑时延最大的路径(这里我认为还需要加上布线的延迟),也就是说关键路径是对设计性能起决定性影响的时序路径。

2023-06-21 14:14:16 3117

3117

reg2reg路径约束的对象是源寄存器(时序路径的起点)和目的寄存器(时序路径的终点)都在FPGA内部的路径。

2023-06-26 14:28:01 1976

1976

同步电路设计中,时序是一个主要的考虑因素,它影响了电路的性能和功能。为了验证电路是否能在最坏情况下满足时序要求,我们需要进行静态时序分析,即不依赖于测试向量和动态仿真,而只根据每个逻辑门的最大延迟来检查所有可能的时序违规路径。

2023-06-28 09:35:37 2200

2200

时序路径作为时序约束和时序分析的物理连接关系,可分为片间路径和片内路径。

2023-08-14 17:50:02 1542

1542

针对第2章节时序路径中用到skew,在本章再仔细讲解一下。

2023-08-14 17:50:58 2095

2095

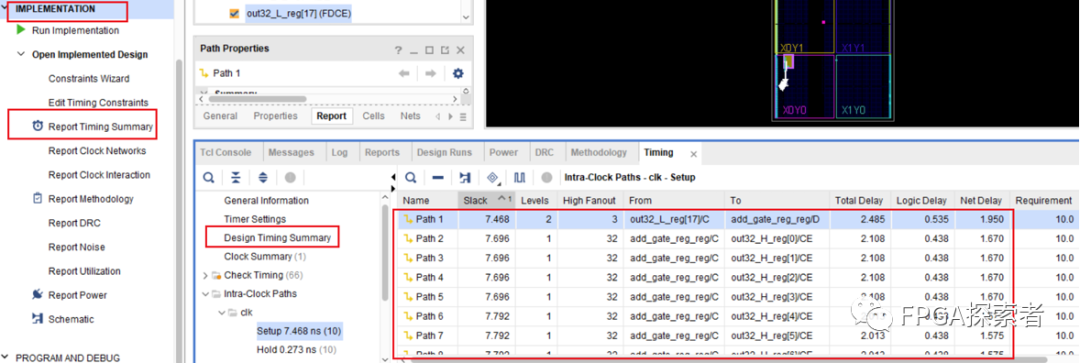

前面讲解了时序约束的理论知识FPGA时序约束理论篇,本章讲解时序约束实际使用。

2023-08-14 18:22:14 3030

3030

时钟周期约束是用于对时钟周期的约束,属于时序约束中最重要的约束之一。

2023-08-14 18:25:51 1777

1777 在输入信号到输出信号中,因为经过的传输路径、寄存器、门电路等器件的时间,这个时间就是时序。开发工具不知道我们路径上的要求,我们通过时序约束来告诉开发工具,根据要求,重新规划,从而实现我们的时序要求,达到时序的收敛。

2019-07-31 14:50:41 7018

7018

Altera 对应的这些时序概念和约束方法。前面首先介绍的第一个时序概念周期(Period),这个概念是 FPGA/ASIC 通用的一个概念,各方的定义相当统一,至多是描 述方式不同罢了,所有的 FPGA

2024-06-17 17:07:28

FPGA开发过程中,离不开时序约束,那么时序约束是什么?简单点说,FPGA芯片中的逻辑电路,从输入到输出所需要的时间,这个时间必须在设定的时钟周期内完成,更详细一点,即需要满足建立和保持时间

2023-11-15 17:41:10

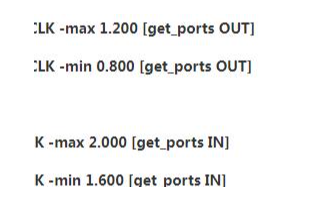

FPGA时序约束,总体来分可以分为3类,输入时序约束,输出时序约束,和寄存器到寄存器路径的约束。其中输入时序约束主要指的是从FPGA引脚输入的时钟和输入的数据直接的约束。共分为两大类:1、源同步系统

2015-09-05 21:13:07

的时序约束。FPGA作为PCB上的一个器件,是整个PCB系统时序收敛的一部分。FPGA作为PCB设计的一部分,是需要PCB设计工程师像对待所有COTS器件一样,阅读并分析其I/O Timing

2016-06-02 15:54:04

(InputDelay、OutputDelay)、上下拉电阻、驱动电流强度等。加入I/O约束后的时序约束,才是完整的时序约束。FPGA作为PCB上的一个器件,是整个PCB系统时序收敛的一部分。FPGA作为

2017-12-27 09:15:17

得到的,因此,时序分析即是通过分析FPGA设计中各个寄存器之间的数据和时钟传输路径,来分析数据和时钟延迟之间的关系。一个设计稳定的系统,必然能够保证整个系统中所有的寄存器都能够正确的寄存数据。2、时序约束的作用?时序分析即是通过相应的EDA软件告知EDA软件在对数...

2021-07-26 06:56:44

FPGA毕竟不是ASIC,对时序收敛的要求更加严格,本文主要介绍本人在工程中学习到的各种时序约束技巧。 首先强烈推荐阅读官方文档UG903和UG949,这是最重要的参考资料,没有之一。它提倡

2020-12-23 17:42:10

Tco(数据在芯片内部的路径延时)、Tsu(建立时间)和Th(保持时间)等,我们也可以用图示的这个模型来剖析一下芯片所给出的这些时序参数的具体路径。在这个模型中,画圈部分所覆盖的路径代表了和FPGA内部

2015-07-20 14:52:19

reg2reg路径的时序分析本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 我们可以先重点研究一下

2015-07-24 12:03:37

路径的分析,由于他们的launch和latch时钟都在FPGA内部,若像前面一样做过时钟的约束,那么FPGA对这些内部的时钟就已心知肚明,无需什么虚拟时钟。而对于pin2reg或reg2pin

2015-07-30 22:07:42

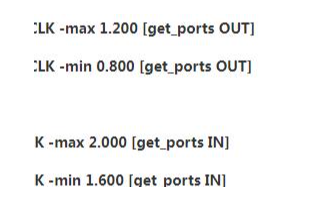

分析的。所以,为了获得这条路径的延时信息,我们势必需要对这条路径做一下约束。我们可以先试试将这条路径用set maximum delay和set minimux delay约束在0~5ns之间。set

2015-08-06 21:49:33

FPGA/CPLD的综合、实现过程中指导逻辑的映射和布局布线。下面主要总结一下Xilinx FPGA时序约束设计和分析。

2023-09-21 07:45:57

一组合电路,从Trig_sig输入一个上升沿触发信号,这个信号分别通过两条路径:路径1(path_1[0]到path_1[64])和路径2(path_2[0]到path_2[64])。希望约束路径1和路径2的延时差绝对值尽量小(即约束路径1和路径2的延时相等),如何做? 谢谢!

2013-12-30 15:12:19

的一条或多条路径。在 FPGA 设计中主要有四种类型的时序约束:PERIOD、OFFSET IN、OFFSET OUT 以及 FROM: TO(多周期)约束。赛灵思FPGA设计时序约束指南[hide][/hide]`

2012-03-01 15:08:40

。 TimingDesigner软件提供独特的时序参考图如测量和计算变量结果,从行内文字到文件都支持厂商特定的约束语法。例如,在一个FPGA约束布线中,对符合其动态文字窗口的语法要求中,可以通过时序图中为特定信号计算延迟

2017-09-01 10:28:10

,因此,为了避免这种情况,必须对fpga资源布局布线进行时序约束以满足设计要求。因为时钟周期是预先知道的,而触发器之间的延时是未知的(两个触发器之间的延时等于一个时钟周期),所以得通过约束来控制触发器之间的延时。当延时小于一个时钟周期的时候,设计的逻辑才能稳定工作,反之,代码会跑飞。

2018-08-29 09:34:47

当逻辑行为以默认的方式不能正确的定时逻辑行为,想以不同的方式处理时序时,必须使用时序例外命令。1. 多周期路径约束指明将数据从路径开始传播到路径结束时,所需要的时钟周期

2018-09-21 12:55:34

时序约束可以很复杂,这里我们先介绍基本的时序路径约束,复杂的时序约束我们将在后面进行介绍。在本节的主要内容如下所示:·时序路径和关键路径的介绍 ·建立时间、保持时间简述 ·时钟的约束(寄存器-寄存器之间的路径约束) ·输入延时的约束 ·输出延...

2021-07-26 08:11:30

各位大侠,能否分享一下找到影响时序的关键路径的一些经验

2014-02-27 11:17:52

TS_FastPath = FROM clk_a TO clk_b 20 ns;而我们的违规路径多是从某个模块下的寄存器到另一个模块下的寄存器,时序分析报告中会给出具体的路径。在QII中可以针对这条路径进行多周期约束

2015-04-30 09:52:05

Vivado运行Report Timing Summary时,只显示各个子项目最差的十条路径,很可能并不包含你最关心的路近,这个时候显示指定路径的时序报告就显得很重要了,下面就简单介绍一下

2021-01-15 16:57:55

Constraint

在多周期路径里,令驱动时钟的周期为PERIOD,数据可以最大n*PERIOD的时间的从源同步元件传输到目的同步元件,这一约束降低工具的布线难度而又不会影响时序性能。这种约束通常

2024-05-06 15:51:23

路径(Path specific exceptions),使用虚假路径、多周期路径约束

一、输入约束Input ConstraintOFFSET IN约束限定了输入数据和输入时钟边沿的关系

2024-04-12 17:39:04

。SDC 的格式也得到了逻辑综合器的支持。而且设定方法比较容易掌握。下面会详细讨论一下这种格式的约束设定方法。 时钟的设定方法: 时钟要分成两种, 一种是从端口上直接输入的时钟, 另一种是在 FPGA

2012-03-05 15:02:22

大部分的时序分析和约束都写在这里了。 一、基本时序路径1、clock-to-setup周期约束跨时钟域约束: (1)当源触发器和目标触发器的驱动时钟不同,且时钟的占空比不是50

2017-03-09 14:43:24

SDR和DDR两场景,而DDR又可再细分成边沿对齐和中心对齐。以上每种情况,其约束语句、获取参数的方法都是不一样的。想知道具体情况,欢迎观看本节视频。05 时序例外约束本节视频讲述多周期路径、异步时钟以及

2017-06-14 15:42:26

高速到低速上图给定的条件:高速时钟到低速时钟两个时钟有2ns的offset源端时钟是目的端时钟频率两倍如果不使用多周期约束,quartus II的时序分析工具将按照数据建立时间setup time

2015-03-17 17:43:52

什么是时序路径和关键路径?常见的时序路径约束有哪些?

2021-09-28 08:13:15

)。方法2调试起来简单,PLL设置简单,出错可能性小。通过不断调整相位,最终肯定可以正确通信。缺点也明显,接口一多,每个都要做随路时钟就浪费了。最近一直在做时序约束,总结一下时序约束过程。(1)根据时序

2016-09-13 21:58:50

本帖最后由 seduce 于 2015-2-3 14:20 编辑

关于约束今天在研究时序约束这一块,于是想着上来和大家分享一下心得,同时和大家交流交流,互相成长,欢迎批评指正。首先说一下

2015-02-03 14:13:04

,不同的寄存器在时钟脉冲的激励下相互配合完成特定的功能,所以要保证不同的寄存器在同一时刻的时钟脉冲激励下协同工作,就需要进行时序分析,通过分析得结果对FPGA进行约束,以保证不同寄存器间的时序要求

2017-02-26 09:42:48

本文转载IC_learner - 博客园数字IC之路-SDC篇(一):基本的时序路径约束_u012675910的博客-CSDN博客_sdc约束 RTL代码描述了电路的时序逻辑和组合逻辑,即RTL代码

2022-03-01 06:48:09

喜我对我的设计中的关键路径以及如何约束它们有疑问。我正在使用ISE 14.1进行实施。我有一个设计,其中关键路径(从源FD到目的地FD)给出-3.3ns的松弛(周期约束为10ns)。现在有没有其他

2019-04-08 08:58:57

的写法是一致的,后文将详细明。3.寄存器-寄存器的时序约束寄存器-寄存器的约束,在同步时序电路中,就是周期的约束。对于完全采用一个时钟的电路而言,对这一个clk指定周期约束即可。但是如果采用了多个时钟

2019-07-09 09:14:48

捕获不到,因此,这就涉及到了多周期路径约束的知识,我们可以让捕获周期为2 ,也就是说,等到下一锁存沿到来的时候再把数据捕获就好了。我们再来看一下这两段时间,第一段时间,也就是时钟发射沿相对时间加上时钟

2015-03-31 10:35:18

时序约束的概念 时序约束主要包括周期约束(FFS到FFS,即触发器到触发器)和偏移约束(IPAD到FFS、FFS到OPAD)以及静态路径约束(STA, IPAD到OPAD)等3种。通过附加约束条件可以使综合布线工具调整映射和布局布线过程,使设计达到时序要求。例如用OFFSET_IN_BEFORE

2011-03-16 18:10:38 0

0 针对目前导航系统中重要的多约束条件下路径规划功能,结合A*算法和蚁群算法提出一种新的不确定算法,该算法首先将多约束条件进行融合使其适合蚁群转移,并在基本蚁群算法基础

2012-06-07 08:56:53 0

0 FPGA时序约束方法很好地资料,两大主流的时序约束都讲了!

2015-12-14 14:21:25 19

19 基于时序路径的FPGA时序分析技术研究_周珊

2017-01-03 17:41:58 2

2 偏移约束。 这里先说一下周期约束:周期约束是为了达到同步组件的时序要求。如果相邻同步原件相位相反,那么延迟就会是时钟约束值的一半,一般不要同时使用上升沿和下降沿。注意:在实际工程中,附加的约束时间为期望值的

2017-02-09 02:56:06 918

918 Xilinx FPGA编程技巧常用时序约束介绍,具体的跟随小编一起来了解一下。

2018-07-14 07:18:00 5223

5223

未知环境下基于约束点的移动机器人路径规划_许重阳

2017-03-15 11:15:27 2

2 经常需要定义时序和布局约束。我们了解一下在基于赛灵思 FPGA 和 SoC 设计系统时如何创建和使用这两种约束。 时序约束 最基本的时序约束定义了系统时钟的工作频率。然而,更高级的约束能建立时钟路径之间

2017-11-17 05:23:01 3260

3260

一个好的FPGA设计一定是包含两个层面:良好的代码风格和合理的约束。时序约束作为FPGA设计中不可或缺的一部分,已发挥着越来越重要的作用。毋庸置疑,时序约束的最终目的是实现时序收敛。时序收敛作为

2017-11-17 07:54:36 2967

2967

我们先看看单时钟周期的情形,如下图所示。红色标记为默认情况下的建立时间检查,蓝色标记为默认情况下的保持时间检查,且注意保持时间的检查是以建立时间的检查为前提,即总是在建立时间检查的前一个时钟周期确定

2017-11-17 11:10:22 4395

4395

我们知道XDC与UCF的根本区别之一就是对跨时钟域路径(CDC)的缺省认识不同,那么碰到FPGA设计中常见的CDC路径,到底应该怎么约束,在设计上又要注意些什么才能保证时序报告的准确性?CDC

2017-11-18 04:04:24 6991

6991

在给FPGA做逻辑综合和布局布线时,需要在工具中设定时序的约束。通常,在FPGA设计工具中都FPGA中包含有4种路径:从输入端口到寄存器,从寄存器到寄存器,从寄存器到输出,从输入到输出的纯组合逻辑

2017-11-24 20:12:54 2067

2067 端和K端网络可靠性研究基础上,提出了基于截断的路径约束方法;并根据该方法构造二元决策图BDD模型进行带约束的是端网络可靠性分析。该算法针对k端点对点信息流在一定时间延迟下完成传输问题,具有较强的实际意义。实例分析结果

2017-12-06 14:03:03 0

0 目前对泊车方法的相关研究仅适用于平行泊车和垂直泊车中的一种泊车场景。为此,提出通用性的自主泊车路径规划方法。该方法融合车辆运动学约束和路径约束,以泊车时间为性能指标,建立泊车路径规划最优控制

2018-02-24 10:36:25 16

16 介绍FPGA约束原理,理解约束的目的为设计服务,是为了保证设计满足时序要求,指导FPGA工具进行综合和实现,约束是Vivado等工具努力实现的目标。所以首先要设计合理,才可能满足约束,约束反过来检查

2018-06-25 09:14:00 7199

7199 典型的时序路径有4类,如下图所示,这4类路径可分为片间路径(标记①和标记③)和片内路径(标记②和标记④)。

2020-01-27 10:37:00 3235

3235

伪路径约束 在本章节的2 约束主时钟一节中,我们看到在不加时序约束时,Timing Report会提示很多的error,其中就有跨时钟域的error,我们可以直接在上面右键,然后设置两个时钟的伪路径

2020-11-14 11:28:10 3628

3628

在 FPGA 设计进程中,时序收敛无疑是一项艰巨的任务。低估这项任务的复杂性常常导致工作规划面临无休止的压力。赛灵思提供了诸多工具,用于帮助缩短时序收敛所需时间,从而加速产品上市。本篇博文描述了一

2021-05-19 11:25:47 3922

3922

什么是关键路径? 关键路径分为两类:一类是时序违例的路径,主要是建立时间违例; 另一类是时序没有违例,但逻辑级数较高的路径。当然,第一类路径中可能会包含第二类路径。 对于第一类路径,其违例的原因

2021-07-06 17:22:48 6964

6964 A 时序约束的概念和基本策略 时序约束主要包括周期约束(FFS到FFS,即触发器到触发器)和偏移约束(IPAD到FFS、FFS到OPAD)以及静态路径约束(IPAD到OPAD)等3种。通过附加

2021-09-30 15:17:46 5927

5927 A 时序约束的概念和基本策略 时序约束主要包括周期约束(FFS到FFS,即触发器到触发器)和偏移约束(IPAD到FFS、FFS到OPAD)以及静态路径约束(IPAD到OPAD)等3种。通过附加

2021-10-11 10:23:09 6573

6573

Vivado下set_multicycle_path的使用说明 vivado下多周期路径约束(set_multicycle_path)的使用,set_multicycle_path一般...

2021-12-20 19:12:17 1

1 本文章探讨一下FPGA的时序约束步骤,本文章内容,来源于配置的明德扬时序约束专题课视频。

2022-03-16 09:17:19 4001

4001

上一篇《FPGA时序约束分享01_约束四大步骤》一文中,介绍了时序约束的四大步骤。

2022-03-18 10:29:28 2166

2166

左边的电路图是需要分析的电路,我们的目的是要对此电路进行时序分析,那首先要找到该电路需要分析的时序路径,既然找路径,那找到时序分析的起点与终点即可。

2022-05-04 17:13:00 3224

3224 本文章探讨一下FPGA的时序input delay约束,本文章内容,来源于配置的明德扬时序约束专题课视频。

2022-05-11 10:07:56 4989

4989

本文章探讨一下FPGA的时序input delay约束,本文章内容,来源于明德扬时序约束专题课视频。

2022-07-25 15:37:07 3757

3757

要从时序分析删除一组路径,如果您确定这些路径不会影响时序性能(False 路径),可用FROM-TO 约束以及时序忽略 (TIG) 关键字。

2022-08-02 08:57:26 1754

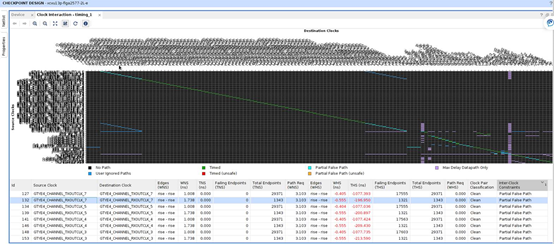

1754 ,为什么有些路径在分析时忽略了?我怎么去定位这些约束是哪里设定的?本文结合一个具体案例,阐述了如何追溯同一时钟域内partial false path的来源,希望为开发者的设计调试提供一些技巧和窍门。

2022-08-02 08:03:36 2297

2297

时间裕量包括建立时间裕量和保持时间裕量(setup slack和hold slack)。从字面上理解,所谓“裕量”即富余的、多出的。什么意思呢?即保持最低要求的建立时间或保持时间所多出的时间,那么“裕量”越多,意味着时序约束越宽松。

2022-08-04 17:45:04 1079

1079 是很多文献所说的current launch和current latch,但是某些情况下,这两者之间并不一定只是一个时钟周期,比如加上一个捕获使能信号,或者跨时钟域的情况,两者时钟有相位差的情况,此时就需要设置多周期。 二、如何理解多周期路径约束? 首先要理解一个数据

2022-12-10 12:05:02 2621

2621 时序约束是我们对FPGA设计的要求和期望,例如,我们希望FPGA设计可以工作在多快的时钟频率下等等。因此,在时序分析工具开始对我们的FPGA设计进行时序分析前,我们必须为其提供相关的时序约束信息。在

2022-12-28 15:18:38 5209

5209 1、时序错误的影响 一个设计的时序报告中,design run 时序有红色,裕量(slack)为负数时,表示时序约束出现违例,虽然个别违例不代表你的工程就有致命的问题,但是这是一

2023-03-17 03:25:03 2014

2014 上一篇《XDC 约束技巧之时钟篇》介绍了 XDC 的优势以及基本语法,详细说明了如何根据时钟结构和设计要求来创建合适的时钟约束。我们知道 XDC 与 UCF 的根本区别之一就是对跨时钟域路径(CDC

2023-04-03 11:41:42 3390

3390 FPGA/CPLD的综合、实现过程中指导逻辑的映射和布局布线。下面主要总结一下Xilinx FPGA时序约束设计和分析。

2023-04-27 10:08:22 2404

2404 典型的时序路径有4类,如下图所示,这4类路径可分为片间路径(标记①和标记③)和片内路径(标记②和标记④)。

2023-06-26 10:30:43 1138

1138

FPGA开发过程中,离不开时序约束,那么时序约束是什么?简单点说,FPGA芯片中的逻辑电路,从输入到输出所需要的时间,这个时间必须在设定的时钟周期内完成,更详细一点,即需要满足建立和保持时间。

2023-06-26 14:42:10 1252

1252

今天介绍一下,如何在Vivado中添加时序约束,Vivado添加约束的方法有3种:xdc文件、时序约束向导(Constraints Wizard)、时序约束编辑器(Edit Timing Constraints )

2023-06-26 15:21:11 6080

6080

今天我们要介绍的时序分析概念是 **时序路径** (Timing Path)。STA软件是基于timing path来分析timing的。

2023-07-05 14:54:43 3161

3161

命令set_multicycle_path常用来约束放松路径的约束。通常情况下,这种路径具有一个典型的特征:数据多个周期翻转一次,如下图所示。因此,我们把这种路径称为多周期路径(FPGA设计中更多的是单周期路径,每个周期数据均翻转)。

2023-09-14 09:05:02 1772

1772

详细的原时钟时序、数据路径时序、目标时钟时序的各延迟数据如下图所示。值得注意的是数据路径信息,其中包括Tco延迟和布线延迟,各级累加之后得到总的延迟时间。

2024-04-29 10:39:04 1656

1656

Vivado中时序分析工具默认会分析设计中所有时钟相关的时序路径,除非时序约束中设置了时钟组或false路径。使用set_clock_groups命令可以使时序分析工具不分析时钟组中时钟的时序路径,使用set_false_path约束则会双向忽略时钟间的时序路径

2025-04-23 09:50:28 1079

1079

电子发烧友App

电子发烧友App

评论