时序路径

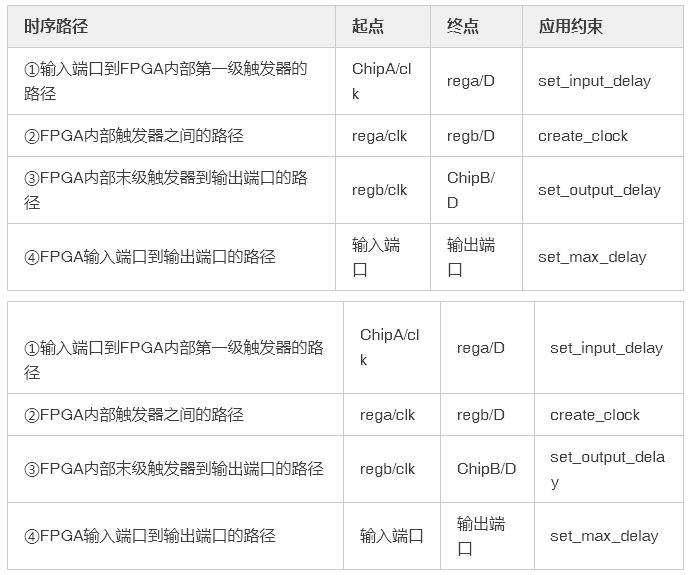

典型的时序路径有4类,如下图所示,这4类路径可分为片间路径(标记①和标记③)和片内路径(标记②和标记④)。

对于所有的时序路径,我们都要明确其起点和终点,这4类时序路径的起点和终点分别如下表。

这4类路径中,我们最为关心是②的同步时序路径,也就是FPGA内部的时序逻辑。

时序模型

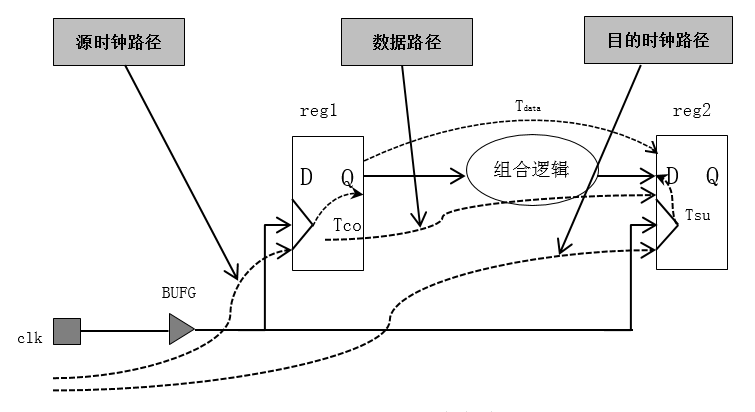

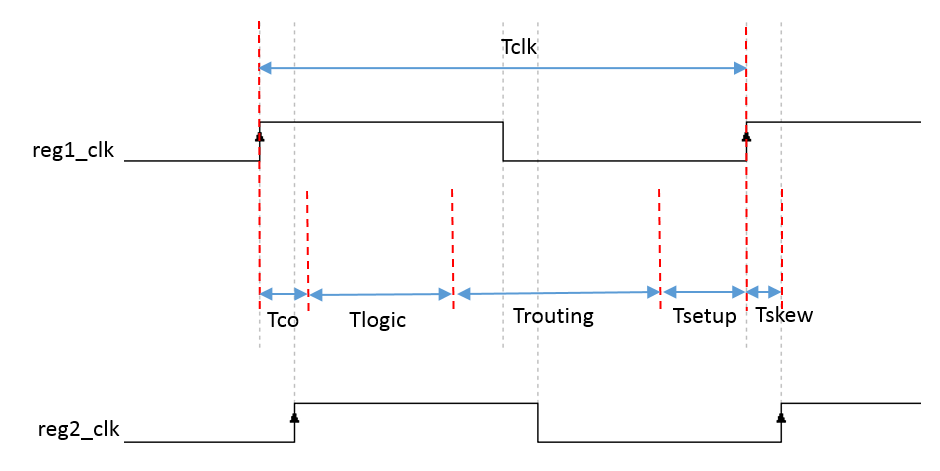

典型的时序模型如下图所示,一个完整的时序路径包括源时钟路径、数据路径和目的时钟路径,也可以表示为触发器+组合逻辑+触发器的模型。

该时序模型的要求为(公式1)

Tclk ≥ Tco + Tlogic + Trouting + Tsetup - Tskew

其中,Tco为发端寄存器时钟到输出时间;Tlogic为组合逻辑延迟;Trouting为两级寄存器之间的布线延迟;Tsetup为收端寄存器建立时间;Tskew为两级寄存器的时钟歪斜,其值等于时钟同边沿到达两个寄存器时钟端口的时间差;Tclk为系统所能达到的最小时钟周期。

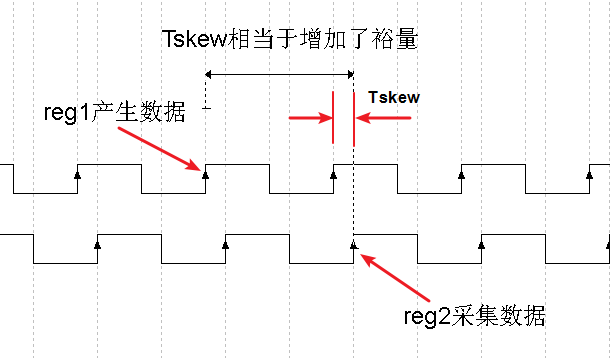

这里我们多说一下这个Tskew,skew分为两种,positive skew和negative skew,其中positive skew见下图,这相当于增加了后一级寄存器的触发时间。

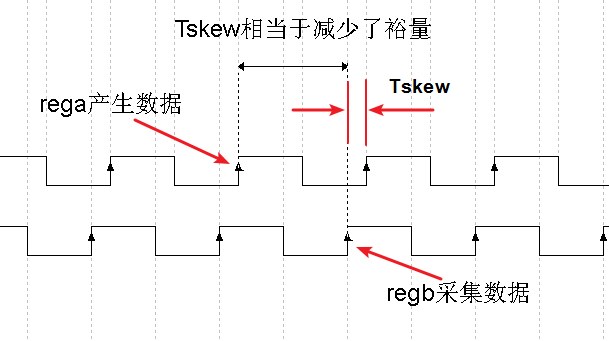

但对于negative skew,则相当于减少了后一级寄存器的触发时间,如下图所示。

当系统稳定后,都会是positive skew的状态,但即便是positive skew,综合工具在计算时序时,也不会把多出来的Tskew算进去。

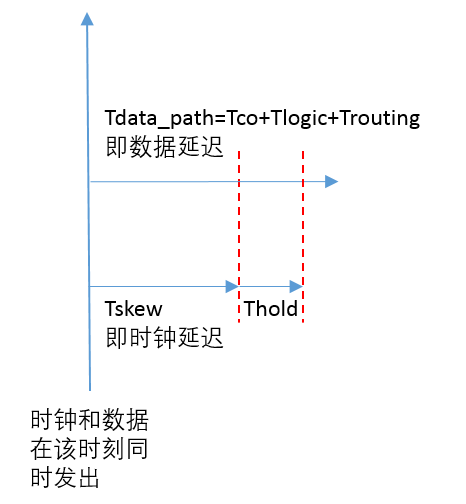

用下面这个图来表示时序关系就更加容易理解了。为什么要减去Tskew,下面这个图也更加直观。

发送端寄存器产生的数据,数据经过Tco、Tlogic、Trouting后到达接收端,同时还要给接收端留出Tsetup的时间。而时钟延迟了Tskew的时间,因此有:(公式2)

Tdata/_path + Tsetup < = Tskew + Tclk

对于同步设计Tskew可忽略(认为其值为0),因为FPGA中的时钟树会尽量保证到每个寄存器的延迟相同。

公式中提到了建立时间,那保持时间在什么地方体现呢?

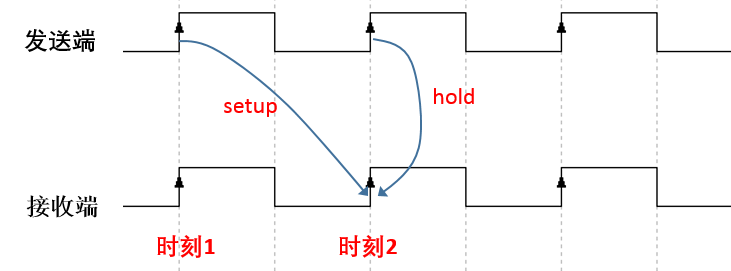

保持时间比较难理解,它的意思是reg1的输出不能太快到达reg2,这是为了防止采到的新数据太快而冲掉了原来的数据。保持时间约束的是同一个时钟边沿,而不是对下一个时钟边沿的约束。

reg2在边沿2时刻刚刚捕获reg1在边沿1时刻发出的数据,若reg1在边沿2时刻发出的数据过快到达reg2,则会冲掉前面的数据。因此保持时间约束的是同一个边沿。

在时钟沿到达之后,数据要保持Thold的时间,因此,要满足:(公式3)

Tdata/_path = Tco + Tlogic + Trouting ≥ Tskew + Thold

这两个公式是FPGA的面试和笔试中经常问到的问题,因为这种问题能反映出应聘者对时序的理解。

在公式1中,Tco跟Tsu一样,也取决于芯片工艺,因此,一旦芯片型号选定就只能通过Tlogic和Trouting来改善Tclk。其中,Tlogic和代码风格有很大关系,Trouting和布局布线的策略有很大关系。

编辑:hfy

-

寄存器

+关注

关注

31文章

5620浏览量

130454 -

触发器

+关注

关注

14文章

2065浏览量

63576 -

时序路径

+关注

关注

0文章

12浏览量

1523

发布评论请先 登录

SHARP LZ9FD534:TFT - LCD模块时序控制IC深度解析

LZ9FC23:TFT - LCD模块时序控制IC的深度解析

FPGA时序收敛的痛点与解决之道——从一次高速接口调试谈起

深入解析LTC2924:高效电源时序控制器的卓越之选

RGB时序灯条的工作原理讲解

输入引脚时钟约束_Xilinx FPGA编程技巧-常用时序约束详解

数字IC/FPGA设计中的时序优化方法

FPGA案例之时序路径与时序模型解析

FPGA案例之时序路径与时序模型解析

评论