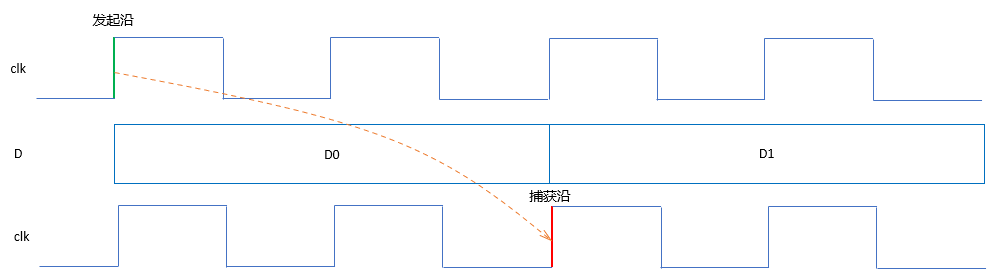

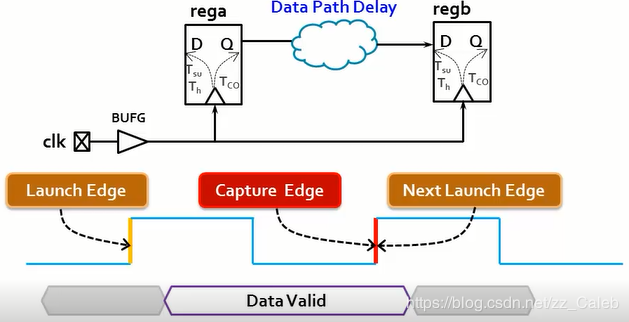

命令set_multicycle_path常用来约束放松路径的约束。通常情况下,这种路径具有一个典型的特征:数据多个周期翻转一次,如下图所示。因此,我们把这种路径称为多周期路径(FPGA设计中更多的是单周期路径,每个周期数据均翻转)。

一般情况下,多周期路径约束的对象都是FPGA内部路径,路径所包含的逻辑单元也都是FPGA内部单元如触发器、BRAM或DSP等。但有时在片间接口使用set_input_delay和set_output_delay约束时,也会用到set_multicycle_path。这里我们就来讨论这种情形。

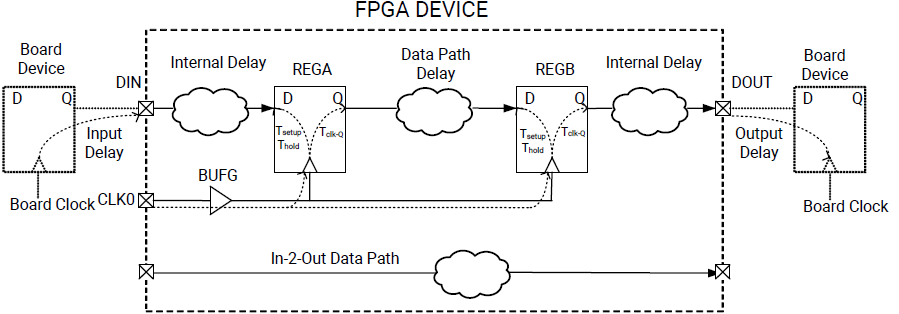

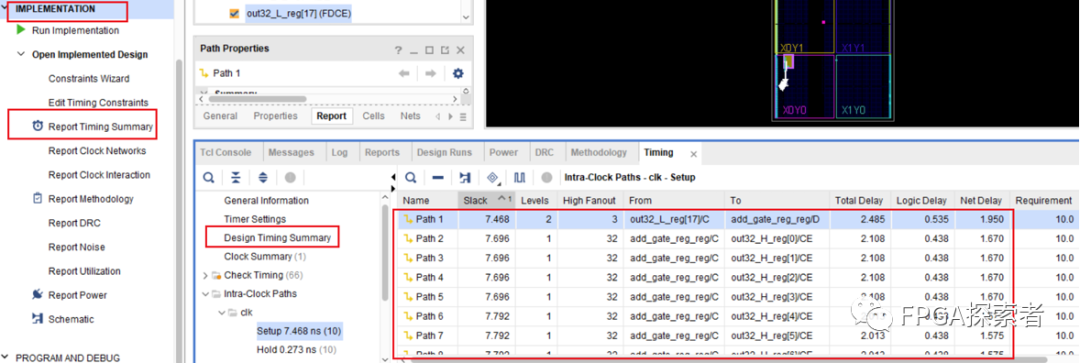

我们先从系统级角度看一下FPGA设计存在的4类时序路径,如下图所示。这4类路径包括:上游芯片到FPGA管脚(用set_input_delay约束)、FPGA内部路径(用create_clock约束)、FPGA管脚到下游芯片(用set_output_delay约束)和FPGA管脚到FPGA管脚(用set_max_delay约束)。就前三条路径而言,如果把上游芯片、FPGA芯片和下游芯片作为一个整体看待,我们就会发现这三条路径本质上是一类路径,起点单元和终点单元都是触发器。只是触发器可能在FPGA外部而已。正因此,凡是适合于FPGA内部路径的多周期路径约束情形也适合于接口多周期路径约束情形。同时,也能看出Vivado的这种系统级的时序分析引擎对接口时序约束极为便利。

情形1:数据每多个时钟周期翻转一次

如下图所示时序波形,数据每两个时钟周期翻转一次。

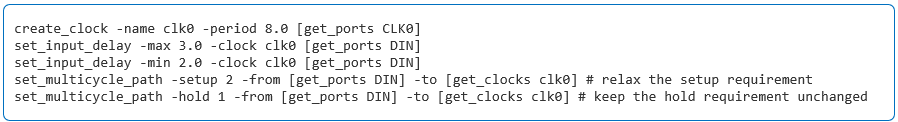

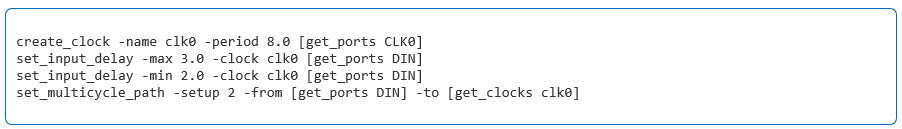

如果数据是由上游芯片发送给FPGA,那么就需要用set_input_delay结合set_multicycle_path一起对接口路径进行约束,如下图所示。这里最后两行使用了set_multicycle_path,一个针对建立时间,一个针对保持时间。

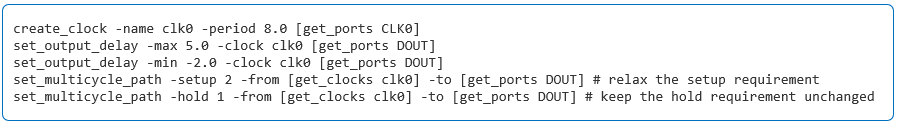

如果数据是从FPGA发送给下游芯片,那么就需要用set_output_delay结合set_multicycle_path一起对接口路径进行约束,如下图所示。

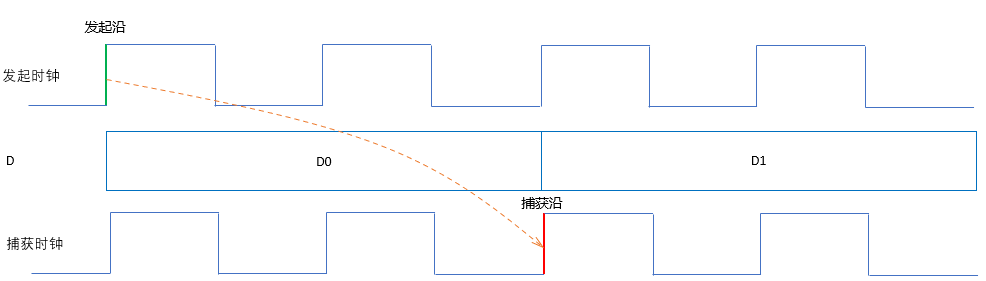

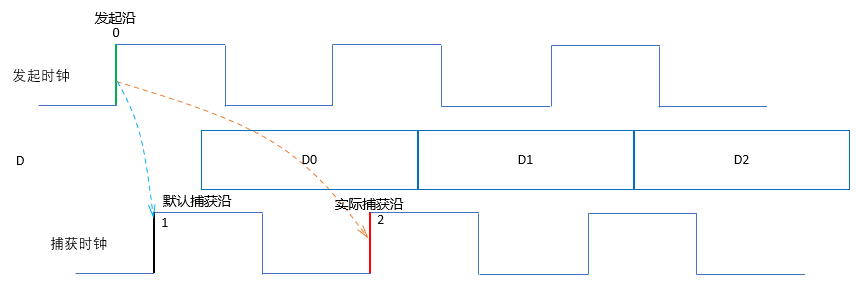

情形2:捕获时钟和发送时钟同频但有相差

如下图所示,发起时钟和捕获时钟同频但不同相。默认情况下,Vivado会选择两个时钟最为接近的边沿作为发起沿和捕获沿,如图中的蓝色箭头所示。显然,这种情况下,时序约束过紧且不符实际。这就要通过set_multicycle_path告诉工具真正的捕获沿是在2号标记处。

如果该路径存在于FPGA输入接口处,那么可以采用set_input_delay结合set_multicycle_path一起约束,如下图所示。

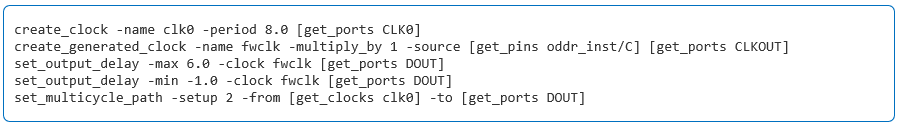

如果该路径存在于FPGA输出接口处的源同步设计,那么可以采用set_output_delay结合set_multicycle_path一起约束,如下图所示。

审核编辑:汤梓红

-

FPGA

+关注

关注

1664文章

22508浏览量

639495 -

FPGA设计

+关注

关注

9文章

431浏览量

28217 -

命令

+关注

关注

5文章

759浏览量

23975 -

约束

+关注

关注

0文章

83浏览量

13210

原文标题:对于输入/输出路径什么场合需要用set_multicycle_path?

文章出处:【微信号:Lauren_FPGA,微信公众号:FPGA技术驿站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

详细解析vivado约束时序路径分析问题

FPGA时序约束之伪路径和多周期路径

FPGA时序分析之关键路径

fpga时序分析案例 调试FPGA经验总结

FPGA实战演练逻辑篇52:基本时序路径

FPGA实战演练逻辑篇61:CMOS摄像头接口时序设计1理想时序

全面解读时序路径分析提速

FPGA设计存在的4类时序路径

FPGA设计存在的4类时序路径

评论