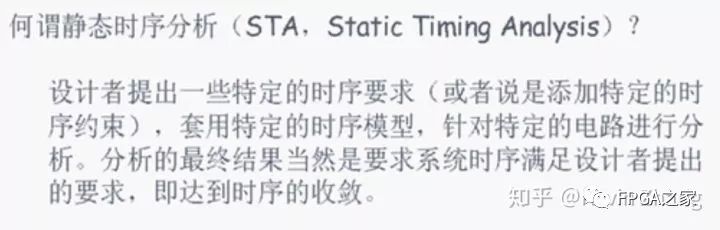

什么是静态时序分析?

通俗来说:在输入信号到输出信号中,因为经过的传输路径、寄存器、门电路等器件的时间,这个时间就是时序。开发工具不知道我们路径上的要求,我们通过时序约束来告诉开发工具,根据要求,重新规划,从而实现我们的时序要求,达到时序的收敛。

我们对整个设计添加时序约束,让整个设计。

时序的欠约束:约束的少了;

时序的过约束:约束了过了;

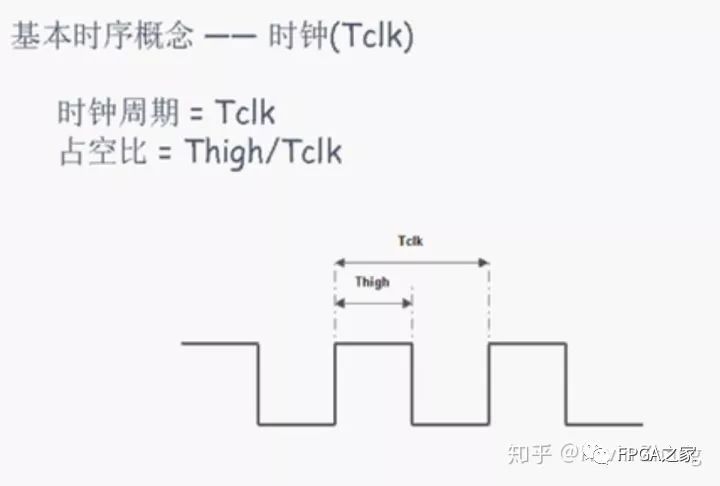

时序基本概念:时钟

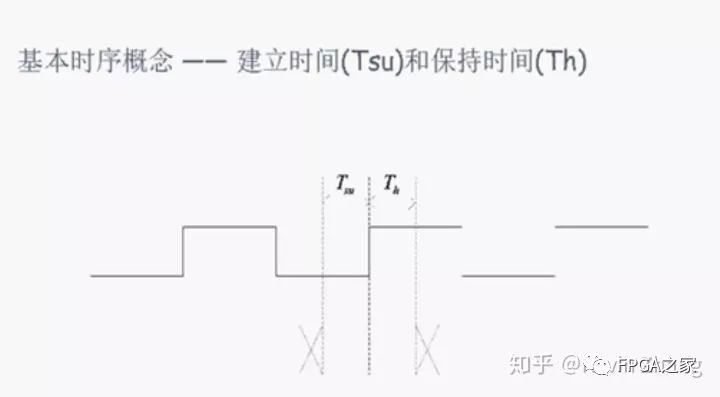

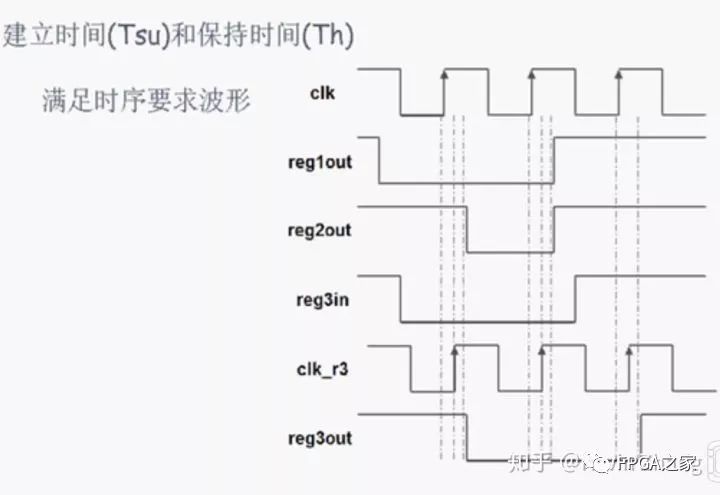

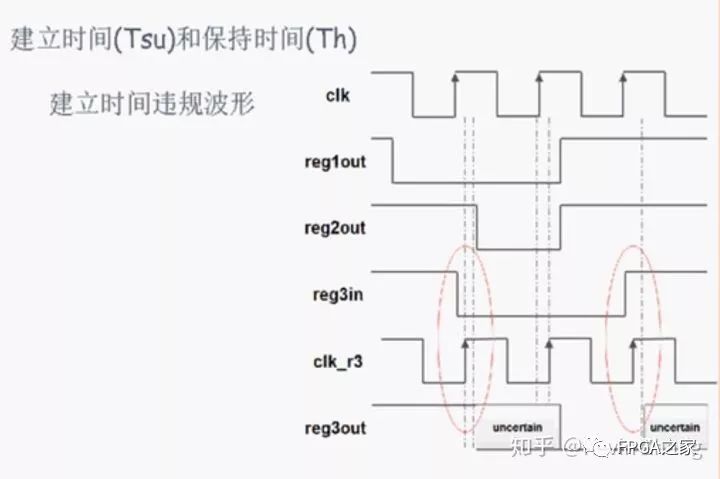

建立时间setup和保持时间hold

建立时间:在时钟上升沿前,数据不能改变的最小时间;

保持时间:在数据上升沿后,数据不能改变的最小时间;

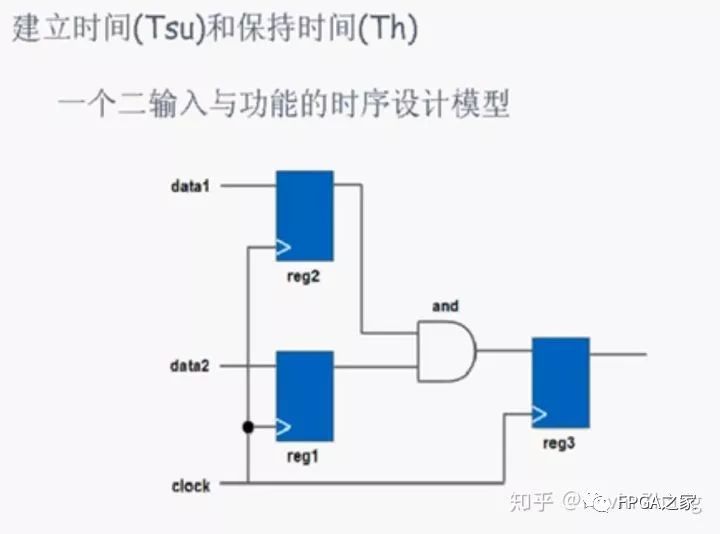

例子

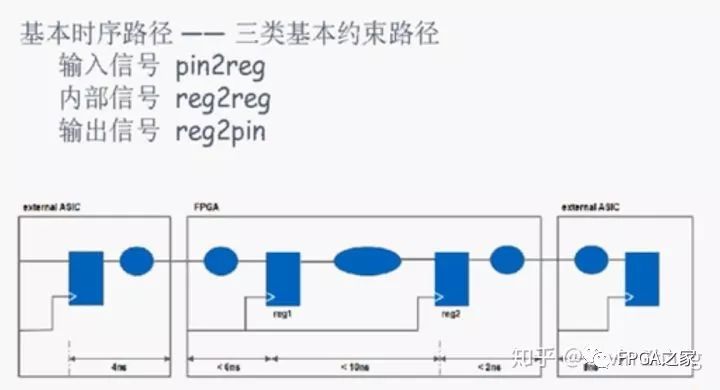

三种时序路径

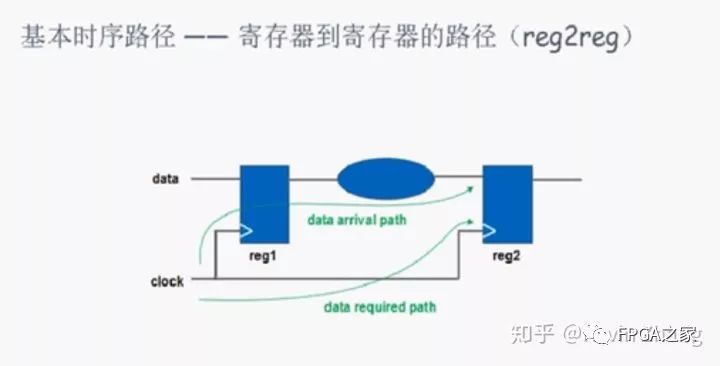

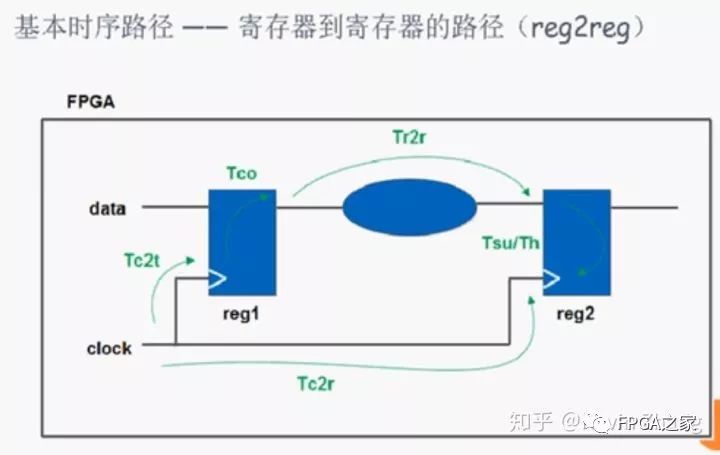

分析一个寄存器的延时

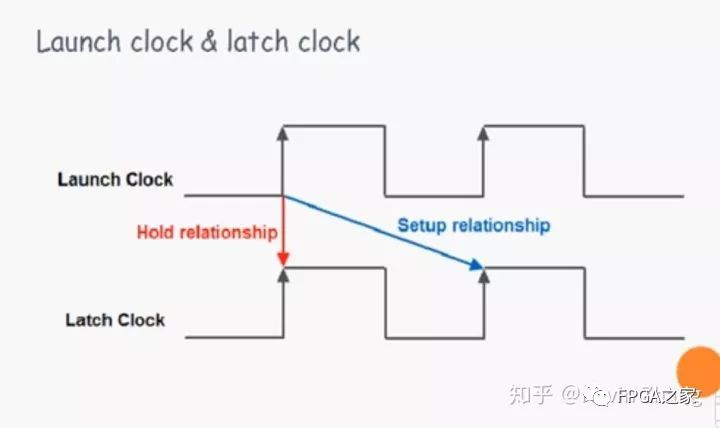

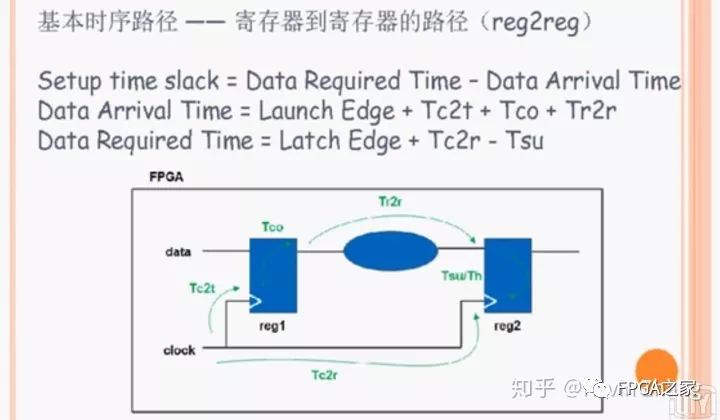

setup slack余量,这个时间是差了一个时钟周期;

数据达到时间,首先是发射时钟+时钟到REG1的延时+reg1的延时+传输路径的延时

数据时间需求:锁存时钟+时钟到reg2的延时-setup时间

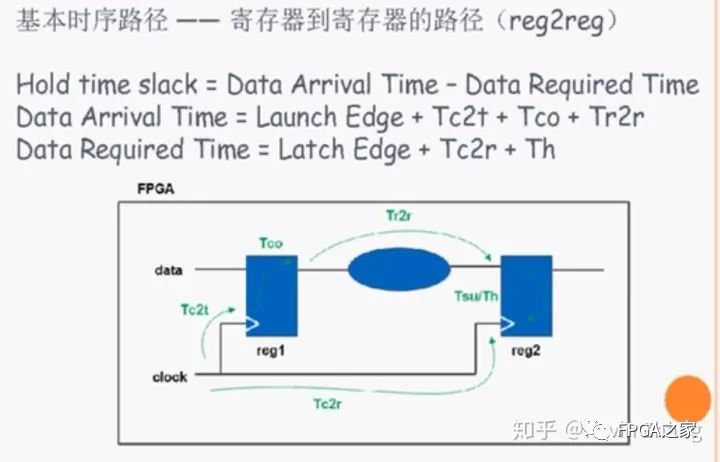

hold时间余量,这里分析的应该是同一个周期里面的时间,这个时间是对齐的;

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1664文章

22509浏览量

639533 -

时序设计

+关注

关注

0文章

22浏览量

44143

原文标题:FPGA学习-时序分析基础001

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

2026深入拆解:Gemini 3.0 镜像官网如何理解 FPGA 时序约束并自动生成 SDC 文件

在 Vivado 或 Quartus 中引用的约束文件。本教程用一个包含多时钟域和 DDR 接口的真实设计,完整拆解从需求到 SDC 的全过程。 为什么

Xilinx FPGA中的混合模式时钟管理器MMCME2_ADV详解

在 FPGA 的浩瀚宇宙中,时钟系统不仅是驱动逻辑运转的“心脏”,更是决定系统稳定性与性能上限的“指挥棒”。对于 Xilinx 7 系列 FPGA 开发者而言,如果仅满足于使用 Clo

FPGA时序收敛的痛点与解决之道——从一次高速接口调试谈起

在FPGA开发中,时序收敛往往是项目后期最令人头疼的环节。许多工程师都有过这样的经历:RTL仿真通过,综合布线后却出现大量时序违例,为了满足

输入引脚时钟约束_Xilinx FPGA编程技巧-常用时序约束详解

基本的约束方法

为了保证成功的设计,所有路径的时序要求必须能够让执行工具获取。最普遍的三种路径以及异常路径为:

输入路径(Input Path),使用输入约束

寄存器到寄存器路径

发表于 01-16 08:19

数字IC/FPGA设计中的时序优化方法

在数字IC/FPGA设计的过程中,对PPA的优化是无处不在的,也是芯片设计工程师的使命所在。此节主要将介绍performance性能的优化,如何对时序路径进行优化,提高工作时钟频率。

开源RISC-V处理器(蜂鸟E203)学习(二)修改FPGA综合环境(移植到自己的Xilinx FPGA板卡)

。

vivado加载所有的约束文件,这里需要将旧的文件remove掉,也就是蓝框的两个文件。

进行综合时,如果提示jtag tck的iobuf错误,建议在约束文件中添加如下

发表于 10-31 08:46

移植E203到Genesys2开发板时遇到时序问题的常见原因

在移植E203到自己的Genesys2开发板时候遇到时序问题的常见原因

1.在vivado中,连接的管脚的信号一般都会自动添加OBUF或IBUF。

但是对于inout类型的接口,不

发表于 10-29 07:04

E203移植genesys2(差分时钟板)生成比特流文件全过程

是100Mhz,输入选择单时钟源,输出只需要16Mhz。

添加完ip和自定义的分频文件之后记得在system.v中例化。

4.设置头文件与注释

添加`define FPGA_S

发表于 10-27 07:16

时序约束问题的解决办法

Time 是否满足约束。

我们要留意的是 WNS 和 WHS 两个数值,如果这两个数值为红色,就说明时序不满足约束。下面将解释怎么解决这个问题。

1. Setup Time 违例

Setup

发表于 10-24 09:55

关于综合保持时间约束不满足的问题

1、将 nuclei-config.xdc 和 nuclei-master.xdc 加入到项目工程中,综合得到时序约束报告如下:

保持时间约束不满足,分析原因,发现所有不满足均出现在

发表于 10-24 07:42

蜂鸟e203移植fpga上如何修改约束文件

第一步:我们先导入官方网站中蜂鸟e203的代码提供的e203添加进去,并加入ddr200T中的

src.文件中的system.v文件并加入约

发表于 10-24 07:18

技术资讯 I Allegro 设计中的走线约束设计

本文要点在进行时序等长布线操作的时候,在布线操作的时候不管你是走蛇形线还是走折线,约束管理器会自动帮你计算长度、标偏差,通过精确控制走线长度,来实现信号的时序匹配。约束设计就是一套精准

西门子再收购EDA公司 西门子宣布收购Excellicon公司 时序约束工具开发商

开发、验证及管理时序约束的软件纳入西门子EDA的产品组合。此次收购将帮助西门子提供实施和验证流程领域的创新方法, 使系统级芯片 (SoC) 设计人员能够优化功耗、性能和面积 (PPA),加快设计速度,增强功能

FPGA开发中如何对整个设计添加时序约束

FPGA开发中如何对整个设计添加时序约束

评论