本文介绍FPGA与高速ADC接口方式和标准以及JESD204与FPGA高速串行接口。

2025-06-12 14:18:21 2881

2881

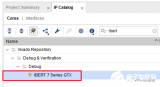

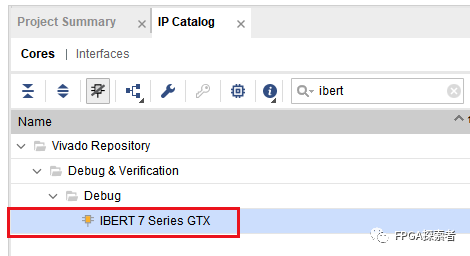

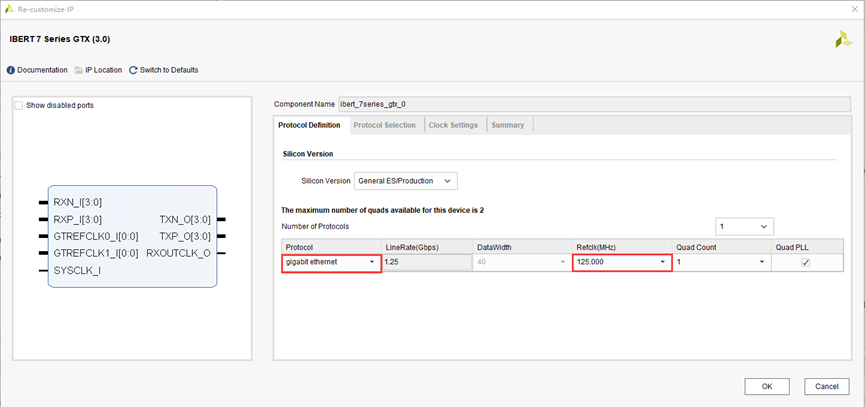

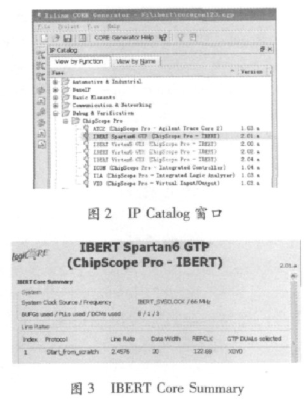

IBERT(Integrated Bit Error Ratio Tester),集成误码率测试仪。作为用户来说可以使用这个工具对自己设计的板子中的高速串行收发器进行简单测试,从而判断设计的接口是否

2025-11-24 09:11:33 2684

2684

GTX、GTH等具体是什么就不多介绍了,网上有很多。写这个的目的,就是当收到FPGA板卡后,要判断本板的高速串行总线是否能够应用,那就需要做基本的功能测试。我们可以用xilinx提供的ibert进行

2020-12-31 15:36:04 9210

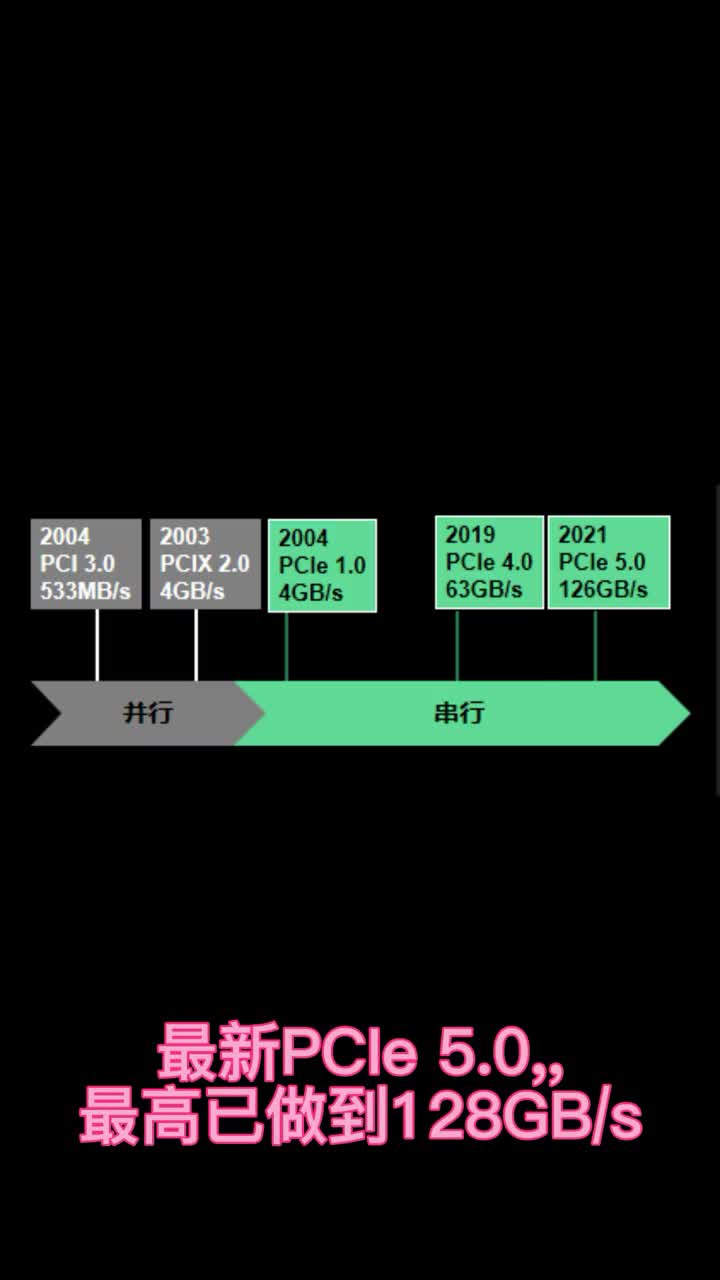

9210 串行接口常用于芯片至芯片和电路板至电路板之间的数据传输。随着系统带宽不断增加至多吉比特范围,并行接口已经被高速串行链接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是独立

2019-10-23 07:16:35

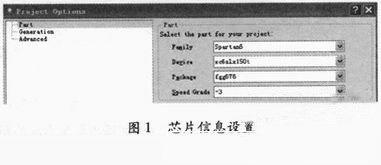

下载配置与调试接口电路设计FPGA是SRAM型结构,本身并不能固化程序。因此FPGA需要一片Flash结构的配置芯片来存储逻辑配置信息,用于进行上电配置。以Altera公司的FPGA为例,配置芯片

2019-06-11 05:00:07

FPGA的高速接口应用注意事项主要包括以下几个方面:

信号完整性与电磁兼容性(EMC) :

在设计FPGA高速接口时,必须充分考虑信号完整性和电磁兼容性。这要求合理的PCB布局、走线策略和屏蔽技术

2024-05-27 16:02:50

,对时钟的稳定性和精度要求较高。设计时需要仔细配置时钟源,确保时钟信号的稳定性和准确性。对于SATA III接口,串行时钟速率高达6GHz,可能需要使用FPGA内部的高性能时钟模块或外部时钟源

2024-05-27 16:20:22

的HDL修改才能使en_gtpwr变为高电平。这是否意味着IBERT软件或Artix FPGA存在问题?提前致谢,赫伯特--------------是的,我这样做是为了好玩!

2020-08-26 07:34:22

我正在研究IBERt virtex 6.是否可以在FPGA上同时运行外部时钟模块和IBERT模块。外部时钟模块的输出在IBERT中被指定为外部时钟引脚号?

2020-03-11 09:28:07

。 串行通信的制式有:单工、半双工、全双工三种。 计算机的串行通信接口是RS-232的标准接口,而单片机的UART接口则是TTL电平,两者的电气规范不一致,所以要完成两者之间的数据通信,就需要借助接口芯片在两者之间进行电平转换,常用

2022-02-17 06:43:25

[tr=transparent]再FPGA设计系统时,大部分人会选择SRAM、SDRAM、甚至DDR. 这些选择,要么价格比较高,要么需要很多I/O资源 这里介绍一种串行PSRAM方案 PSRAM

2018-07-03 08:52:46

双线、8b/10b编码标准的产品。这个串行接口与FPGA配合使用可以实现体积更小的高性能系统。 但在这个领域中,一切都是发展变化的。面对带有大量高速信道的应用系统,例如物理实验中或高端MRI扫描仪中

2019-05-20 05:00:07

的问题,如果采用AC耦合,Altera推荐电路仅是在两根差分线上各串一个电容即可,因为部分耦合网络FPGA内部有考虑。 最近一次看NS的研讨会,他们出了一个LPDS的接口标准,也是差分高速串行标准。“LP”即

2015-01-22 14:20:51

高速无线调试器HSWLDBG BURNER 3.3,5

2023-03-28 13:06:20

RocketIO高速串行接口本人在北京工作6年以上,从事FPGA外围接口设计,熟练使用Virtex-5/Virtex-6 FPGA,非常熟悉RocketIO GTP/GTX协议,Aurora协议

2014-03-01 18:46:35

。

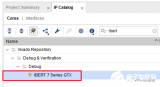

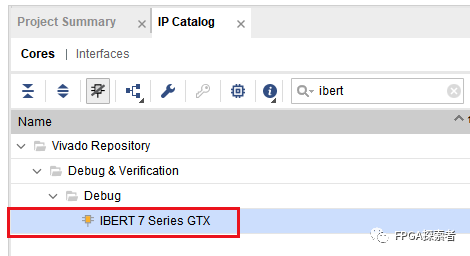

为了方便用户使用,vivado中提供了一个IBERT(Integrated Bit Error Ratio Tester)的测试工具用于对Xilinx FPGA芯片的高速串行收发器进行板级硬件测试

2024-11-12 16:54:07

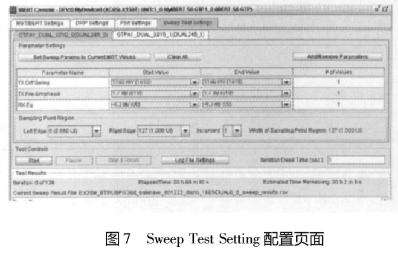

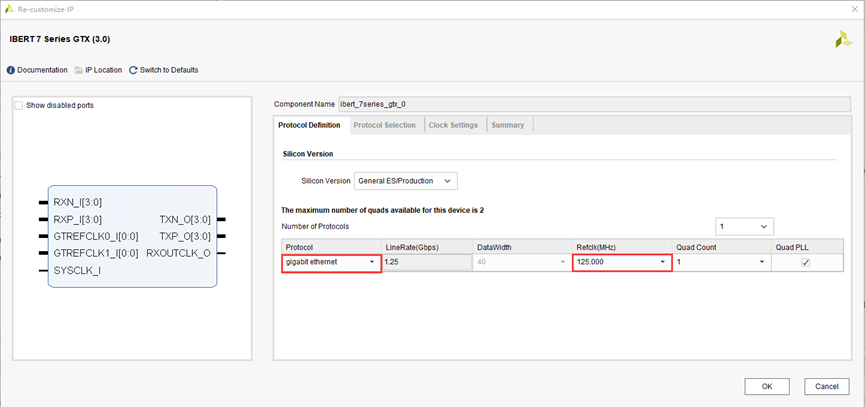

利用 IBERT 进行 GTX 信号眼图测试8.5.4.1 概述Vivado中提供了1种IBERT工具用于对Xilinx FPGA芯片的高速串行收发器进行板级硬件测试。通过IBERT我们可...

2021-07-20 07:28:23

和GTX收发器的动态重新配置端口属性,还包括通信逻辑,以允许设计在运行时通过JTAG进行访问。

IBERT工具用于对Xilinx FPGA芯片的高速串行收发器进行板级硬件测试。通过IBERT可以获取误码率

2023-06-21 11:23:12

Synchronous DRAM(SDRAM)嵌入式高速双接口存储器(dual port SRAM/FIFO Block )(真双端/伪双端)内置多个18×18/9×9可串行乘法器以及算术逻辑单元

2020-06-03 09:32:14

FPGA与专用芯片(比如AD/DA)之间的高速LVDS数据传输.本人非常熟悉AD接口,包括高速并行AD、串行AD,比如ADS5474,LTC2175,E2V高速AD等,基于FPGA设计高速并行/串行

2014-03-01 18:47:47

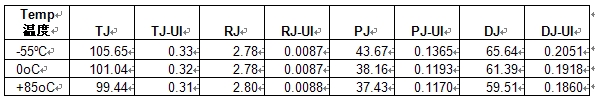

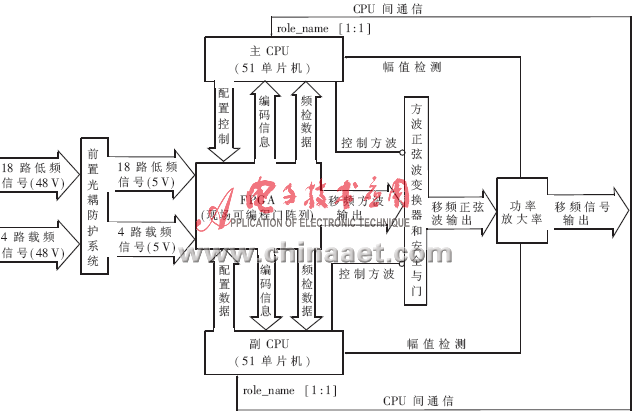

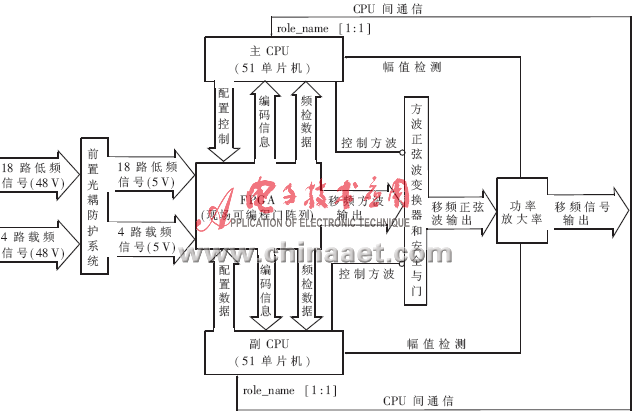

的输入输出接口设计就显得尤为重要。1 高速采集系统介绍 数据采集系统原理框图如图1所示,输入的中频信号经A/D采样电路采样后,转换成LVDS信号送入FPGA中,或通过FPGA的端口RocketIO从高速接口

2018-12-18 10:22:18

基于FPGA的通用高速串行互连协议设计基于FPGA的通用高速串行互连协议设计

2012-08-11 15:46:52

基于DSP和FPGA的高速串行通信系统设计

2015-03-16 15:47:04

多FPGA系统中自定义高速串行数据接口设计.pdf

2011-03-21 17:28:15

多FPGA系统中自定义高速串行数据接口设计为方便多FPGA系统中主从FPGA之间的命令与数据传输,节省连接的引脚数量,设计了一种基于FPGA的自定义高速串行数据传输模块。对主从串行模块进行了详尽

2012-08-11 11:49:57

并对FPGA进行编程,但由于我的外部TX源,我无法生成二维眼图。是否可以在不使用环回功能的情况下使用IBERT 3.0获取眼图?

2020-05-22 10:18:07

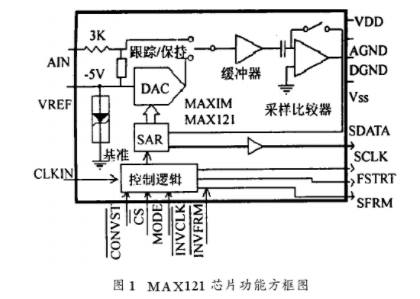

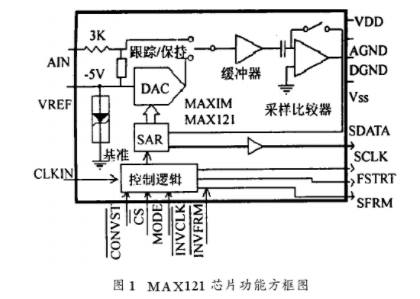

如何实现MAX121在高速串行接口电路的应用?MAX121芯片有何特点及性能如何?

2021-04-12 06:46:13

亲爱的大家,我希望将高速ADC与串行LVDS输出连接到virtex 7 fpga。我使用的ADC评估板是AD9635_125EBZ。我想知道如何将串行LVDS接口到FMC HPC。我对FPGA很陌生。问候,萨兰

2020-07-26 18:27:20

大家好。我正在使用XC6VSX315T。但我的SRIO无法正常工作。所以我试图用Ibert来测试我的FPGA。但是有一些问题。我已经测量了电压和clk。他们都没问题。可能是什么问题?请帮助我非常感谢你。

2020-06-19 10:06:58

本文在对Virtex-5 RocketIOTM GTP进行了解的基础上,针对串行高速接口开发中位宽不匹配的问题,提出了一种位宽转换方法,以解决Virtex-5 RocketI0TM GTP无法直接应用于某些串行高速接口开发的问题,并就SATA2.0接口开发中该问题的解决方案进行详细阐述。

2021-05-28 06:21:43

本文给出了基于FPGA高速数据采集系统中的输入输出接口的实现,介绍了高速传输系统中RocketIO设计以及LVDS接口、LVPECL接口电路结构及连接方式,并在我们设计的高速数传系统中得到应用。

2021-04-29 06:04:42

本文介绍了基于Xilinx Virtex-6 FPGA的高速串行数据传输系统的设计与实现,系统包含AXI DMA和GTX串行收发器,系统增加了流量控制机制来保证高速数据传输的可靠性。最后进行了仿真测试,测试结果显示系统可以高速可靠地传输数据。

2021-05-25 06:45:36

本文研究设计了一种基于高速隔离芯片的高速串行隔离型ADC。该数字隔离型ADC频带宽,延时小,稳定性高并且电路结构简单。利用FPGA作为控制器,很好地实现了模数转换和隔离传输。

2021-05-08 06:14:31

调整和演进,满足新设计的需要。 为什么需要高速转换器转FPGA串行接口 JESD204数据转换器串行接口标准由JEDEC委员会制定,旨在标准化并减少高速数据转换器与FPGA(现场可编程门阵列)等其它

2018-12-25 09:27:33

测试机。IBERT是针对高速串行接口的在线调试和验证。通过IBERT的检测,可以确认FPGA内部的高速串行口传输数据的可靠性和稳定性。JTAG-to-AXI Master,即JTAG-to-AXI主机

2019-05-24 15:16:32

用于高速数据转换器的串行接口有哪些选择?

2021-04-09 06:55:28

紫光的FPGA哪些系列支持高速接口?相关接口有哪些免费的IP可以使用呢?性能怎么样?

2024-03-20 16:58:29

谁介绍一款FPGA出串行高速2711串行接口芯片

2015-05-25 10:41:52

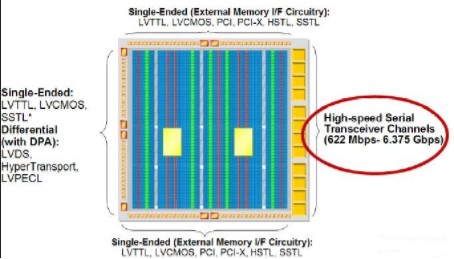

轻松实现高速串行I/OFPGA应用设计者指南输入/输出(I/O)在计算机和工业应用中一直扮演着关键角色。但是,随着信号处理越来越复杂,I/O通信会变得不可靠。在早期的并行I/O总线中,接口的数据对齐

2020-01-02 12:12:28

本文由Xilinx公司连接功能解决方案部市场营销经理Abhijit Athavale编写,针对FPGA高速串行I/O接口的实现进行了全面而详细的介绍,是FPGA设计人员不可多得的专业参考资料。

2020-01-28 08:45:42

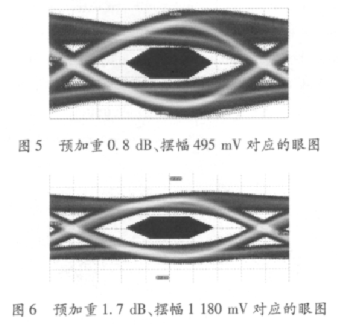

随着高速数字系统的发展,高速串行数据被广泛使用,内嵌高速串行接口的FPGA也得到大量应用,相应的高速串行信号质量的测试也越来越频繁和重要。通常用示波器观察信号波形、眼图、抖动来衡量信号的质量

2019-09-23 07:00:49

的高性能FPGA计算加速卡。作为基于服务器的PCI Express数据采集、处理、存储设备,该板卡可以实现2通道万兆光纤网络数据的高速采集、实时处理、实时记录和宽带回放,强大的FPGA处理性能,可以实现

2016-03-04 11:13:54

的高性能FPGA计算加速卡。作为基于服务器的PCI Express数据采集、处理、存储设备,该板卡可以实现2通道万兆光纤网络数据的高速采集、实时处理、实时记录和宽带回放,强大的FPGA处理性能,可以实现

2016-03-11 11:07:39

的高性能FPGA计算加速卡。作为基于服务器的PCI Express数据采集、处理、存储设备,该板卡可以实现2通道万兆光纤网络数据的高速采集、实时处理、实时记录和宽带回放,强大的FPGA处理性能,可以实现

2016-03-18 11:16:02

的高性能FPGA计算加速卡。作为基于服务器的PCI Express数据采集、处理、存储设备,该板卡可以实现2通道万兆光纤网络数据的高速采集、实时处理、实时记录和宽带回放,强大的FPGA处理性能,可以实现

2016-03-25 11:34:03

的高性能FPGA计算加速卡。作为基于服务器的PCI Express数据采集、处理、存储设备,该板卡可以实现2通道万兆光纤网络数据的高速采集、实时处理、实时记录和宽带回放,强大的FPGA处理性能,可以实现

2016-04-01 10:53:42

的高性能FPGA计算加速卡。作为基于服务器的PCI Express数据采集、处理、存储设备,该板卡可以实现2通道万兆光纤网络数据的高速采集、实时处理、实时记录和宽带回放,强大的FPGA处理性能,可以实现

2016-04-11 14:45:24

的高性能FPGA计算加速卡。作为基于服务器的PCI Express数据采集、处理、存储设备,该板卡可以实现2通道万兆光纤网络数据的高速采集、实时处理、实时记录和宽带回放,强大的FPGA处理性能,可以实现

2016-04-18 14:12:57

的高性能FPGA计算加速卡。作为基于服务器的PCI Express数据采集、处理、存储设备,该板卡可以实现2通道万兆光纤网络数据的高速采集、实时处理、实时记录和宽带回放,强大的FPGA处理性能,可以实现

2016-04-27 11:51:14

本文介绍了一种应用FPGA 器件完成高速数字传输的方法,利用这种方法实现无线收发芯片nRF2401A 的高速数据接口。为进一步提高信息的传输速率,这里还对待传输的数据进行了压缩处

2009-08-04 09:16:20 9

9 为了使计算机能够通过串口控制FPGA 的输出信号,笔者根据异步串行通信的原理,设计了简便易行的FPGA 串行通信接口系统,并应用VHDL 语言在FPGA 内部集成了串行接收模块,具有较强

2009-09-24 15:52:56 18

18 串行接口常用于芯片至芯片和电路板至电路板之间的数据传输。随着系统的带宽不断增加至多吉比特范围,并行接口已经被高速串行链接,或SERDES (串化器/ 解串器)所取代。起初

2010-02-25 23:03:44 38

38 本文探讨了BRDF测量系统中利用串行接口芯片EZ-USB FX2实现PC机与光谱仪之间的高速串行通讯。给出了系统组成原理,USB接口芯片EZ-USB FX2 CY7C68013的功能介绍和基于“Slave FIFOs”方式实现

2010-08-03 11:15:14 11

11 摘 要:介绍了FPGA最新一代器件Virtex25上的高速串行收发器RocketIO。基于ML505开发平台构建了一个高速串行数据传输系统,重点说明了该系统采用RocketIO实现1. 25Gbp s高速串行传输的设

2010-09-22 08:41:18 44

44 FPGA硬件系统的调试方法

在调试FPGA电路时要遵循一定的原则和技巧,才能减少调试时间,避免误操作损坏电路。一般情况下,可以参考以下步骤进行

2010-02-08 14:44:42 3102

3102 高速串行接口设计的高效时钟解决方案

数字系统的设计师们面临着许多新的挑战,例如使用采用了串行器/解串器(SERDES)技术的高速串行接口来取代传统的并行总线架

2010-04-09 13:24:59 1349

1349

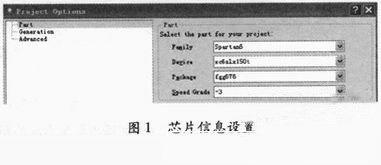

根据可编程串行接口芯片8251A标准及功能,划分其功能模块,使用ISE和Modelsim软件,利用VHDL语言完成了8251A的逻辑设计、功能仿真、综合实现和布局布线,使用ISE的iMPACT工具将生成的配置

2011-12-28 10:32:41 62

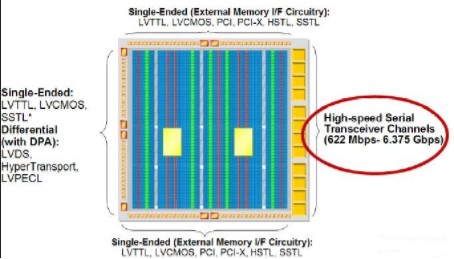

62 Xilinx收发器调试工具,可支持312.5Mbps至12.5Gbps的JESD204B数据转换器至FPGA串行数据接口和Xilinx® Inc., 7系列FPGA及Zynq®-7000全可编程SoC。

2013-10-17 16:35:20 1258

1258 多FPGA系统中自定义高速串行数据接口设计

2016-05-10 11:24:33 24

24 基于FPGA的高速数据采集系统接口设计.

2016-05-10 17:06:40 27

27 基于FPGA的通用高速串行互连协议设计。

2016-05-11 09:46:01 18

18 高速串行接口链路层的电路设计与实现

2017-01-19 21:22:54 12

12 设计周期中最困难的流程。此外,几乎当前所有的像CPU、DSP、ASIC等高速芯片的总线,除了提供高速并行总线接口外,正迅速向高速串行接口的方向发展。FPGA也不例外,每一条物理链路的速度从600Mbps到

2018-07-19 14:19:00 14271

14271

XC5LX50T为例,这款FPGA集成了一个PCIE的Endpoint以及12个可以支持6 Gb/s以上的高速串行接口模块,支持串行RapidIO、fiber channel以及其他多种串行协议。

2018-07-20 11:42:00 2009

2009

本文主要介绍了基于FPGA的串行A/D转换模块设计,tcl594以8位开关电容逐次逼近A/D转换器为基础而构造的CMOSA/D转换器,用Xilinx公司的FPGA芯片XC3S250ETQG144

2017-12-19 10:48:26 7160

7160

许多 FPGA 设计都采用高速存储器接口,可能调试比较困难,不过只要采用正确的方法就能成功进行调试。 现代 FPGA 通常连接高速 SRAM 和 SDRAM 存储器 。要确保这种器件无差错运行,调试

2018-01-12 11:48:44 1662

1662

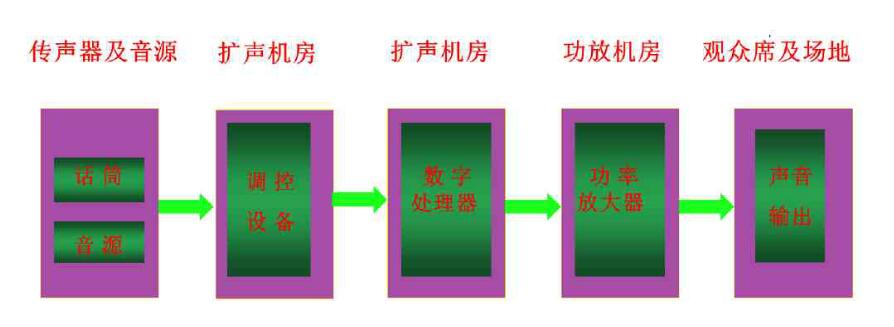

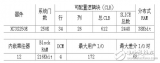

本文首先介绍了扩声系统的基本组成结构,其次介绍了影响扩声系统调试六大因素,最后介绍了扩声系统调试的详细步骤。

2018-05-24 16:36:03 12808

12808

随着高速数字系统的发展,高速串行数据被广泛使用,内嵌高速串行接口的FPGA也得到大量应用,相应的高速串行信号质量的测试也越来越频繁和重要。通常用示波器观察信号波形、眼图、抖动来衡量信号的质量

2018-11-29 09:33:00 4803

4803

随着FPGA的设计速度和容量的明显增长,当前流行的FPGA芯片都提供高速总线,例如DDR内存总线,PCI-X总线、SPI总线;针对超高速的数据传输,FPGA通过集成SerDes提供高速串行IO,支持各种诸如PCI-E、GBE、XAUI等高速串行总线协议,为各种不同标准的高速传输提供极大的灵活性。

2019-07-23 08:09:00 5767

5767

了解使用Vivado 2016.3中引入的系统内IBERT进行调试的好处,以及将其添加到设计中所需的步骤。

2018-11-20 06:43:00 6397

6397 来自OFC 2015的Xilinx Alliance成员演示,重点介绍了与Xilinx UltraScale FPGA接口的MoSys带宽引擎2高速串行存储器IC。

2018-11-29 06:37:00 3530

3530 通过Virtex-7 2000T FPGA中的GTX收发器实现高速串行性能。

2018-11-22 06:27:00 4389

4389 随着FPGA在数据中心加速和Smart NIC在SDN和NFV领域的广泛应用,基于以太网接口的FPGA开发板越来越受到关注。而更高速率的以太网接口技术则是应用的关键,本文将详细介绍基于FPGA的10G以太网接口的原理及调试技术。

2019-03-03 10:52:49 19155

19155

本次研讨会视频将从原始版本到现在的“B”版本简要介绍JESD204标准。此外,还将介绍与JESD204等高速串行接口相关的常见“高性能指标”。研讨会中涉及的话题也适用于使用类似高速串行接口的应用。

2019-07-05 06:19:00 3759

3759 在数字系统互连设计中,高速串行/O技术取代传统的并行/O技术成为当前发展的趋势。与传统并行丨/技术相比,串行方案提供了更大的带宽、更远的距离、更低的成本和更高的扩展能力,克服了并行l/O设计存在的缺陷在实际设计应用中,采用现场可编程门阵列FPGA实现高速串行接口是一种性价比较高的技术途径。

2020-08-24 17:28:00 15

15 FPGA概述FPGA调试介绍调试挑战设计流程概述■FPGA调试方法概述嵌入式逻辑分析仪外部测试设备■使用 FPGAVIEW改善外部测试设备方法■FPGA中高速O的信号完整性测试和分析

2020-09-22 17:43:21 12

12 高速反串行板(HSDB)/(HSC-ADC-FPGA)

2021-04-15 20:06:27 10

10 IBERT(Integrated Bit ErrorRatio Tester,集成误比特率测试工具),是Xilinx提供用于调试FPGA高速串行接口比特误码率性能的工具,最常用在GT高速串行收发器测试

2021-04-27 16:10:45 9248

9248

介绍了MAXIM系列芯片MAX121的工作性能与特点,具体给出了MAX121芯片在数字信号处理集 成电路(cc)高速串行接口电路的

2021-05-12 16:09:59 7369

7369

ADC和DAC是FPGA与外部信号的接口,从数据接口类型的角度划分,有低速的串行接口和高速的并行接口。FPGA经常用来采集中高频信号,因此使用并行ADC和DAC居多。本文将介绍如何使用FPGA驱动并行ADC和并行DAC芯片。

2022-04-21 08:55:22 8245

8245 电子发烧友网站提供《TIDA 00133高速串行视频接口参考设计.zip》资料免费下载

2022-09-05 15:09:56 4

4 IBERT(Integrated Bit ErrorRatio Tester,集成误比特率测试工具),是Xilinx提供用于调试FPGA高速串行接口比特误码率性能的工具,最常用在GT高速串行收发器测试

2023-06-21 11:29:12 5571

5571

串行接口常用于芯片至芯片和电路板至电路板之间的数据传输。随着系统带宽不断增加至多吉比特范围,并行接口已经被高速串行链接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是独立

2023-07-27 16:10:01 4205

4205

本文介绍一个FPGA开源项目:基于IBERT的GTX数据传输测试。IBERT是指误码率测试,在Vivado软件中,IBERT 7 Series GTX IP核可用于对 Xilinx FPGA芯片

2023-08-31 11:45:30 4509

4509

应用领域,例如通信、嵌入式系统以及科学研究等等。 一个FPGA芯片通常具有许多不同类型的接口,以满足不同的需求。在这篇文章中,我们将讨论几个常见的高速接口类型,包括PCIe、DDR、Gigabit以太网

2023-12-07 17:27:29 4774

4774 FPGA(现场可编程门阵列)和DSP(数字信号处理器)之间通过SRIO接口进行调试通常需要以下步骤。

2024-04-19 11:48:46 2569

2569 随着信息技术的飞速发展,高速数据传输已成为现代通信和数据处理系统的核心。高速串行收发器(High-Speed Serial Transceiver)作为实现高速数据传输的关键部件,其性能优劣直接影响到整个系统的性能。本文将对高速串行收发器的原理进行详细介绍,并探讨其芯片设计的关键技术和挑战。

2024-05-16 16:54:38 2784

2784 高速串行通信的“高速”一般比较高,基本至少都会上G。如果利用FPGA内部的LUT、触发器和普通IO是无法满足这样高的输入输出速率的。

2024-08-05 11:12:59 2243

2243

Ratio Tester),集成误码率测试仪,它可以利用FPGA内部资源,评估检测FPGA中GTX的通断和通信性能。一般的误码率可以算到十的负十二次方级别。 这里暂时不介绍IBERT具体的生成过程,因为只是

2024-12-20 09:38:26 3744

3744

ADC和DAC是FPGA与外部信号的接口,从数据接口类型的角度划分,有低速的串行接口和高速的并行接口。FPGA经常用来采集中高频信号,因此使用并行ADC和DAC居多。本文将介绍如何使用FPGA驱动并行ADC和并行DAC芯片。

2025-03-14 13:54:12 1979

1979

高速串行接口(如PCIe、以太网、HDMI等)是芯片设计的“高速公路”,但调试过程却常让人抓狂——信号质量差、误码率高、眼图模糊……耗时耗力的测试流程,是否让你无数次想对屏幕喊“太难了”?

2025-05-30 14:30:50 890

890

Xilinx FPGA因其高性能和低延迟,常用于串行通信接口设计。本文深入分析了Aurora、PCI Express和Serial RapidIO这三种在Xilinx系统设计中关键的串行通信协议。介绍了它们的特性、优势和应用场景,以及如何在不同需求下选择合适的协议。

2025-11-14 15:02:11 2357

2357

电子发烧友App

电子发烧友App

评论