一、前言

IBERT(Integrated Bit Error Ratio Tester),集成误码率测试仪。作为用户来说可以使用这个工具对自己设计的板子中的高速串行收发器进行简单测试,从而判断设计的接口是否有问题。因为这个工具是直接集成到FPGA上,这样一来直接使用这个工具来测试高速接口就方便很多了,它只需要JTAG和测试接口用的连接线就能完成对板子的测试。

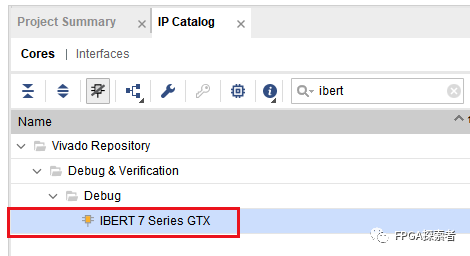

二、IBERT配置

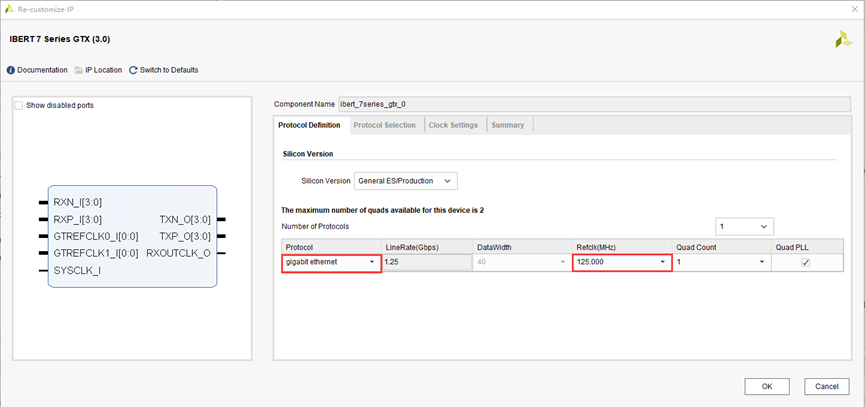

使用ibrt时主要时例化时对各个参数进行配置,本节将顺应IP的配置顺序对各个配置参数进行介绍。在对4个配置页面进行介绍之前,先对component name进行说明,这个就是ip的定义名字,可以有字母数字下划线组合而成,下划线不能再最前面。

2.1 协议定义

协议是线速/数据宽度/参考时钟速率的组合。一个 IBERT 内核最多可以定义三个协议,并且可以将任意数量的可用 Quad 指定为定义的任何协议。

Silicon Version:选择“常规 ES/产品”或“初始 ES”按钮以匹配目标芯片,这两者的区别暂时还没弄清楚,一般来说使用过程中默认选第一个。

Number of Protocols:选择协议的数量, 一个IBERT 最多可定义三个协议。

Protocol:在Protocol框中,选择自定义(custom)或其他预定义协议。如果为自定义,需要在linerate框中输入线速率(如果超出允许的范围,则线速率以红色文本显示)。

LianRate(Gbps):线速率,单位为吉比特每秒。可以根据要求选择自定义值,也可以从预先提供的行业标准协议(例如,CPRI、千兆以太网或 XAUI)中进行选择。

DataWith:选择数据的位宽。

refclk(Mhz):参考时钟频率,单位为兆赫兹。GT收发器的参考时钟。

Quad Count:再参考时钟频率下运行的Quad数量。一个Quad对应四个channel。

Quad PLL:Quad的时钟单元,默认情况下,Quad PLL 处于选中状态。要改为选择 CPLL,可以取消选中 QPLL 复选框。Xilinx建议在高于 6.5 Gb/s 的线速率下使用 QPLL,可以为 0.6 Gb/s 至 6.5 Gb/s 范围内的每个线速选择 QPLL或者CPLL。

2.2 协议选择

GTH location:将显示器件/封装组合中可用的Quad。

Protocol Selected:将要测的Quad分配给特定协议。

Refclk Selection:参考时钟输入的合法选择列在 REFCLK 选择组合中,这里需要结合原理图确定是选择MGTREFCLK0还是MGTREFCLK1,以及是否选择相邻的南北两个Quad的参考时钟作为本Quad的参考时钟。

TXUSRCLK Source:将 Quad 分配给协议后,将启用 TXUSRCLK 驱动源组合会被使能。TXUSRCLK 在 Quad 中的所有四个通道之间共享,因此需要确认组合中 TXOUTCLK 中的哪一个通道应用于用户时钟。

2.3 Clock Settings

Add RXOUTCLK Probes:如果需要,接收器时钟探头使能功能可从任何串行收发器中提取恢复的时钟。启用后,会出现一个新面板,可以在其中填写串行收发器源和探针标准。在“时钟设置”选项卡中,单击“添加RXOUTCLK探头”,Quad lane0 驱动输出引脚或引脚对。需要从列表中选择 I/O 标准并分配有效的引脚位置。

Systom clock:IBERT内核需要一个自由运行的系统时钟,用于通信和内核中包含的其他逻辑。选择 I/O 标准、有效引脚位置和频率以完成系统时钟设置。或者,也可以选择任何启用的Quad参考时钟。为了使内核正常工作,当FPGA配置为IBERT内核设计时,该系统时钟源必须保持工作和稳定。如果系统时钟的运行速度超过150 MHz,则会使用混合模式时钟管理器(MMCM)在内部对其进行分频,以满足时序限制。xilinx推荐选择外部时钟源来驱动系统时钟 。

注:在我自己的使用过程中选择了一个Quad的参考时钟作为系统,结果在vivado hardware 下始终不会出现IBERT,导致无法观测误码率,最终选择板上晶振作为IBERT时钟IBERT才被探测到,而后发现最初为其选择参考时钟为系统的哪个Quad则是无法link上。因此如Xilinx的推荐一样,最好选择外部时钟源来驱动IBERT的系统时钟。

2.4 Summary

回顾总结之前配置的内容。

三、IBRT使用

在完成好IP的设置之后,可以在工程下看到综合好的IP模块,单击右键点击open IP example design即可获得基于该IP生成的示例工程。直接生成比特然后下载到板子上即可。

工程下载完成后,在vivado hardware manager中便会显示IBRT的内容,下下方也会出现serial I/O Links以及serial I/O Scans页面,在IBERT上右键创建Links或者直接在serial I/O Links点击+号添加links。

3.1 serial I/O Links

在serial I/O Links页面中可以看见详细的链路信息。

Status:链路传输速率,如果为建链成功会显示No Link,建链不成功多半时时钟不对,以及PCB的问题。.当检查器连续五个周期接收到没有错误的数据时,就会断言LINK信号(显示线速率)。如果 LINK 信号被置位,并且检查器连续收到五个带有数据错误的周期,则 LINK 信号将被取消置位(显示No Link)。

Bits:探测到的比特数量。

Error:错误的比特数量。

BER:误码率,bit error ratio。

Reset:如果更改了serial I/O Links中的某些配置,需要reset下一重新进行检测。

TX/RX Pattern:测试时的伪随机码(PRBS),接收端需要校验发送端发送的数据是否正确的来计算误码率,故需要Tx和Rx的伪随机码一致。

TX Pre-Cursor:TX 预加重,用于改善信号传输质量的参数,可以修改参数获取最优质量链路。

TX Post-Cursor:TX后加重,用于改善信号传输质量的参数,可以修改参数获取最优质量链路。

TX Diff Swing:用于改善信号传输质量的参数,可以修改参数获取最优质量链路。

DFE Enabled:收发器的Rx接收端的均衡器的使能信号,勾选有利补偿信号在信道传输中的损失。

Inject Error:可以在测试过程中注入错误,可以模拟真实情况下有可能遇到的各种影响。

TX/RX Reset:发送端和接收端各自单独的复位。

RX/TX PLL Status:显示locked即表示可以进行测试,如果显示其他则说明对应的参考时钟设置或参考时钟的管脚约束有问题,需要重新设置。

Loopback Mode:主要五个选项,分为近端、远端的PCS和近端、远端PMA回环,以及none。如果选择none,则Tx端的码流将会输出,根据自行外部连接线再输入到Rx端去,选择外部连接一定要注意连接情况。

3.2 serial I/O Scans

serial I/O Scans用来生成GT链路的眼图,可以在serial I/O Links页面中右键添加scan以产生眼图,也可以在serial I/O Scans页面添加。

眼图的横坐标为-0.5到0.5,表示一个数据的数字周期。

除了单次查看眼图判断信道质量,还可以选择sweep的方式来设置多组不同的参数生成眼图的方式,这样就可以获取最佳预加重参数,这样一来在此后的接口设计当中就可以使用到这样的一组参数,以此提供信号传输的质量。

-

收发器

+关注

关注

10文章

3840浏览量

111489 -

眼图

+关注

关注

1文章

76浏览量

21817 -

误码率

+关注

关注

1文章

26浏览量

14489 -

Vivado

+关注

关注

19文章

860浏览量

71428

原文标题:【vivado】 IBERT GT收发器误码率测试

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

是德科技全新多通道比特误码率测试仪

基于FPGA的误码率测试仪的设计与实现

IP集成式误码率测试器(IBERT)的主要性能和优势介绍

BER误码率 影响误码率的因素

误码率是指什么_误码率是怎么表示_怎么计算

关于ZC706评估板的IBERT误码率测试和眼图扫描详细分析

如何在DS2652x STC上使用误码率测试仪

ZC706评估板IBERT误码率测试和眼图扫描

IBERT GT收发器误码率测试实例

IBERT GT收发器误码率测试实例

评论