fpga高速接口有哪些

FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,可以实现高度定制的硬件功能。它在数字电路设计中扮演着重要的角色,可以用于各种应用领域,例如通信、嵌入式系统以及科学研究等等。

一个FPGA芯片通常具有许多不同类型的接口,以满足不同的需求。在这篇文章中,我们将讨论几个常见的高速接口类型,包括PCIe、DDR、Gigabit以太网和HDMI。

首先要提到的是PCIe(Peripheral Component Interconnect Express)接口。这是一种用于将外部设备连接到计算机系统的高速串行总线接口。PCIe接口在FPGA中广泛应用于扩展卡、图形显示和数据采集等领域。它具有高带宽、低延迟和可靠性的特点,适用于处理大量数据的应用。

DDR(Double Data Rate)接口是一种用于存储器控制器和外部存储器之间的高速通信接口。它允许FPGA与外部DDR存储器进行数据交换,提供了高带宽和低延迟的数据传输。DDR接口在许多应用中得到了广泛应用,如图像处理、数据存储和高性能计算等领域。

Gigabit以太网是一种用于局域网(LAN)和广域网(WAN)之间数据传输的标准化接口。它提供了高速数据传输和网络连接的能力,使得FPGA能够与其他设备进行通信。Gigabit以太网接口在嵌入式系统、通信设备和工业自动化等领域得到了广泛应用。

HDMI(High Definition Multimedia Interface)接口是一种用于高清视频和音频传输的数字接口。它被广泛用于显示设备,如电视、显示器和投影仪等。FPGA可以通过HDMI接口将图像和音频数据发送到显示设备,实现高清视频和音频的传输和显示。

除了上述提到的接口,还有许多其他类型的高速接口可用于FPGA。例如,串行接口如SATA(Serial ATA)和USB(Universal Serial Bus)可以用于数据存储和外设连接。I2C(Inter-Integrated Circuit)和SPI(Serial Peripheral Interface)等串行总线接口可以用于与传感器和其他外设进行通信。

此外,FPGA还可以通过各种通信接口,如UART(Universal Asynchronous Receiver/Transmitter)、CAN(Controller Area Network)和Ethernet等,与其他设备进行串行和并行通信。

总结起来,FPGA的高速接口种类繁多,每种接口都有其特定的应用领域和特点。PCIe、DDR、Gigabit以太网和HDMI是几个常见且重要的高速接口类型。随着科技的不断进步,我们可以预见未来将会有更多种类的高速接口出现,以满足不断增长的需求。通过合理选择和使用高速接口,我们能够充分发挥FPGA在各种应用中的潜力,并提升系统性能和功能性。

-

以太网

+关注

关注

41文章

6192浏览量

181563 -

DDR

+关注

关注

11文章

761浏览量

69566 -

FPGA芯片

+关注

关注

4文章

250浏览量

41121

发布评论请先 登录

适配MiSTer FPGA平台的开源MIDI接口板介绍

FPGA时序收敛的痛点与解决之道——从一次高速接口调试谈起

基于4片DSP6678+FPGA KU115 的VPX高速信号处理平台

基于AMD FPGA的HDMI2.1接口实现

Altera FPGA的Avalon MM总线接口规范介绍

如何利用XPIO构建并实现带有Strobe的高速接口设计

如何在智多晶FPGA上使用MIPI接口

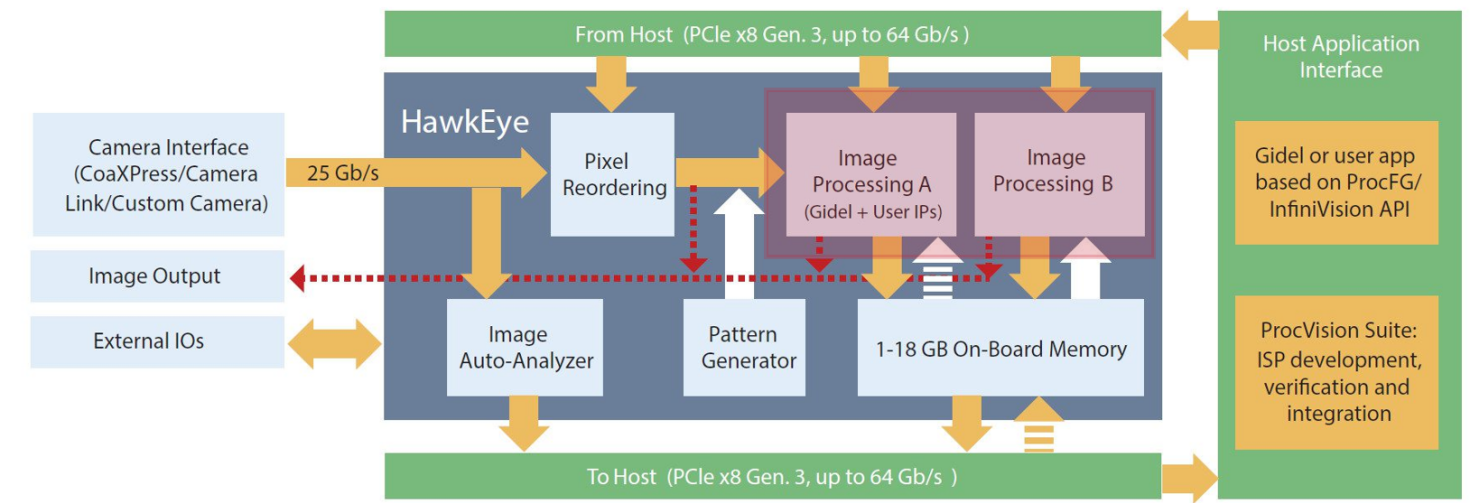

FPGA 加持,友思特图像采集卡高速预处理助力视觉系统运行提速增效

高速总线接口的类型介绍

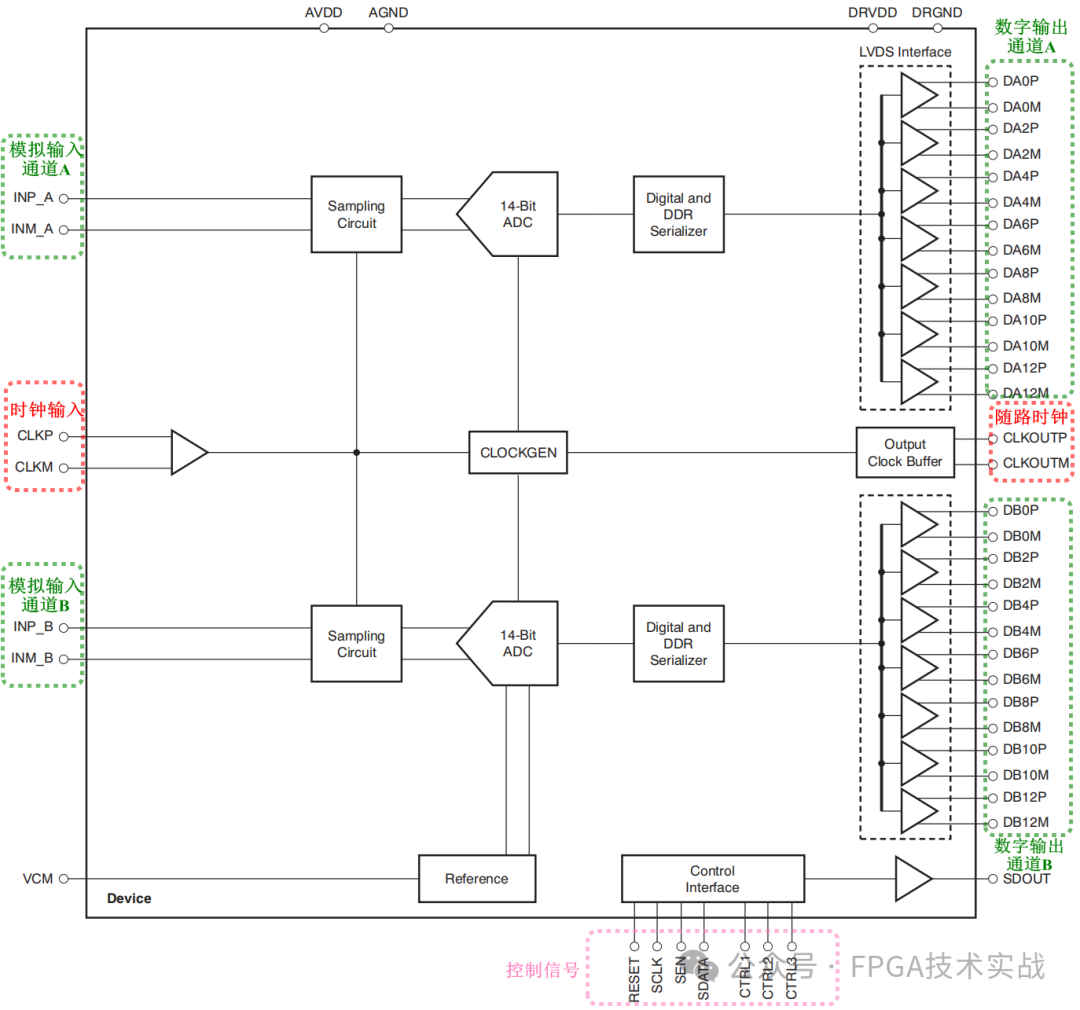

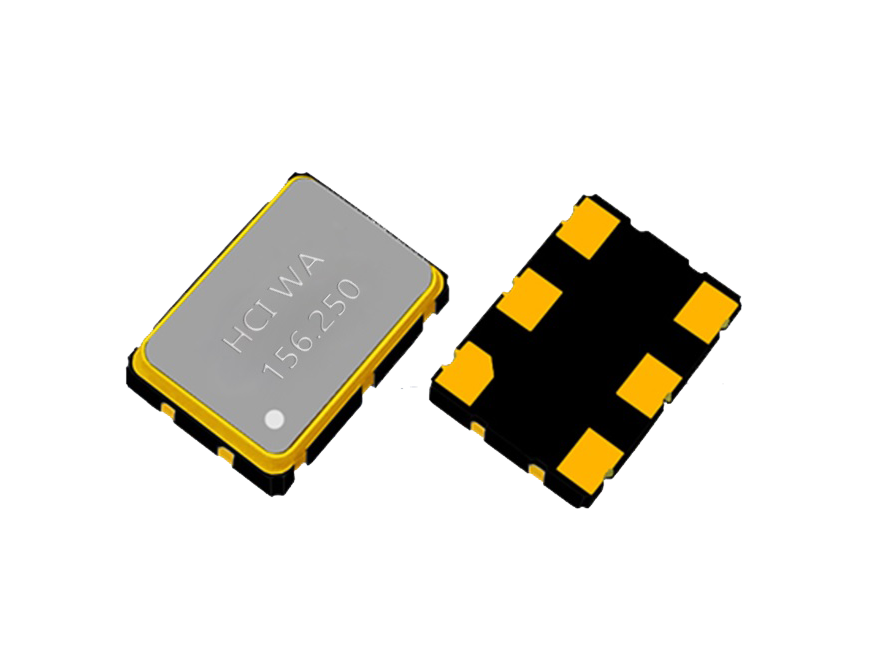

Altera FPGA与高速ADS4249和DAC3482的LVDS接口设计

FPGA从0到1学习资料集锦

FPGA的Jtag接口烧了,怎么办?

fpga高速接口有哪些

fpga高速接口有哪些

评论