前言

在调试MGT Bank的时候总会出现这样那样的问题,我们有时候会用到这个工具IBERT,那IBERT究竟是什么呢?

IBERT简介

IBERT(Integrated Bit Error Ratio Tester),集成误码率测试仪,它可以利用FPGA内部资源,评估检测FPGA中GTX的通断和通信性能。一般的误码率可以算到十的负十二次方级别。

这里暂时不介绍IBERT具体的生成过程,因为只是对IP核进行配置即可,下面大概描述下这个过程:

IBERT IP核生成及使用简介

在Vivado中IP catalog中搜索IBERT,如下:

开始定制IP核。

第一页:

第二页

第三页

注意第三页的系统时钟,有两种选择,可以选择外部时钟源,我这里选择的就是外部时钟源,由外部晶振直接提供,还可以选择第二项,使用GTX差分时钟:

定制完毕之后,打开Xilinx提供的例子程序:

之后我们的操作就在例子程序中进行,我们需要给MGT Bank提供时钟,GTX差分时钟,这个时钟也许需要我们在FPGA中配置时钟芯片等。我们的程序就在例子程序的顶层添加吧。

生成bitstream

上板子下载程序

之后是如下界面:

我们通过观察需要观察的GTX 通道的Status即可,还可以观察误码率:

FAR-End以及Near-End PCS/PMA

还有一个地方比较关键,有多个选择:

回环模式,可以选择的有:

正确选择了,如果你的MGT Bank没问题,状态就正常了:

这几种选择是什么意思呢?

Near-End PCS

Near-End PMA

Far-End PMA

Far-End PCS

其实我也没有必要多废话,就看数据手册里面讲的很清楚:

UG811有,UG476也有。

所谓的Near-End,以及Far-end代表的就是自己的FPGA的MGT和另外的FPGA的MGT。

而PCS以及PMA是MGT的物理层结构。

在博客:高速串行总线系列(3)GTX/GTH 物理层结构分析

以及UG476中都有讲。

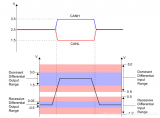

我们的TX用户接口的并行数据是先到PCS之后再到PMA的,而RX的接收到的串行数据先到PMA在到PCS。

中间存在串并转换,不在细讲。

由此可见,要做内部自回环以及外部自回环,都可以通过IBERT来实现。

当然还有一个选择None,也是外回环。

回环的过程是:

Traffic Generator产生数据通过TX发送出去,之后经过一系列路径,在由RX接收最终到达Traffic Checker,经过将发送的数据与接收数据对比,可以得到各种报告,包括眼图等。

补充

要做内回环也好,外回环也好,我们需要选择是那个通道发送以及那个通道接收,这就需要create link,可以选择该bank上的任意一个通道发送以及任意一个通道接收。当然还有一个最简单的办法,就是删了所有的link,点击auto link(类似这样的),Vivado会自动探测到那一路链接有通信。

通常都是X0Y6通道发,X0Y6通道收,类似如此,毕竟成双成对才是真理。

原文链接

https://gitcode.csdn.net/66ca084daa1c2020b359a016.html

-

FPGA

+关注

关注

1656文章

22288浏览量

630384 -

串行总线

+关注

关注

1文章

186浏览量

31519

原文标题:高速串行总线系列-IBERT 使用介绍

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

IBERT GT收发器误码率测试实例

Xilinx FPGA串行通信协议介绍

高速总线接口的类型介绍

智多晶XSBERT让高速串行接口调试化繁为简

如何用泰克MSO5系列混合信号示波器调试IoT和CAN总线

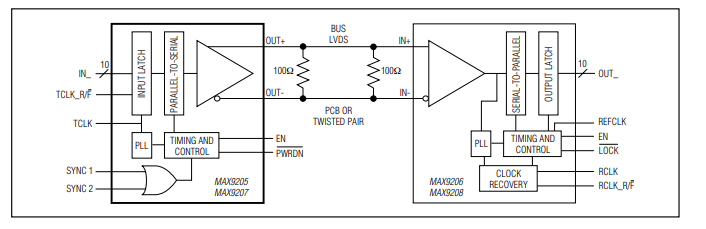

MAX9205/MAX9207 10位、总线LVDS串行器技术手册

NVMe简介之AXI总线

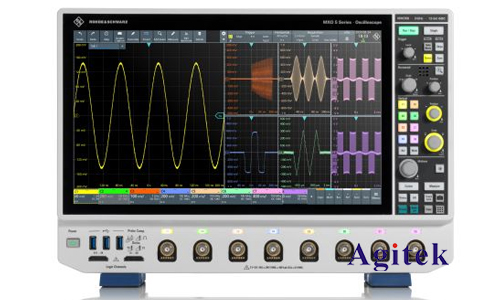

罗德与施瓦茨示波器高速总线测试

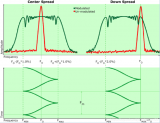

扩频时钟技术分享:SSC技术是什么、SSC对测试高速总线信号的影响

基于Xilinx的A7系列FPGA的CAN总线协议开发

高速串行总线系列-IBERT使用介绍

高速串行总线系列-IBERT使用介绍

评论