)、锁相环频率合成技术(PLL)、直接数字频率合成技术(DDS)、混合频率合成技术四种实现方式,其中锁相环频率合成器是射频电路中最常使用的一种结构,相比于其他几种结构,PLL结构能够在有限的功耗限制下合成高性能的载波信号。

2015-10-17 11:24:00 2785

2785

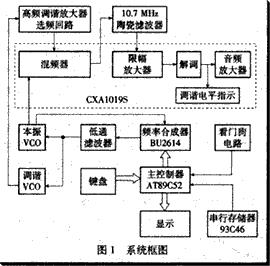

作为收音机重要组成部分的调谐电路和本振电路一直采用传统的电容、电感手动调台方式。近年来,随着无线电通信技术的迅速发展,锁相环和频率合成技术在各个领域得到了广泛的应用。由于锁相环具有跟踪特性、窄带滤波特性和锁定状态无剩余频差存在,因此在频率合成技术中采用锁相环路可以产生频率准确度很高的振荡信号源。

2018-12-21 08:50:00 8441

8441

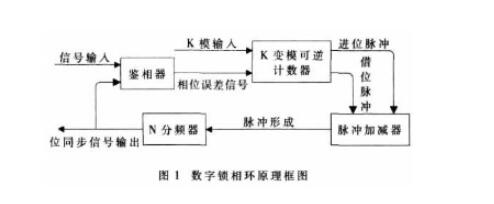

的问题进行了讨论。 引言 锁相环(PLL)技术在众多领域得到了广泛的应用。如信号处理,调制解调,时钟同步,倍频,频率综合等都应用到了锁相环技术。传统的锁相环由模拟电路实现,而全数字锁相环(DPLL)与传统的模拟电路实现的PLL相比,具有精度高

2018-10-25 09:17:13 9370

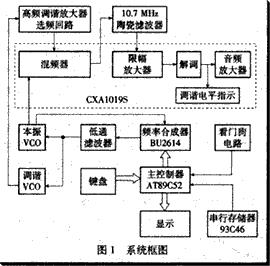

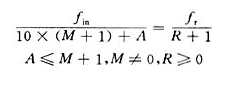

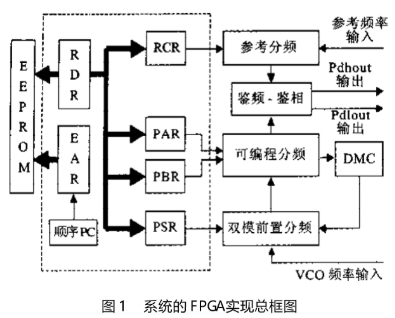

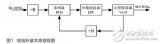

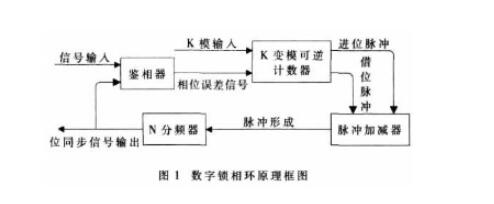

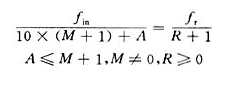

9370 数字锁相环频率合成系统的工作原理是:锁相环对高稳定度的基准频率(通常由晶体振荡器直接或经分频后提供)进行精确锁定,环内串接可编程的分频器,通过编程改变分频器的分频比,使环路总的分频比为N(可通过编程改变),从而环路稳定的输出 N倍的基准频率,而整个程序和系统的控制是要由CPU来完成的。

2020-07-23 16:47:49 2086

2086

大家都知道锁相环很重要,它是基石,锁相环决定了收发系统的基础指标,那么如此重要的锁相环选型原则有哪些呢?

2023-08-01 09:37:05 7303

7303

该文章是完全原创,用最简洁的语言讲清楚FPGA实现负反馈的精要。震撼!FPGA实现负反馈控制纯数字锁相环!.zip (225.26 KB )

2019-04-30 04:50:41

堆叠着鉴相、同相积分、中相积分、滤波等专用名词。这些概念距离硬件设计实现数字锁相环较远。Div20PLL Port(clock : in std_logic; --80M local clkflow

2012-01-12 15:29:12

数字锁相环设计源程序PLL是数字锁相环设计源程序, 其中, Fi是输入频率(接收数据), Fo(Q5)是本地输出频率.目的是从输入数据中提取时钟信号(Q5), 其频率与数据速率一致, 时钟上升沿锁定在数据的上升和下降沿上;顶层文件是PLL.GDF

2009-12-18 10:37:37

保证环路所要求的性能, 增加系统的稳定性。压控振荡器受滤波器输出的电压控制, 使得压控振荡器的频率向输入信号的频率靠拢, 也就是使差拍频率越来越低, 直至消除频率差而锁定。锁相环在开始工作时, 通常输入

2022-06-22 19:16:46

频率合成器的主要性能指标锁相环频率合成器原理锁相环频率合成器捕捉过程的分析与仿真

2021-04-22 06:27:35

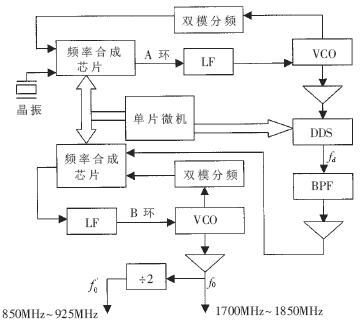

及可编程分频器三部分组成。其中可编程分频器是单片微机与锁相环之间的接口,同时也是组成数字锁相频率合成器的关键部件,在移动通信陆地电台等领域有着广泛的应用。</p><

2010-03-16 10:59:24

硬件锁相环和软件锁相环,这个很好理解,很多东西原来都是直接用硬件电路搞出来,现在有可编程器件了,再利用软件来实现。传统的硬件锁相环在如谐波、频率突变、相位突变等电压畸变以及三相电压不平衡情况下,很难

2015-01-04 22:57:15

ADI是高性能模拟器件供应商,在锁相环领域已有十多的的设计经验。到目前为止,ADI的ADF系列锁相环产品所能综合的频率可达8GHz,几乎能够涵盖目前所有无线通信系统的频段。ADF系列PLL频率合成

2018-11-06 09:03:16

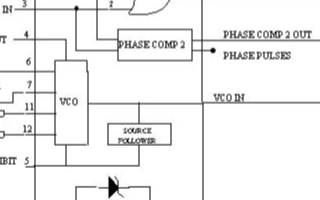

介绍了锁相环路的基本原理,分析了集成锁相环芯片ADF4106的工作特性,给出了集成锁相环芯片ADF4106的一个应用实例,为高频频率合成器的设计提供了很好的思路。 关键词:ADF4106,锁相环,频率合成器,环路滤波器

2019-07-04 07:01:10

全数字锁相环的设计及分析 1 引 言 锁相环是一种能使输出信号在频率和相位上与输入信号同步的电路,即系统进入锁定状态(或同步状态)后,震荡器的输出信号与系统输入信号之间相差为零,或者保持为常数

2010-03-16 10:56:10

HDL硬件描述语言对优化前后的算法进行了编码实现。仿真和实验结果表明,优化后的数字三相锁相环大大节省了FPGA的资源,并能快速、准确地锁定相位,具有良好的性能。关键词:FPGA;三相锁相环;乘法复用;CORDIC

2019-06-27 07:02:23

(DS)、锁相环频率合成技术(PLL)、直接数字频率合成技术(DDS)、混合频率合成技术四种实现方式,其中锁相环频率合成器是射频电路中最常使用的一种结构,相比于其他几种结构,PLL结构能够在有限的功耗限制

2018-09-06 14:32:13

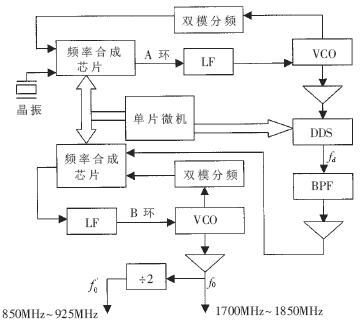

本文设计了一种多环锁相频率合成器。多环锁相环路有直接数字频率合成(DDS)环路和锁相频率合成环路(PLL)组成。充分利用两个不同环路的优点,既保证了高的输出频率,又得到了较高的频率分辨率。【关键词

2010-05-13 09:09:53

随着集成电路技术的不断进步,数字化应用逐渐普及,在数字通信、电力系统自动化等方面越来越多地运用了数字锁相环。它的好处在于免去了模拟器件的繁琐,而且成本低、易实现、省资源。本文综合以上考虑,在一片FPGA中以Quartus II为平台用VHDL实现了一个全数字锁相环功能模块,构成了片内锁相环。

2019-10-10 06:12:52

。本文结合FPGA技术、锁相环技术、频率合成技术,设计出了一个整数/半整数频率合成器,能够方便地应用于锁相环教学中,有一定的实用价值。那么有谁知道具体该如何利用FPGA设计PLL频率合成器吗?

2019-07-30 07:55:22

锁相环频率合成器是什么原理?基于CD4046的锁相环频率合成器的设计

2021-04-12 06:28:35

全数字锁相环由那几部分组成?数字锁相环的原理是什么?如何采用VHDL实现全数字锁相环电路的设计?

2021-05-07 06:14:44

控制用微处理器的主要性能有哪些?处理器在调频(FM)调谐器中的应用是什么?数字调谐系统有哪些性质?怎样去设计一种基于PLL(锁相环)合成器的数字调谐系统?

2021-08-17 07:03:36

fpga中的用锁相环产生时钟信号相比于用计数器进行分频有哪些优点,看fpga中锁相环的结构,其前期的输入信号和后期的输出信号不也是通过计数器进行分频实现的吗

2014-10-06 10:46:05

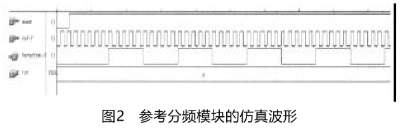

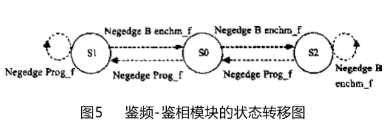

数字锁相环频率合成系统的工作原理CPU控制数字锁相环频率合成系统FPGA实现

2021-04-09 06:20:37

大家好,我的课题是要用FPGA做一个高精度锁相环。这个数字锁相环的工作原理为:正弦模拟信号通过低通滤波器后,经过模数转换器(ADC)转化为数字信号,与NCO(数控振荡器) 的输出信号相乘后滤波,从而

2016-08-15 11:31:56

驱动高压锁相环频率合成器电路的VCO

2021-01-11 06:02:04

用ad9850激励的锁相环频率合成器山东省济南市M0P44 部队Q04::00R 司朝良摘要! 提出了一种ad9850和ad9850相结合的频率合成方案! 介绍了ad9850芯片ad9850的基本工作原理" 性能特点及

2008-07-17 22:44:22 4

4 智能全数字锁相环的设计

摘要: 在FPGA片内实现全数字

2008-08-14 22:12:51 56

56 以TRAC020LH 完全可重配置模拟器件和TRAC 开发软件为基础,设计模拟锁相环;给出仿真结果和利用PIC 单片机对器件进行配置的应用电路。该锁相环成功应用于逆变器的频率跟踪,性能

2009-04-15 11:42:39 11

11 智能全数字锁相环的设计:在FPGA片内实现全数字锁相环用途极广。本文在集成数字锁相环74297的基础上进行改进,设计了锁相状态检测电路,配合CPU对环路滤波参数进行动态智能配

2009-06-25 23:32:57 72

72 基于FPGA的全数字锁相环设计:

2009-06-26 17:30:59 145

145

锁相环频率合成器:相位噪声问题和宽带循环:

In this chapter we locate the context of this thesis by introducing

2009-07-25 17:18:33 0

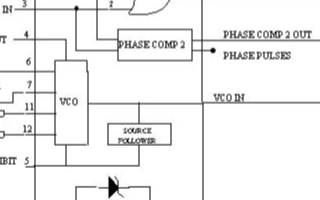

0 锁相环频率合成器(Motorola集成电路应用技术丛书):锁相环路设计基础,鉴相器,压控振荡器,程序分频器,前置分频器,单片集成锁相环路等内容。

2009-09-05 08:20:52 0

0 锁相环被广泛应用于电力系统的测量和控制中。介绍了一种新型的基于比例积分控制逻辑的全数字锁相环。通过对其数学模型的分析,阐述了该锁相环的各项性能指标与设计参数的

2010-07-02 16:54:10 30

30 本文介绍锁相环及其频率跟踪的基本原理,给出二阶锁相环和四阶锁相环的设计依据。在此基础上,对四阶锁相环实现频率跟踪的转换时间进行了仿真,就如何减小频率跟踪的转换时间

2010-07-29 16:28:14 44

44 锁相环的研究和频率合成一、实验目的:1. 振荡器(VCO)的V—f 特性的研究2. 对称波锁相环基本特性的研究3. 利用锁相环实现频率合成二、锁相环原理:

2009-03-06 20:02:52 2529

2529

实验五 数字锁相环与位同步

一、 实验目的

1. 掌握数字锁相环工作原理以及触发式数字锁

2009-04-01 09:27:45 6242

6242

介绍了锁相环路的基本原理,分析了集成锁相环芯片ADF4106的工作特性,给出了集成锁相环芯片ADF4106的一个应用实例,为高频频率合成器的设计提供了很好的思路。

2009-05-05 19:57:57 3047

3047

摘要: 在FPGA片内实现全数字锁相环用途极广。本文在集成数字锁相环74297的基础上进行改进,设计了锁相状态检测电路,配合CPU对环路滤波参数进行动态智

2009-06-20 12:39:32 1760

1760

宽频带数字锁相环的设计及基于FPGA的实现数字锁相环(DPLL)技术在数字通信、无线电电子学等众多领域得到了极为广泛的应用。与传统的模拟电路实现的

2009-11-23 21:00:58 1713

1713

单环锁相频率合成器,单环锁相频率合成器是什么意思

频率合成的历史

频率合成器被人们喻为众多电子系统的“心脏”。现代战争是

2010-03-23 11:36:28 1266

1266 集成锁相环频率合成器,什么是集成锁相环频率合成器

频率合成的历史

频率合成器被人们喻为众多电子系统

2010-03-23 11:45:44 956

956 数字锁相环(DPLL),数字锁相环(DPLL)是什么?

背景知识:

随着数字电路技术的发展,数字锁相环在调制解调、频率合成、FM 立体声解码、彩色副

2010-03-23 15:06:21 6110

6110 模拟锁相环,模拟锁相环原理解析

背景知识:

锁相技术是一种相位负反馈控制技术,它利用环路的反馈原理来产生新的频率点。它的主要

2010-03-23 15:08:20 6264

6264 锁相环路由于具有高稳定性、优越的跟踪性能及良好的抗干扰性,在频率合成中得到了广泛应用。但简单的锁相环路对输出频率、频率分辨率等指标往往不能满足要求,所以要对简单锁相环

2011-05-28 13:42:13 1355

1355

本文鉴于 数字锁相环 在实际应用中对信号频率的准确度和稳定度有较为严格的要求,设计一种应用于数字锁相环的数控振荡器(NCO,Number Controlled Oscillator)。基于直接数字频率合成(

2011-08-05 14:51:05 79

79 针对扩频通信系统的载波同步,提出一套完善的数字锁相环设计方案. 该方案利用新颖的可控根法完成1~3阶模拟锁相环(APLL)环路参数设计,并实现从模拟域到数字域的转换,得到的数字锁相

2011-08-26 16:10:38 122

122 叙述了MC14046 芯片的主要特点和功能,分析了用锁相环构成频率合成器的工作原理,介绍了一种用MC14046 构成的新型频率合成器。

2011-09-14 17:58:15 170

170 锁相环英文为PLL,即PLL锁相环。可以分为模拟锁相环和数字锁相环。两种分类的锁相环原理有较大区别,通过不同的锁相环电路实现不同的功能。

2011-10-26 12:40:28

为得到性能优良、符合实际工程的锁相环频率合成器,提出了一种以ADI的仿真工具ADIsimPLL为基础,运用ADS(Advanced Design System 2009)软件的快速设计方法。采用此方法设计了频率输出为

2013-01-10 16:50:36 81

81 基于FPGA的数字锁相环设计与实现技术论文

2015-10-30 10:38:35 9

9 Xilinx FPGA工程例子源码:用FPGA实现数字锁相环

2016-06-07 15:07:45 38

38 随着数字电路技术的发展,数字锁相环在调制解调、频率合成、FM 立体声解码、彩色副载波同步、图象处理等各个方面得到了广泛的应用。数字锁相环不仅吸收了数字电路可靠性高、体积小、价格低等优点,还解决了模拟

2017-09-12 16:54:55 0

0 一、设计目标 基于锁相环的理论,以载波恢复环为依托搭建数字锁相环平台,并在FPGA中实现锁相环的基本功能。 在FPGA中实现锁相环的自动增益控制,锁定检测,锁定时间、失锁时间的统计计算,多普勒频偏

2017-10-16 11:36:45 19

19 业界领先的射频、微波及毫米波产品供应商美国Pasternack公司推出一系列新型USB控制锁相环(PLL)频率合成器。在将信号完整性作为首要目标的射频和微波通信系统中,锁相环频率合成器可提供高频率

2018-04-26 11:16:00 1104

1104 锁相环路是一种反馈控制电路,简称锁相环(PLL,Phase-Locked Loop)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。

2019-09-20 07:05:00 4322

4322

随着集成电路技术的不断进步,数字化应用逐渐普及,在数字通信、电力系统自动化等方面越来越多地运用了数字锁相环。它的好处在于免去了模拟器件的繁琐,而且成本低、易实现、省资源。本文综合以上考虑,在一片FPGA中以Quartus II为平台用VHDL实现了一个全数字锁相环功能模块,构成了片内锁相环。

2020-07-16 09:16:08 3429

3429

锁相环路是一种反馈控制电路,简称锁相环( PLL)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。因锁相环可以实现输出信号频率对输入信号频率的自动跟踪, 所以锁相环通常

2020-08-06 17:58:25 26

26 本文提出了一种适用范围广泛的全数字锁相环(ADPLL)实现方法.在锁相环输入频率未知的情况下,实现锁相锁频功能。本文从全数字锁相环的基本实现方式入手.进行改进,并使用VH DL语言建模,使用FPGA进行验证。

2021-01-26 15:03:00 66

66 本文提出了一种适用范围广泛的全数字锁相环(ADPLL)实现方法.在锁相环输入频率未知的情况下,实现锁相锁频功能。本文从全数字锁相环的基本实现方式入手.进行改进,并使用VH DL语言建模,使用FPGA进行验证。

2021-01-26 15:03:00 20

20 CN-0369:低相位噪声的转换锁相环频率合成器

2021-03-20 13:21:15 7

7 锁相环路诞生于20世纪30年代。近年来,锁相技术在通信、航天、测量、电视、原子能、电机控制等领域,能够高性能地完成信号的提取、信号的跟踪与同步,模拟和数字通信的调制与解调、频率合成、滤波等功能

2021-03-31 11:59:11 6328

6328

UG-369:ADF4151锁相环频率合成器评估板

2021-04-19 20:14:47 6

6 UG-802:用于锁相环的ADF5355频率合成器评估

2021-04-25 12:23:05 4

4 UG-383:用于锁相环的ADF4159频率合成器评估

2021-05-10 13:26:06 2

2 UG-1087:用于锁相环的ADF5356频率合成器评估

2021-05-17 09:38:07 10

10 用锁相环实现超快频率切换

2021-05-18 20:29:01 9

9 UG-686:ADF4155锁相环频率合成器评估板

2021-05-25 16:46:51 4

4 所设计的频率合成器,要求相位噪声低,输出频率800~1 000 MHz,共88个波道,通过单片机发送的频率控制字进行波道选择。在对比各种大规模集成频率合成芯片性能的基础上,选用了单片大规模集成锁相环频率合成芯片PE3236作为核心电路,构成锁相式频率合成器。

2021-05-28 10:30:08 5925

5925

基于FPGA的宽频带数字锁相环的设计与实现简介说明。

2021-06-01 09:41:14 26

26 ADF4150HV锁相环频率合成器UG-406评估板

2021-06-03 11:16:33 10

10 基于FPGA的高性能全数字锁相环

2021-06-08 11:09:01 46

46 数字调谐系统是现代收发信机的核心,其性能直接影响通信质量的好坏,其主要部分是集成锁相式频率合成器。集成锁相环与微处理器结合,可由微机控制完成频率合成器的全部功能。

2021-06-14 17:29:00 5078

5078

锁相环(PLL)电路是由压控振荡器(VCO)和鉴相器组成的反馈系统,振荡器信号跟踪施加的频率或相位调制信号是否具有正确的频率和相位。需要从固定低频率信号生成稳定的高输出频率时,或者需要频率快速变化时,都可以使用PLL。典型应用包括采用高频率、电信和测量技术实现滤波、调制和解调,以及实现频率合成。

2022-06-13 16:14:35 5580

5580 锁相环的锁定是指锁相环的输出频率等于输入频率,而输出信号的相位跟随输入信号的变化而变化。

2023-01-31 16:31:12 4097

4097 模拟锁相环和数字锁相环的主要区别在于它们的控制方式不同。模拟锁相环是通过模拟电路来控制频率和相位,而数字锁相环是通过数字信号处理技术来控制频率和相位。此外,模拟锁相环的精度较低,而数字锁相环的精度较高。

2023-02-15 13:47:53 6625

6625 锁相环频率合成器的优缺点 锁相环频率合成器,又称为PLL(Phase Locked Loop),是一种广泛应用的电路,能够将输入信号的频率合成为电路所需要的频率,并且能够实现对信号的相位和频率

2023-09-02 14:59:33 3701

3701 锁相环是如何实现倍频的? 锁相环(Phase Locked Loop, PLL)是一种电路,用于稳定和恢复输入信号的相位和频率。它可以广泛应用于通信、计算机、音频等领域中。其中一个重要的应用就是

2023-09-02 14:59:37 5114

5114 如何调试锁相环频率合成器? 锁相环频率合成器(PLL)是电路中常见的一个模块,用于生成稳定的高精度频率信号。PLL的核心部分是相位检测器和环路滤波器,其主要工作原理是通过不断调整反馈回来的参考信号

2023-09-02 15:06:37 1899

1899 锁相环(Phase Locked Loop, PLL)是一种广泛应用于通信系统、频率合成、数字信号处理等领域的关键电路。本文将介绍锁相环的基本原理、分类及应用,以期帮助读者更好地理解和掌握这一技术。

2023-09-14 17:29:12 12300

12300 基本PLL锁相环、整数型频率合成器和分数型频率合成器。下面将详细介绍这三种模式的作用和特点。 第一种:基本PLL锁相环 基本PLL锁相环是PLLf工作的最基本形式,它主要由比较器、低通滤波器、VCO和分频器组成。其基本工作原理是将输入信号和VCO输出的信号进行

2023-10-13 17:39:48 5281

5281 比较,通过不断调整内部振荡器的频率,使得输出信号的相位与参考信号的相位保持一致,从而实现同步。锁相环广泛应用于数字通信、音频解码、数字信号处理等领域。 在锁相环的基本结构中,包含一个相位检测器、一个积分环节、一个低通滤波器和一个控制振荡器。参考

2023-10-13 17:39:53 3088

3088 软件锁相环在频率突变时锁不住 锁相环无法锁定怎么办? 锁相环(PLL)是一种用于在电路中生成稳定频率的技术。它是在1960年代开发的,并被广泛应用于通信、雷达、卫星技术等领域中。锁相环的主要作用

2023-10-13 17:39:58 3085

3085 电子发烧友网站提供《基于ADF4111的锁相环频率合成器设计.pdf》资料免费下载

2023-10-20 14:45:29 4

4 数字锁相环(DigitalPhase-LockedLoop,简称DPLL)是一种基于反馈控制的技术,用于实现精确的时序控制和相位同步。通过相位比较、频率差计算、频率控制、滤波和循环控制,它能够完成

2024-01-02 17:20:25 3358

3358

频率合成器和锁相环是两种常见的电子设备,用于生成稳定的频率信号。尽管它们的功能都是产生特定频率的信号,但它们在工作原理和应用方面有着明显的区别。

2024-02-27 18:22:59 2092

2092 锁相环频率合成器(Phase-Locked Loop Frequency Synthesizer, PLLFS)是一种利用锁相环(Phase-Locked Loop, PLL)技术实现频率合成的装置。其基本原理基于相位负反馈控制系统,通过调整输出信号的相位和频率,使其与参考信号的相位和频率保持同步。

2024-08-05 15:01:43 2292

2292 在现代电子系统中,频率控制和信号生成是至关重要的。锁相环(PLL)和频率合成器是实现这些功能的两种关键技术。尽管它们在某些应用中可以互换使用,但它们在设计、工作原理和应用领域上存在显著差异。 一

2024-11-06 10:46:53 1812

1812 锁相环(Phase-Locked Loop,简称PLL)是一种广泛应用于电子系统中的反馈控制系统,主要用于频率合成和相位同步。本文将从锁相环的工作原理、基本组成、应用案例以及设计考虑等方面进行详细阐述,以帮助读者全面理解这一重要技术。

2025-02-03 17:48:00 2319

2319

电子发烧友App

电子发烧友App

评论