作者:孟凡文,张玉香,胡连柱,王爱玲

1 前言

锁相环路诞生于20世纪30年代。近年来,锁相技术在通信、航天、测量、电视、原子能、电机控制等领域,能够高性能地完成信号的提取、信号的跟踪与同步,模拟和数字通信的调制与解调、频率合成、滤波等功能,已经成为电子设备中常用的基本部件之一。为了便于调整,降低成本和提高可靠性,目前已有多种不同性能的集成锁相环电路,主要分为模拟和数字两种。

数字锁相芯片4046结构简单,接线方便,功能扩展容易,在音频发生器设计、鉴相、频率合成、压频转换等方面获得广泛应用。本文利用4046的锁相和压控振荡原理,结合计数器的分频功能,并通过计数和译码显示测量不同汽缸汽车的转速。

2 数字锁相环4046的功能及在本设计中的应用

2.1 数字锁相环4046功能简介

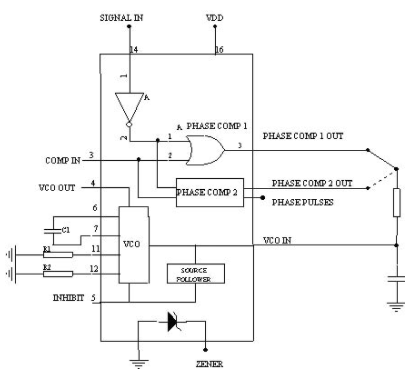

数字锁相环4046包含两个相位比较器,一个压控振荡器(VCO),一个源极跟随器和齐纳二极管。比较器有两个共用信号输入端,一个是输入信号端,一个是比较信号输入端,对于大幅值信号,可直接耦合到比较器输入端,对于小幅值信号,可通过电容耦合到放大器上,再送给信号输入端。

相位比较器1是一个或门,产生相位差信号(相位比较器1输出),并在压控振荡器的输出信号中心频率处保持90°相移不变。只要输入信号和比较信号(占空比都为50%)的相位差保持恒定,压控振荡器输出信号的中心频率就跟踪输入信号的频率,这也是锁相环锁相的本质。

相位比较器2是边缘触发的数字存储网络,产生相位差信号(相位比较器2输出)和锁定信号(相位脉冲输出),并在压控振荡器的输出信号中心频率处保持0°相移不变。只要输入信号和比较信号(与占空比无关)的相位差保持恒定,压控振荡器输出信号的中心频率就跟踪输入信号的频率。

压控振荡器(VCO)产生的信号从VCO OUT 输出,振荡频率由压控振荡器输入信号(VCO IN)和6、7管脚间的电容和11、12管脚上接的电阻共同确定,当外围参数确定后,振荡频率的大小与压控振荡器输入信号成线性关系。

源极跟随器通过外接10kΩ以上的电阻接地。当INHIBIT 输入端信号为高电平时,就会屏蔽压控振荡器和源极跟随器来减小功耗。齐纳二极管主要起稳压作用。

4046有以下主要特点:

(1) 较宽的电源电压范围(3.0~18V);

(2) 低功耗(70μA);

(3) 振荡频率高且稳定(1.3MHz);

(4) 频率温度漂移小;

(5) VCO输出线性好(《1%)。

2.1 数字锁相环4046在本设计中的应用

本设计中,传感器采集汽车打火系统中的电火花信号,此信号经过限幅、滤波、稳压,送给电压比较器的同相输入端,与反相输入端的恒定电压值进行比较,输出信号为矩形脉冲,高电平为运算放大器的电源电压值。经过处理后的信号送给数字锁相环4046的输入信号端口,采用4046的第二相位比较器,当输出信号(4管脚)的相位与输入信号的相位差恒定时,输出信号频率为输入信号频率的整数倍。频率大小取决于相位比较器的输出信号经低通滤波处理后的电压和6、7管脚间的电容和11、12管脚上外接的电阻的大小。

3 测量汽车转速的设计电路实现

对于4缸、6缸和8缸汽车发动机,为了得到统一的转速计算公式,需要对4046的输出信号进行不同的分频。对于4缸汽车发动机来说,4046的输出信号要经过6分频,对于6缸汽车发动机来说,4046的输出信号要经过4分频,对于8缸汽车发动机来说,4046的输出信号要经过3分频。而计数器具有分频功能,本设计中选用具有可变计数器功能的CMOS芯片4018。只要把4018芯片的6管脚接到1管脚DATA端,就构成6进制计数器,对输入时钟信号进行6分频;只要把4018芯片的4管脚接到1管脚DATA端,就构成四进制计数器,对输入时钟信号进行4分频;把第4和第5管脚经相与后再接到1管脚DATA端,就构成三进制计数器,对输入时钟信号进行3分频;采用一个多路开关就可实现对不同汽缸汽车的转速测量。

4046的输出信号经计数器计数,数据锁存后,送给译码电路,译码输出驱动共阴极发光二极管,直接显示测量结果。

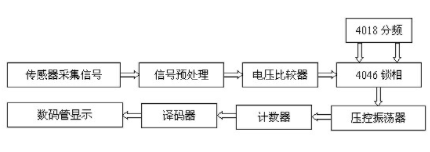

整个测量系统可用以下原理框图表示。

4 关键设计环节的仿真

本设计的关键环节是数字锁相环4046的锁相和压控振荡功能以及可变计数器4018的分频功能。电路设计与制版软件Protel 99内含一个功能强大的模/数混合信号仿真器,可进行瞬态分析, 显示电路节点的波形,从而验证设计的可行性。可利用此软件的仿真功能来分析4018和4046的功能以及在本设计中的应用。

4.1 4018的分频功能仿真

4.1.1 6分频的实现

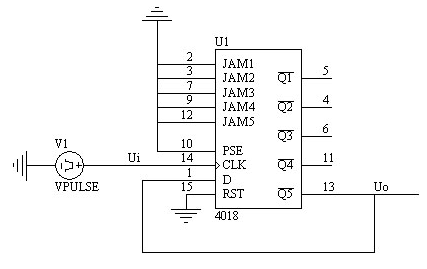

由以上分析可知道,只要把4018的6管脚输出接到1管脚DATA端,4018就成为六进制计数器,电路连接如图3所示。

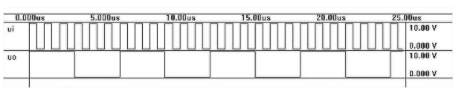

仿真时,在4018的时钟CLK端加上频率为1MHz的方波信号,观察输入信号Ui和输出信号Uo,波形图如图4所示,用软件所带测量光标测量两个信号的频率,Ui的频率恰为Uo的频率的6倍,用4018成功地实现了输入信号的6分频。

4.1.2 4分频与3分频的实现

只要把4018芯片的4管脚接到1管脚DATA端,就可对输入时钟信号进行4分频,把第4和第5管脚相与后再接到1管脚DATA端,就可对输入时钟信号进行3分频,相应的电路连接图和仿真波形不再赘述。

4.2 4046的锁相功能和压控振荡功能仿真

4.2.1 4046的锁相功能仿真

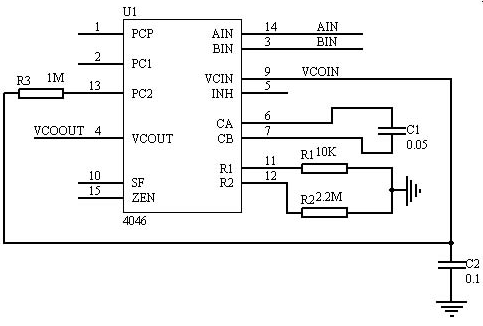

4046内部有两个相位比较器,本设计中使用相位比较器2,把信号输入端(14管脚)的信号与比较输入端(3管脚)的信号进行相位比较,将相位差转化为脉冲信号输出,此信号经过低通滤波器滤波,作为压控振荡器的输入信号,只要14管脚和3管脚的信号相位差恒定,压控振荡器的输入信号就为定值,压控振荡器的输出信号频率就为14管脚信号频率的倍数。实际电路连接图如图5所示。

图5中,经传感器采集并预处理过的信号从信号输入端(14管脚)输入,压控振荡器的输出信号(4管脚)经4018分频后反馈至比较信号输入端(3管脚),鉴相后的信号从相位比较器2(13管脚)输出,此信号经低通滤波处理后送给压控振荡器输入端(9管脚),输出信号频率由压控振荡器输入信号和6、7管脚间的电容C1和11、12管脚上的电阻R1、R2决定。

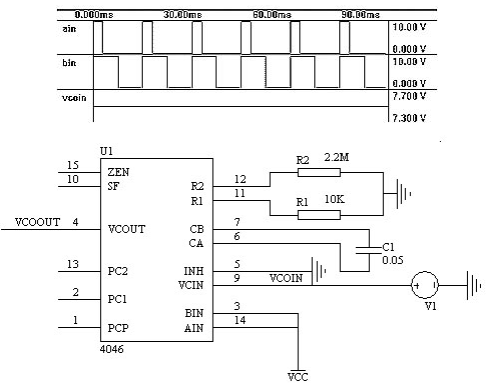

对4046的锁相功能进行仿真时,从14管脚输入频率为60Hz,高电平为电源电压(10V),占空比为1/4的矩形波信号,从3管脚输入频率为60Hz,高电平为电源电压(10V),占空比为1/2的矩形波信号,二者的相位差是恒定的,从相位比较器2输出的信号滤波后成为直流信号,送给压控振荡器输入端,相应的仿真波形图如图6所示。

由上图可以看出,当输入信号和比较信号的相位差保持恒定时,鉴相后的信号经低通滤波处理后为直流信号,此信号控制压控振荡器的输出信号频率。

4.2.2 4046的压控振荡功能仿真

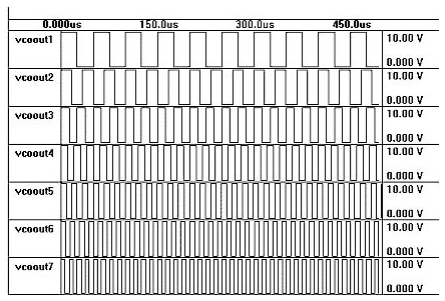

当外围参数确定后,4046的压控振荡器输出信号频率取决于VCO IN端的直流信号大小。通过设置不同的输入直流信号电压,观察输出信号波形。所采用的电路连接图如图7所示。

分别给VCO IN端加上1.0~7.0V的直流电压,观察VCO OUT端的输出信号波形,所得波形图如图8所示。

通过测量光标测量各输出信号的周期,再转换成频率,所得波形频率与输入直流电压的关系如表1所示。

通过以上波形显示和测量数据可以得出以下结论,压控振荡器的输出信号频率与输入电压具有很好的线性关系,输出信号频率超出音频范围。

5 结束语

本设计运用数字锁相芯片具有的锁相和压控振荡功能,产生高频振荡,驱动可变计数器进行不同分频,产生的与汽车转速成正比的信号经计数、译码后显示测量结果。配以合理的传感器采集信号,可用于不同汽缸的汽车转速的测量,具有一定的实用价值和应用前景。

责任编辑:gt

-

芯片

+关注

关注

462文章

53537浏览量

459148 -

二极管

+关注

关注

149文章

10310浏览量

176469 -

汽车电子

+关注

关注

3043文章

8558浏览量

172236

发布评论请先 登录

CD4046锁相环设计

锁相环cd4046应用介绍

锁相环CD4046应用

数字锁相环(DPLL),数字锁相环(DPLL)是什么?

用锁相环CD4046实现电动机转速测量的研究

基于数字锁相环4046实现汽车测速系统的设计

基于数字锁相环4046实现汽车测速系统的设计

评论