数字锁相环技术原理

摘要:数字锁相环(DigitalPhase-LockedLoop,简称DPLL)是一种基于反馈控制的技术,用于实现精确的时序控制和相位同步。通过相位比较、频率差计算、频率控制、滤波和循环控制,它能够完成两个信号相位同步、频率自动跟踪的功能。数字锁相环不仅具有可靠性好、精度高、环路带宽和中心频率编程可调等优点,还解决了模拟锁相环的直流零点漂移、器件饱和及易受电源和环境温度变化等缺点,此外还具有对离散样值的实时处理能力。数字锁相环广泛应用于物理和工程领域,包括用于测量和跟踪信号频率、提取原始信号的给定频率分量并在同时消除噪声和杂散分量,或者基于输入信号合成新信号。此外,数字锁相环在调制解调、频率合成、FM立体声解码、彩色副载波同步、图像处理等各个方面得到了广泛的应用,已成为锁相技术发展的方向。

1.锁相环基本原理

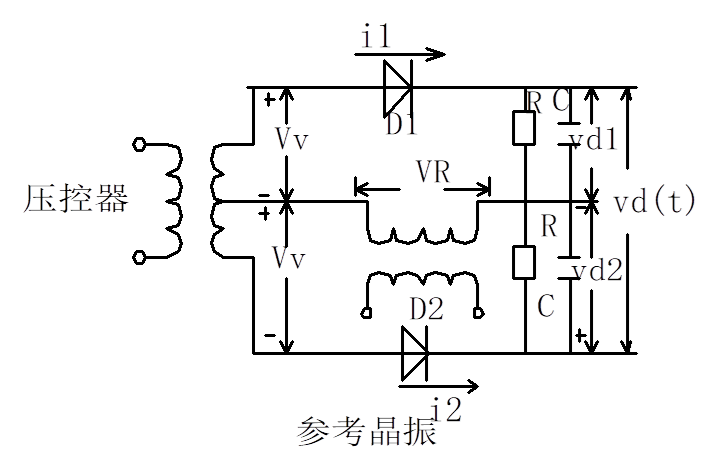

锁相环(PLL)技术也称自动相位控制技术,主要由鉴相器,低通滤波器(LPF),压控振荡器(VCO)和参考频率源(晶体振荡器)组成。

当压控振荡器的频率fv,由于某种原因发生变化时,必然相应地产生生相位变化。这个相位变化在鉴相器中与参考晶体振荡器的稳定(对应于频率fR)相比较,使鉴相器输出一个与相位误差成比例的误差电压ud(t),经过低通滤波器,取出其中缓慢变动的直流电压分量uc(t),并加到VCO的控制端,使压控振荡器的输出频率fv不断改变且向参考频率fR靠拢,直至fv=fR为止,从而使得uv(t)、us(t)两信号的频率相同而相位差保持恒定(同步),即实现频率自动跟踪和相位锁定。这就是是锁相环路的基本原理。

图1锁相环组成结构图

2.全数字锁相环的基本原理

全数字锁相环由数字鉴相器、数字环路滤波器、数控振荡器三部分组成。锁相环是一个相位反馈控制系统,而在数字锁相环中,由于误差控制信号是离散的数字信号,而不是模拟电压,因而受控的输出电压的改变是离散的而不是连续的;此外,全数字锁相环的环路组成部件也全用数字电路实现。其中可逆计数器及N分频器的时钟由外部晶振提供。全数字锁相环不使用VCO(电压控制振荡器),同时采用系统可编程芯片实现,这大大减轻温度及电源电压变化对环路的影响,有利于提高系统的集成度和可靠性。

3.全数字锁相环的实现

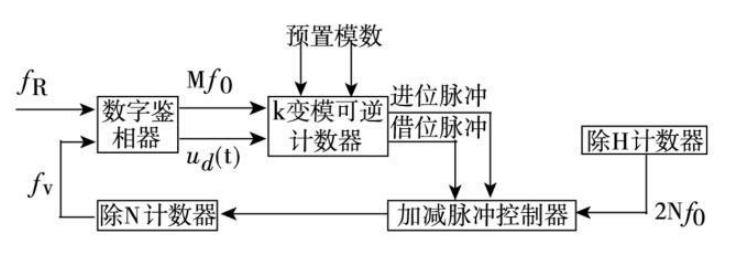

全数字锁相环是模拟锁相环系统的数字化,全数字锁相环的基本结构如图2所示。主要由数字鉴相器、K变模可逆计数器构成(模数K可预置)、加减脉冲控制器和除N计数器构成。K变模可逆计数器和加减脉冲控制器的工作频率分别为Mf0和2Nf0,f0为锁相环的中心频率。一般情况下M和N均为2的整数幂。时钟2Nf0经除H(H=M/2N)计数器得到。实际应用中一般在压控振荡器与鉴相器之间加入可控的变模分频器,来得到固定的或是可变的输出频率,输出频率与输入频率之间成比例关系。

图2全数字锁相环路结构图

3.1数字鉴相器的实现

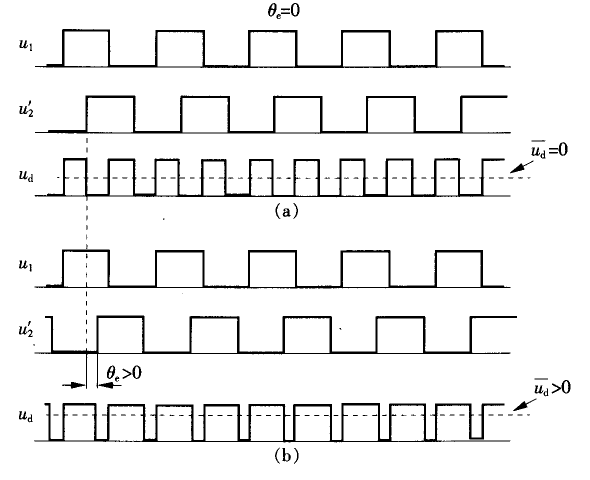

常用的数字鉴相器有三种类型EXOR鉴相器、JK触发型鉴相器和边沿控制鉴相器。数字鉴相器的作用是鉴别两个数字信号相位的差别,并通过信号将这种差别表示出来。数字鉴相器在很大程度上决定着锁相环的性能,选择的原则要从适用条件、线性鉴相范围、设计难易程度等角度综合考虑。其中EXOR鉴相器,它适用于波形对称的情况,线性鉴相范围为±Π/2,线性增益Kd=2/Π(V/rad)。通过比较输入信号u1(t)和反馈输入信号u2’(t)的相位产生一个误差信号ud(t),其作为K变模可逆计数器的加减方向控制信号,相位差为θe(θe=θv-θR)。环路锁定时,输入信号和输出信号之间没有相位误差时,输入和输出信号的相位刚好相差90°,经过异或门,产生占空比为50%的输出信号,该信号和输入信号波形相同,频率刚好是前者的两倍。这种情形如图3(a)所示。在这种情况下,可逆计数器加和减的周期是相同的,此时只要可逆计数器的k值足够大,其输出端就不会产生进位或借位脉冲。当输出信号u2’滞后于参考信号u1时,相位误差为正。这种情形如图3(b)所示。

图3 EXOR鉴相器的波形图(a)零相位误差(θe=0时波形)

(b)零相位误差(θe>0时波形)

3.2数字环路滤波器的实现

K变模可逆计数器是最重要的数字环路滤波器之一。这种环路滤波器通常和EXOR或者JK触发鉴相器一起工作,它由两个互相独立的计数器组成,这两个计数器通常被称之为加(UP)计数器和减(DN)计数器。实际应用中,这两个计数器总是向上计数的,K为这两个计数器的模,也就是说,这两个计数器的计数范围都是[0,K-1],其中K是由模K控制输入端控制,而且,一般是2的整数次幂。时钟信号(K时钟)的频率定义为ADPLL中心频率fo的M倍,M通常取8、16、32等。它对数字鉴相器输出的相位差信号进行加减运算,当运算结果达到由模值控制器所预设的模值时,计数器输出一个溢出信号,加减溢出判断电路对溢出信号进行判断:若是加溢出则输出进位脉冲;若是减溢出则输出借位脉冲。进位和借位脉冲可用来控制DCO(数控振荡器),使得DCO输出的脉冲数根据进位和借位来加上或者是删除一些脉冲,实际上也就改变了DCO的输出频率。可逆计数器的模值由K模值控制器控制,一般为2的整数幂,当模值控制器变化范围为4b0001~4b1111时,对应的模值的变化范围为23~217。即可根据模值的大小调整可逆计数器的长度来实现数字编程控制。

3.3数字振荡器的实现

数控振荡器由加减脉冲控制器和除N计数器组成。加减脉冲控制器的作用是实现对输入信号频率和相位的跟踪和调整,最终使得输出信号锁定在输入信号的频率和相位上,它是由D触发器和JK触发器组合实现的。当没有进位脉冲和借位脉冲输入时,即锁相环路稳定时,加减脉冲控制器对输入时钟进行二分频后输出,从而保持u1(t)和u2’(t)的正交;当有进位脉冲时,加减脉冲控制器除了将信号2分频,还会在2分频的过程中加入半个时钟周期,当有借位脉冲输入时,则是减去半个时钟周期,这个过程是连续发生的。由于实际门电路中延迟的影响,有可能在逻辑输出的信号中存在毛刺,从而产生不可预知的问题,所以可以通过时钟控制的D触发器来消除这些毛刺所带来的隐患。由此可见,加减脉冲控制器就是通过这种方式来调节相位以使闭环系统最终达到锁定状态。

Moku:Pro的PID/PLL

Moku:Pro的PID/PLL(相对于参考时钟)多达四个输入信号,从1 kHz到300 MHz的精度优于6 μ弧度。基于数字实现的锁相环架构,Moku:Pro的PID/PLL提供了动态范围、零死区和测量精度,超过了传统锁相放大器和频率计数器的性能。

Moku:Pro的PID/PLL特征

•四个独立的相位计通道输出选项,跟踪和记录两个独立信号的相位,频率和幅度。

•锁相输出选项,使您可以产生正弦波锁相输入。

•使用相位计的集成频谱分析工具包在频域观察测量数据。

•锁相环跟踪带宽从10hz到10khz。

关于昊量光电:

上海昊量光电设备有限公司是光电产品专业代理商,产品包括各类激光器、光电调制器、光学测量设备、光学元件等,涉及应用涵盖了材料加工、光通讯、生物医疗、科学研究、国防、量子光学、生物显微、物联传感、激光制造等;可为客户提供完整的设备安装,培训,硬件开发,软件开发,系统集成等服务。

审核编辑 黄宇

-

鉴相器

+关注

关注

1文章

56浏览量

23104 -

数字锁相环

+关注

关注

3文章

30浏览量

13356 -

DPLL

+关注

关注

1文章

12浏览量

13964 -

时序控制

+关注

关注

0文章

31浏览量

11907 -

相位同步

+关注

关注

0文章

5浏览量

7761

发布评论请先 登录

相关推荐

关于ADF4372锁相环输出幅度问题求解

AD9779内部锁相环无法锁定怎么解决?

DDS+PLL可编程全数字锁相环设计

数字锁相环技术原理

数字锁相环技术原理

评论