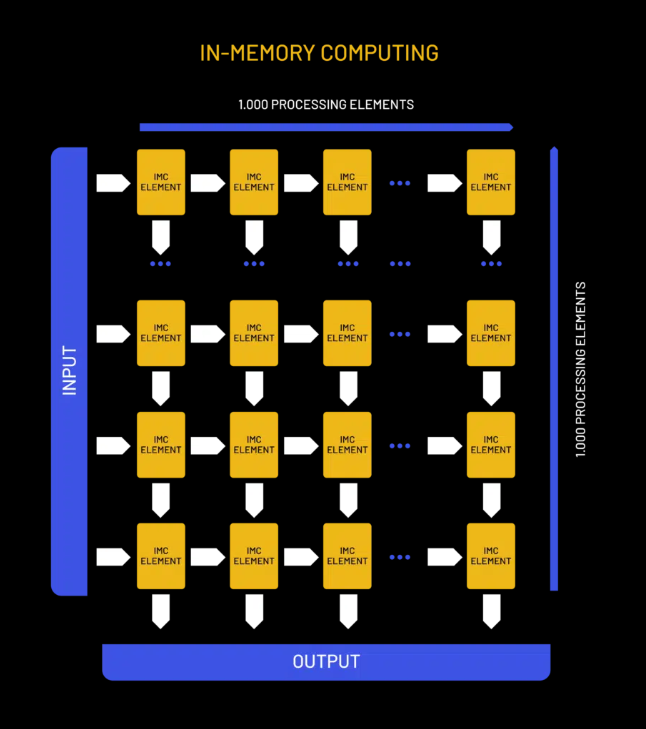

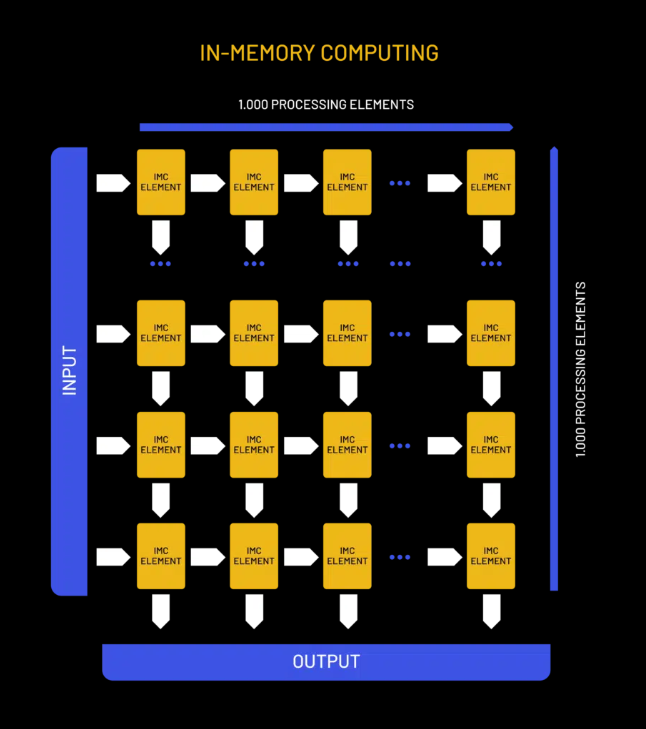

看到了其前景并提前布局。AI推理也使得存储HBM不再是唯一热门,更多存储芯片与AI推理芯片结合,拥有了市场机会。 已经有不少AI推理芯片、存算一体芯片将SRAM替代DRAM,从而获得更快的访问速度、更低的刷新延迟等。 静态随机存取存储器(Static

2025-03-03 08:51:57 2677

2677

SRAM(静态随机存储器)是一种在通电状态下可保持数据不丢失的存储器件,无需刷新即可持续工作,因此具有高速读写、响应及时的特点,广泛应用于对实时性要求高的场景。

2025-12-08 16:51:57 443

443

使用DMA将数据从FLASH传输到SRAM

下载示例

演示AT32F系列使用DMA将数据从FLASH传输到SRAM的使用方法。

注:本例程对应的代码是基于雅特力提供的V2.x.x 板级支持包

2025-12-03 16:26:37

在内存技术持续革新的今天,SRAM(静态随机存取存储器)和DRAM(动态随机存取存储器)依然是计算系统中最核心的存储组件。尽管出现了MRAM、ReRAM等新兴存储方案,但二者凭借成熟的设计与明确

2025-12-02 13:50:46 869

869 Cypress赛普拉斯512Kbit FRAM凭借微秒级写入、10^14次擦写寿命及151年数据保留,为车载黑匣子EDR提供高可靠数据存储。其-40℃~105℃车规级工作范围确保碰撞数据完整记录,满足汽车安全法规严苛要求。

2025-12-01 09:47:00 246

246

MRA、MRB、SAR、DAR、CRA和CRB这些都是属于DTC内部的寄存器,它们是无法通过CPU直接访问的。这些DTC内部寄存器中设置的值作为传输信息放置在SRAM区域中。当生成激活请求时,DTC

2025-11-28 15:50:58 4483

4483

运动控制领域,通常需要外扩FPGA实现高速脉冲收发、高速探针锁存、比较输出等功能,ARM和FPGA之间的接口通常选择并口(Localbus)或SPI接口。

FET153-S核心板引出了并口接口,但

2025-11-28 14:13:39

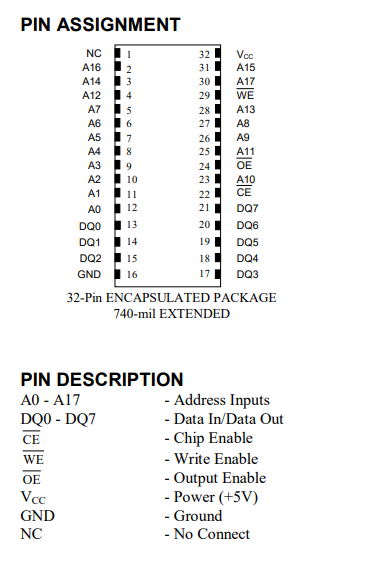

在各类电子设备与嵌入式系统中,存储器的性能与功耗表现直接影响着整体设计的稳定与效率。低功耗SRAM,特别是异步SRAM系列,凭借其出色的能效比与高可靠性,正成为越来越多工业控制、通信设备及便携终端中的关键部件。

2025-11-25 15:42:56 271

271

在各类存储设备中,SRAM(静态随机存储器)因其高速、低功耗和高可靠性,被广泛应用于高性能计算、通信和嵌入式系统中。其中,双口SRAM静态随机存储器凭借其独特的双端口设计,在高带宽和多任务场景中表现尤为出色,成为提升系统效率的重要组件。

2025-11-25 14:28:44 275

275 VS Code运行 pytest_hello_world.py

2025-11-24 00:33:33 442

442 DRAM利用电容存储数据,由于电容存在漏电现象,必须通过周期性刷新来维持数据。此外,DRAM采用行列地址复用设计,提高了存储密度,但增加了控制复杂性。它广泛用于大容量、低成本存储场景,如计算机内存。

2025-11-18 11:49:00 477

477 在现代高性能电子系统中,存储器的读写速度往往是影响整体性能的关键因素之一。同步SRAM(Synchronous Static Random Access Memory)正是在这一需求下发展起来的重要

2025-11-18 11:13:01 244

244 富士通16Kbit FRAM凭借微秒级写入速度与10万亿次擦写寿命,为图传模块提供高可靠性数据存储。其SPI接口与工业级温度范围(-40℃~85℃)完美适配无人机、安防监控等场景的实时数据记录需求。

2025-11-18 09:48:00 317

317

在处理器性能持续攀升的今天,存储系统的速度已成为制约整体算力的关键瓶颈之一。作为最接近CPU核心的存储单元,SRAM(静态随机存取存储器)承担着高速缓存的重要角色,其性能直接影响数据处理效率。当前

2025-11-12 13:58:08 457

457 PSRAM(伪静态随机存储器)是一种兼具SRAM接口协议与DRAM内核架构的特殊存储器。它既保留了SRAM无需复杂刷新控制的易用特性,又继承了DRAM的高密度低成本优势。这种独特的设计使PSRAM在嵌入式系统和移动设备领域获得了广泛应用。

2025-11-11 11:39:04 499

499 我目前正在使用EZ-USB™ CX3(MIPI CSI-2 到超高速USB桥接控制器)开发固件。

我想知道如何检查或估算该设备的SRAM 使用量。

由于 CX3不支持 JTAG 访问,我无法使用典

2025-11-11 06:33:59

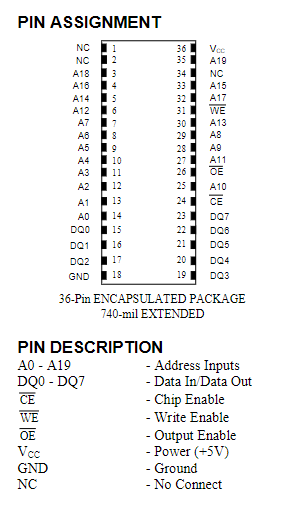

在要求高性能与高可靠性的电子系统中,存储器的选择往往成为设计成败的关键。Netsol推出的高速异步SRAM系列,凭借其出色的性能表现与独有的错误校正(ECC)能力,为工业控制、通信设备及高精度计算等应用提供了值得信赖的存储解决方案。

2025-11-05 16:21:39 284

284 上一篇文章介绍了如何在VS code中使用瑞萨官方插件为RA芯片创建项目与项目调试,相信大家对RA在VS code中的开发有了基础的了解。

2025-11-05 14:46:31 1250

1250

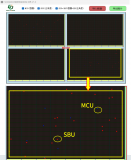

大家好,本团队此次分享的内容为可实现数据全复用高性能池化层设计思路,核心部分主要由以下3个部分组成;

1.SRAM读取模块;——池化使用的存储为SRAM

基于SRAM读与写时序,约束池化模块读与写

2025-10-29 07:10:56

PSRAM全称为pseudo SRAM,一般叫伪静态SRAM,串行PSRAM具有类似SRAM的接口协议,给出地址,读、写命令,就可以实现存取,不同于DRAM需要用到memory controller来控制内存单元定期数据刷新

2025-10-27 16:04:47 450

450 非挥发性存储器,如NAND、NOR Flash,数据在掉电后不会丢失。这类存储器通常速度比较慢,可以做资料和大数据存储。

2025-10-27 15:14:39 310

310 在存储解决方案中,外置SRAM通常配备并行接口。尽管并口SRAM在数据传输率方面表现卓越,但其原有的局限性也日益凸显。最明显的挑战在于物理尺寸:不论是占用的电路板空间或是所需的引脚数量,并行接口都

2025-10-26 17:25:18 835

835 在需要高速数据写入与极致可靠性的工业与数据中心应用中,Everspin推出的8位位并行接口MRAM树立了性能与耐用性的新标杆。这款Everspin存储器MRAM与SRAM引脚兼容的存储器,以高达35

2025-10-24 16:36:03 532

532 本篇将详细介绍如何利用Verilog HDL在FPGA上实现SRAM的读写测试。SRAM是一种非易失性存储器,具有高速读取和写入的特点。在FPGA中实现SRAM读写测试,包括设计SRAM接口模块

2025-10-22 17:21:38 4118

4118

电机驱动EMC整改:传统VS智能,性价比之争|深圳南柯电子

2025-10-21 10:13:33 354

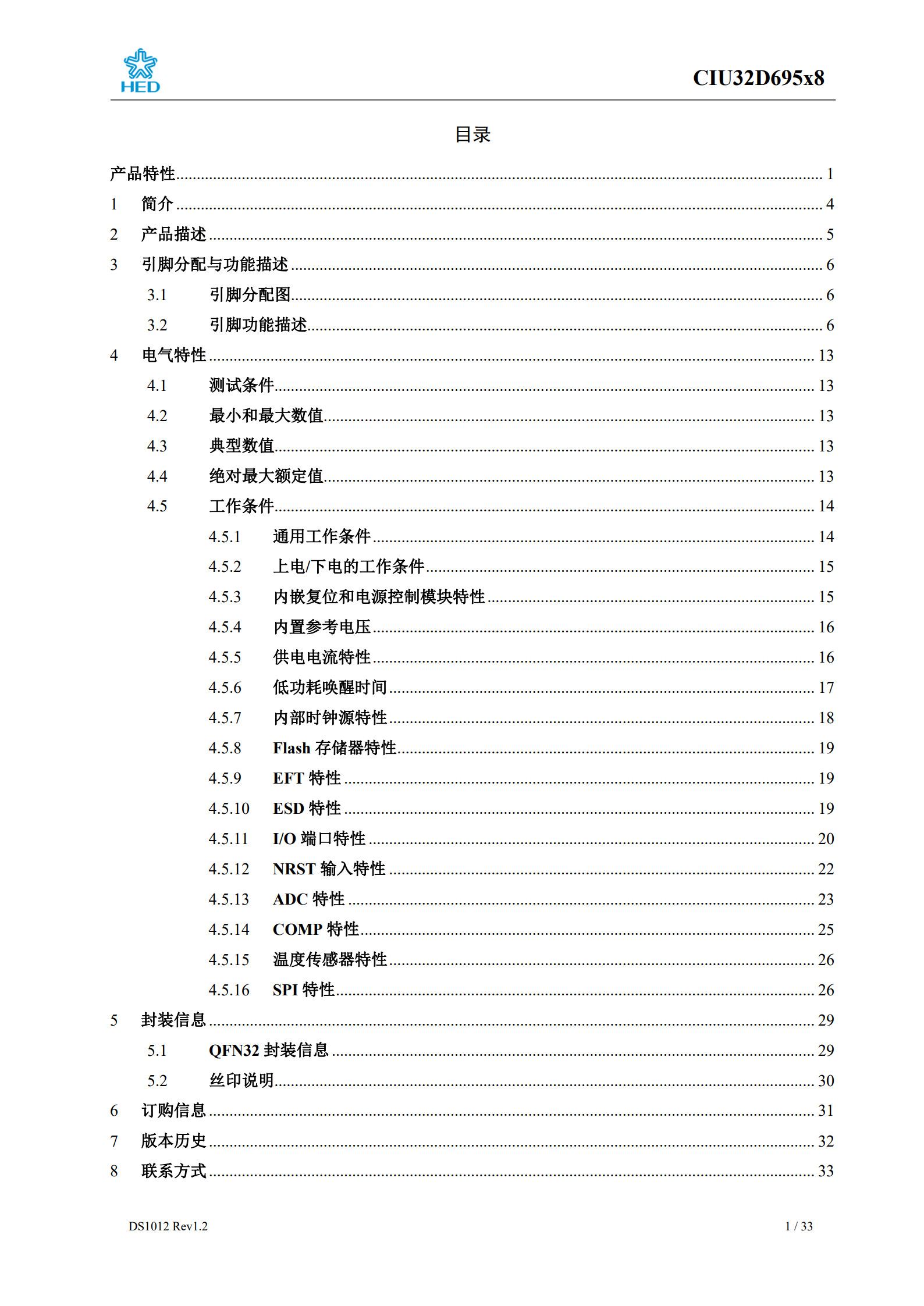

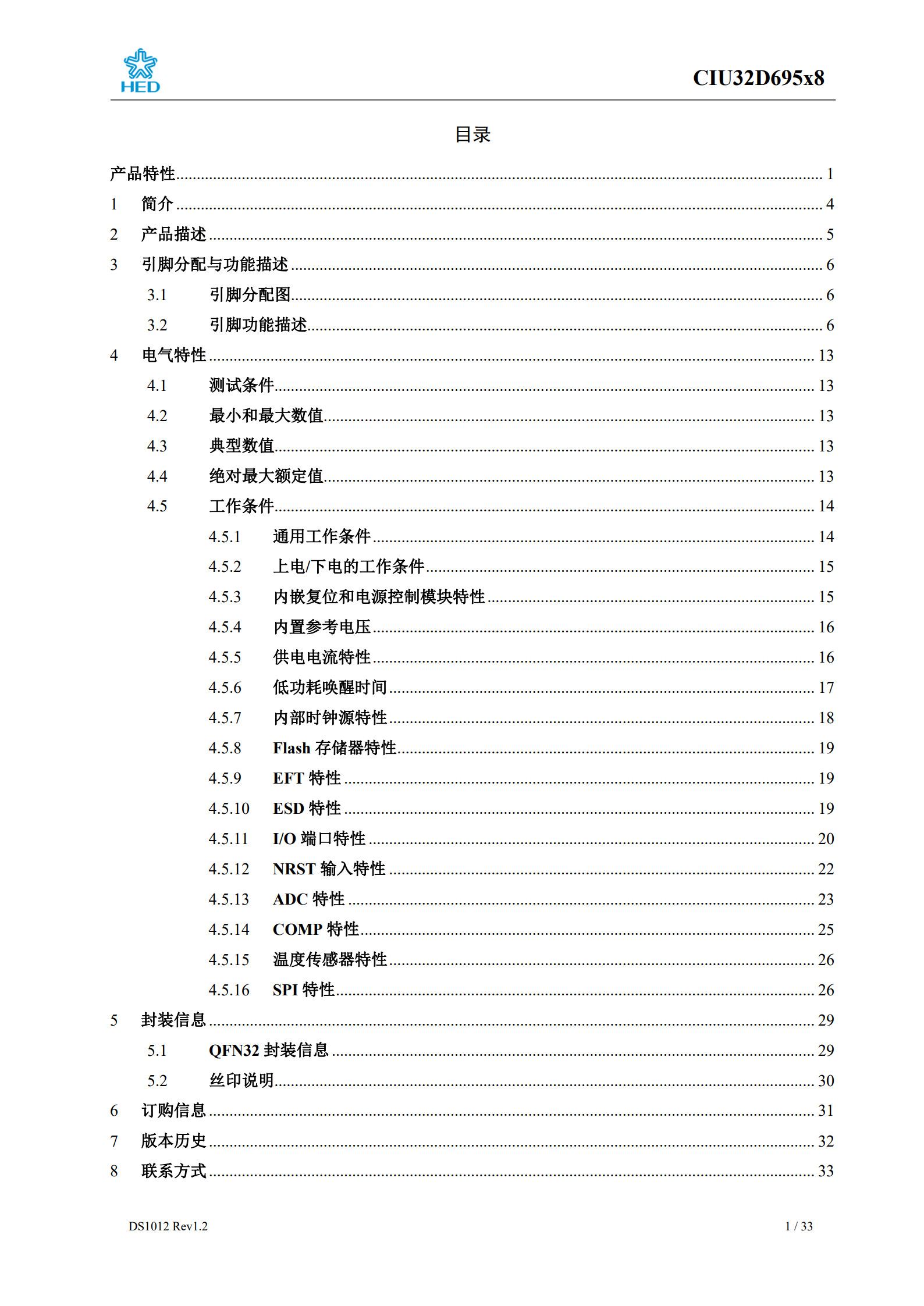

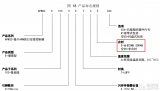

354 CIU32D695x8 ARM Cortex-M0+ 32-bit MCU,64KB Flash ,6KB SRAM , DMA ,2x UART , I2C ,2x SPI , Timers

2025-10-20 11:37:02 801

801

ADSP-21060LCW-160内容介绍: 哈喽,朋友们,今天我要向大家介绍的是一款处理器——ADSP-21060LCW-160。 它拥有一个令人惊叹的计算核心,能够以每秒 4000 万条指令(40 MIPS)的速度运行,更令人瞩目的是,它每秒可以完成高达 1.6 亿次浮点运算(160 MFLOPS)。这

2025-10-15 12:01:31

富士通MB85RC04VPNF-G-JNERE1 4Kbit工业级FRAM,150ns极速写入、1万亿次擦写、-40℃~+85℃宽温,I²C接口低功耗,SOP-8小封装,为PLC、电表、编码器等边缘节点提供高可靠非易失存储。

2025-10-10 09:45:00 307

307

Microchip Technology 23AA04M和23LCV04M 4Mb SPI/SDI/SQI SRAM是随机存取存储器器件,可通过兼容串行外设接口 (SPI) 的串行总线访问。SRAM

2025-10-09 11:16:59 540

540 Microchip Technology 23AA02M和23LCV02M 2Mb SPI/SDI/SQI SRAM是可以通过串行外设接口 (SPI) 兼容总线访问的随机存取存储器器件。该SRAM

2025-10-09 11:12:55 561

561 富士通256Kbit FRAM MB85RS256BPNF-G-JNERE1为LED显示系统提供高速、高耐久性数据存储方案,支持纳秒级写入与10^12次擦写,解决传统存储器延迟高、寿命短问题,适用于智能交通、户外广告等严苛环境,显著提升系统响应与可靠性。

2025-09-11 09:45:00 481

481

在此前的文章《SRAM PUF:为每颗芯片注入“不可复制的物理指纹”,守护芯片安全》中,我们探讨了基于SRAM的物理不可克隆功能(PUF)的基本原理,并介绍了SRAM PUF作为一种安全可靠、经济

2025-09-05 10:46:16 1153

1153 ISSI IS62WV51216BLL-55TLI是一款8Mb(512K×16)高速异步SRAM,采用55ns访问速度、2.5V~3.6V宽电压设计,支持-40℃~85℃工业级温度范围,适用于车载导航、工业控制及通信设备等高可靠性场景。

2025-09-04 10:00:00 534

534

8月29日,广汽集团发布2025年半年度报告。报告期内,公司合并口径营业总收入约426.11亿元。公司资产负债率为44.65%,财务健康水平进一步提高。

2025-09-01 10:50:55 1265

1265 Cypress 64Kbit FRAM以纳秒写入、万亿次擦写、微瓦功耗,破解手持检测器数据丢帧、寿命及续航痛点,覆盖-40℃~85℃,50G抗震,直接替代EEPROM,30天续航,零掉电丢数。

2025-08-28 09:45:00 434

434

使用 NUC505 时如何将代码放入 SRAM 中执行?

2025-08-28 08:25:40

如何保持SRAM的状态,并在芯片复位时不初始化?

2025-08-25 06:09:44

如何保持SRAM的状态,并在芯片复位时不初始化?

2025-08-21 07:17:17

如何在Keil开发环境中查看代码大小和SRAM使用情况?

2025-08-20 06:38:41

两个总线能不能同时使用,用了华邦的SDRAM发现SDRAM数据高概率读写错误,但是用ISSI的没问题。如果不对外部SRAM读写就正常。

2025-08-12 06:56:57

如今我们所生活的互联世界依赖于数以亿计的芯片。社会正常运转所需的芯片数量之大,令人惊叹,因此保护芯片安全的技术至关重要。

2025-08-11 16:18:13 1127

1127

AD7606BSTZ引脚配置:OS0/OS1/OS2=0;RANGE=0; REF SEL=0; STBY=0;REFIN外接5v,采样频率10khz,并口模式,STM32F103fsmc读取,采集5v基准得到数值0X76F6,而不是0X7FFF,采集其它电压,等比例缩小,请问什么原因呢?

2025-07-28 08:20:47

赛普拉斯2 Mbit FRAM FM25V20A-DG以40 MHz SPI总线、10¹²次擦写寿命和100 krad(Si)抗辐射能力,取代呼吸机中EEPROM与SRAM加电池的传统方案,为智能生命支持系统提供原子级可靠的数据存储基石。

2025-07-24 11:25:44 521

521

= 0x102a26db, LR = 0x7ffffff

同样的逻辑在SRAM0,SRAM1,SRAM2,和code flash的ecc inject测试暂时都没有出现过这类问题。 work flash需要做什么特殊的操作吗?

2025-07-18 06:19:51

各位大佬,我们实验室有一台设备,以一个单片机作为微型计算机,有一个db25并口输出接口用来连接针式打印机,我现在想把它跟工控机连接起来读取其输出数据,联系过厂家说他们没有做这种功能,但是既然可以连接

2025-07-15 17:42:52

一般我们开发MCU自带的SRAM,对一般应用来说,已经够用了,但是对于内存需求较高的场合,比如跑GUI或者算法等,自带的内存会就不够用,这个时候就要外扩SRAM或SDRAM。

2025-07-15 09:33:09 1781

1781

客户要求Flash driver不能存储在Flash中,需要在升级的时候,由CAN FBL发送到SRAM中,再运行SRAM中的Flash driver

我应该如何实现这个要求?如何能把Flash driver分离成一个单独的部分,再由CAN FBL加载到SRAM中?你们有相关的文档和示例程序吗?

2025-07-15 07:22:16

电子发烧友网综合报道,Marvell 美满电子当地时间 17 日宣布推出业界首款 2nm 定制 SRAM,可为 AI xPU 算力设备提供至高 6Gb(即 768MB)的高速片上缓存。Marvell

2025-06-21 00:57:00 7264

7264 CS56404L 64Mb Quad-SPI Pseudo-SRAM 产品特点及核心优势:核心特点接口与模式支持 SPI(单线) 和 QPI(四线) 模式,默认上电为 SPI 模式,可通过指令切换至

2025-06-06 15:01:36

近期受晶圆厂委托, 季丰在执行完SRAM芯片在中子辐射下SER测试后, 通过对SRAM芯片的深入研究,对测试失效数据的分析,将逻辑失效地址成功转换为物理坐标地址,最终在图像上显示失效位置,帮助客户直观地看到失效点分布位置。 通过多个失效芯片图像的叠加,客户可以看到多个芯片失效积累效果。

2025-06-03 10:08:45 862

862

我对 PMG1 闪光灯有疑问。

1.微控制器读取闪存中的软件信息时,软件信息部署在哪里? 是 SRAM 吗?

2.微控制器加载软件时,在部署之前是否检查 SRAM 是否复位?

2025-05-23 06:22:31

在工业通信领域,技术革新与突破始终是推动行业发展的核心动力。今天,为大家带来基于DSMC/FlexBus并口的RK3576J与FPGA通信方案,核心板国产化率高达100%,为工控场景带来高效、稳定的通信新体验。

2025-05-21 11:51:05 1687

1687

为大家带来基于DSMC/FlexBus并口的RK3576J与FPGA通信方案

2025-05-20 11:45:18 4103

4103

你好。我是CYUSB3的初学者。

我想创建一个使用 CYUSB3KIT-003 使用 GPIO 访问 SRAM 的应用程序。

目前我已经在我的电脑上安装了SDK,但是有什么参考资料吗?

2025-05-14 06:51:40

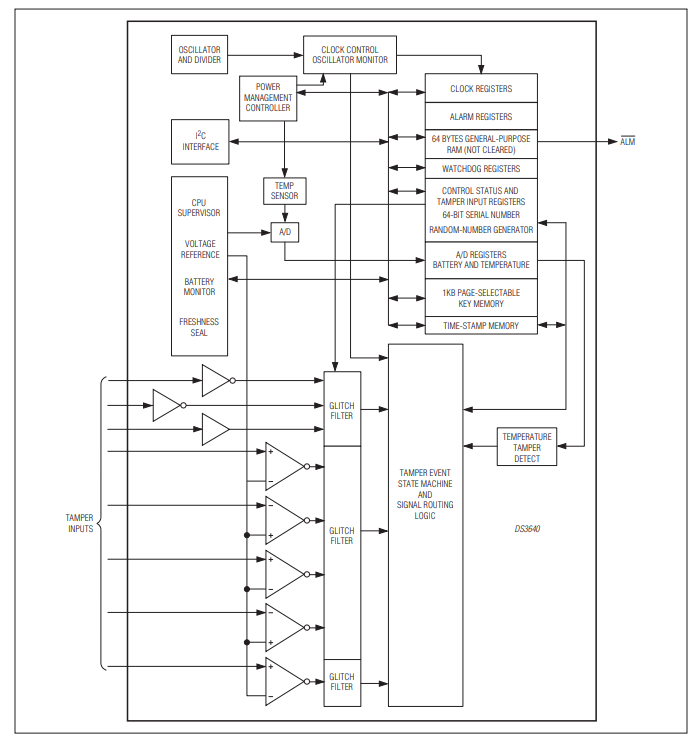

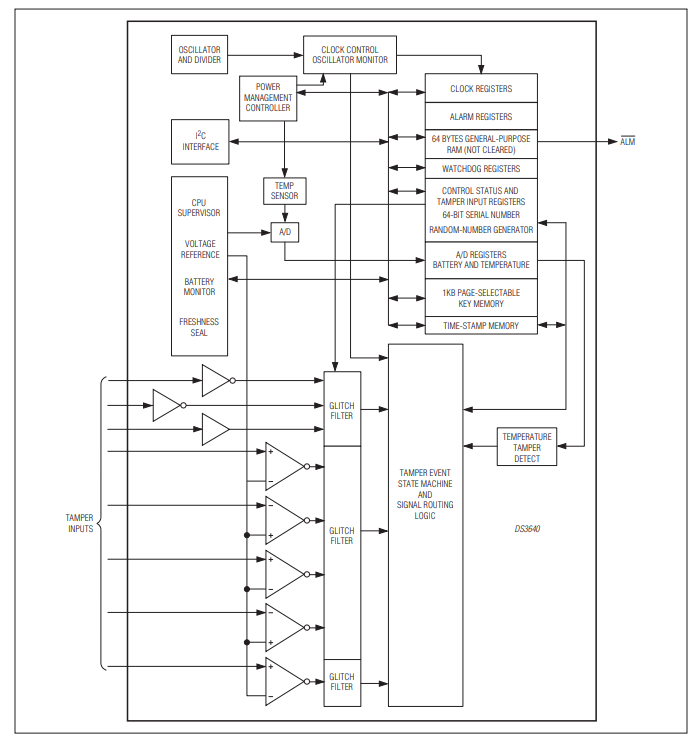

DeepCover 嵌入式安全方案采用多重先进的物理安全机制保护敏感数据,提供最高等级的密钥存储安全保护。

DeepCover安全管理器(DS3640)是一款具有1024字节加密SRAM的安全

2025-05-13 11:22:05 618

618

规格型号:T19264M02外形尺寸:120.0mm*62.0mm视窗尺寸:104.0mm*39.0mm控制芯片:7920带中文字库接口方式:并口/串口工作电压:5.0V或3.3V规格型号

2025-04-28 10:50:33

规格型号:T12864C065A外形尺寸:65mm*41mm,视窗尺寸:61.5*31.5mm,控制芯片:ST7565,接口方式:并口或SPI串口,工作电压:3.3V,显示效果:白底黑字、绿底黑字

2025-04-28 10:43:03

产品型号:T12232M6529A外形尺寸:65.4*29.0*5.8MM视窗尺寸:60.0*19.0MM通讯接口:并口/SPI/3.3V/5V/排线接口控制芯片:ST7565工作电压

2025-04-27 16:33:02

UV-EPROM的结构与使用方法,闪速存储器的结构与使用方法,EEPROM的结构与使用方法, SRAM的结构与使用方法, 特殊的SRAM的结构与使用方法 ,DRAM的结构与使用方法,

2025-04-16 16:04:56

我有 NXP S32G3 板。我有 .map 文件。有没有办法从 .map 文件确定 SRAM 使用情况。

非常感谢帮助。

2025-04-08 06:00:58

中小尺寸彩屏TFT-LCD显示控制器RA8889ML3N电路原理图,最高驱动1366*2048分辨率,支持并口/串口(SPI)主控接口,支持图形绘图引擎,支持JPEG视频硬解码. 原理图和PCB图资料如下:*附件:RA8889_EV_Board_202006118.zip

2025-04-03 14:33:52

如何使用 S32 Design Studio for ARM 将自定义数据放入 SRAM 中以进行S32K146?

2025-04-01 08:27:32

我在定制硬件中使用S32K312 IC (单核)。我已使用 RTD SDK 创建了该项目。

我看到有以下 RAM(大分区)可供我们使用(根据生成的链接器文件):

int_dtcm

int_sram

2025-03-27 07:16:12

除了运算、控制和存储部件,海波阔系统需要的一些通用的外部接口,如中断控制器、看门狗、计数器、串口和并口等。

MCU主要应用于要求不高的场合。

中央处理器(CPU)

中央处理器(CPU)是通用

2025-03-23 09:47:39

PT5F2306 是一款 51 内核的触控 A/D 型 8 位 MCU,内置 16K*8bit FLASH、内部 256*8bitSRAM、外部 512*8bit SRAM、触控检测、12 位高精度

2025-03-17 17:25:28 0

0 采用STM32F427+FPGA+Flash。

STM32通过FMC总线访问FPGA内部SRAM,起始地址为0x60000000;

Flash中存储FPGA的配置数据,STM32和FPGA均可

2025-03-12 07:59:54

SRAM16 KB RTC SRAM最大 8 MB Quad SPI flash2 MB 嵌入式 PSRAM(仅 ESP32 - S3FH4R2 芯片)Wi -

2025-03-07 14:46:59

本书主要介绍了UV-EPROM的结构和使用方法,闪速存储器的结构和使用方法,EEPROM的结构和使用方法, SRAM的结构与使用方法,特殊的SRAM的结构与使用方法,DRAM的结构与使用方法,

2025-03-07 10:52:47

两块SRAM分别位于不同的基地址,有什么方法可以使这两块区域SRAM当成一块使用

2025-03-07 08:59:10

,520KB SRAM,16KB RTC SRAM模组集成元件40MHz 晶振4/8/16MB SPI flash(可选),ESP32-DOWDR2-V3 芯片另内置 2

2025-03-06 19:42:35

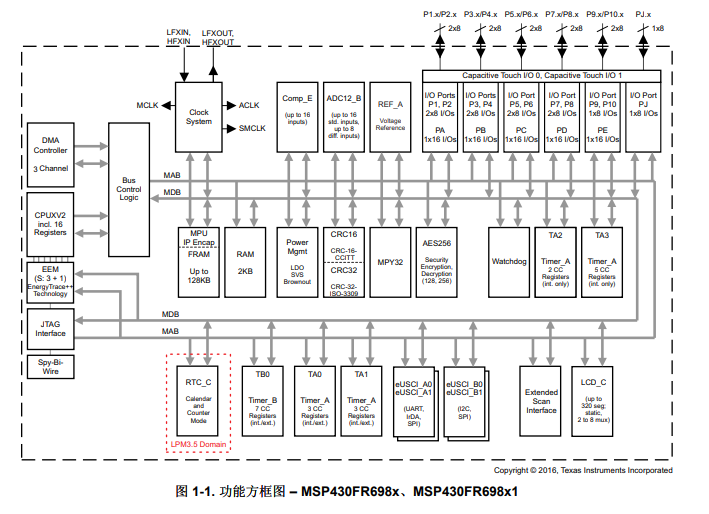

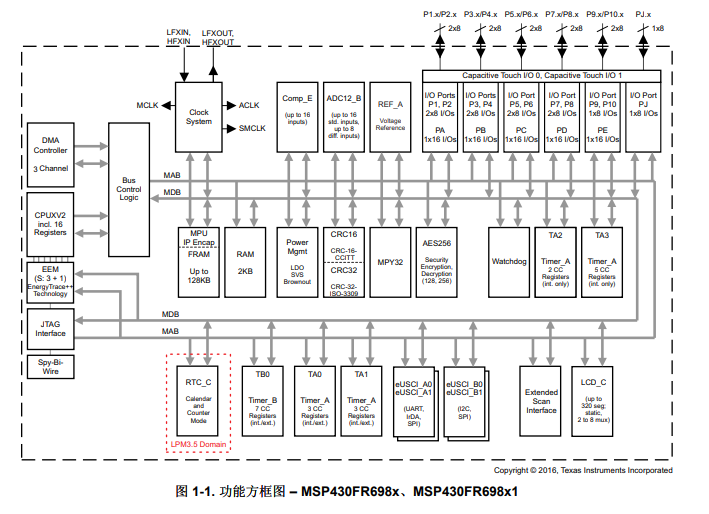

MSP430™超低功耗(ULP)FRAM平台将独特的嵌入式FRAM和整体超低功耗系统架构组合在一起,从而使得创新人员能够以较少的能源预算增加性能。FRAM技术以低很多的功耗将SRAM的速度、灵活性和耐久性与闪存的稳定性和可靠性组合在一起。

2025-03-04 17:11:15 1075

1075

P1032BF1是一款基于ARM Cortex-M3的单片机,专为Wi-Fi /蓝牙通信控制而设计;能够实现指纹的图像采集、特征提取、特征比对,可应用于智能锁;支持大型程序代码和拥有大型嵌入式SRAM,也可用于一般的MCU应用。

2025-03-04 09:27:09 762

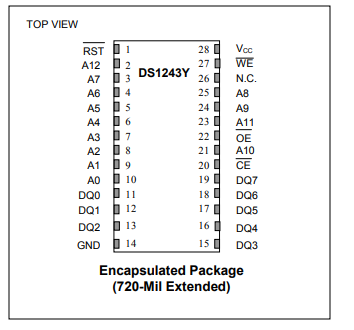

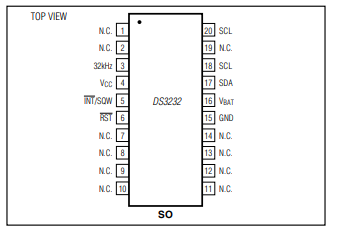

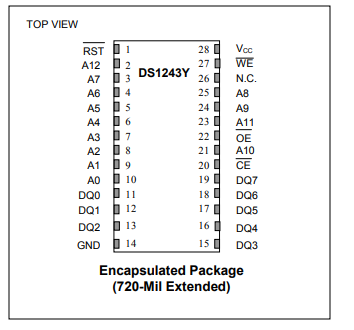

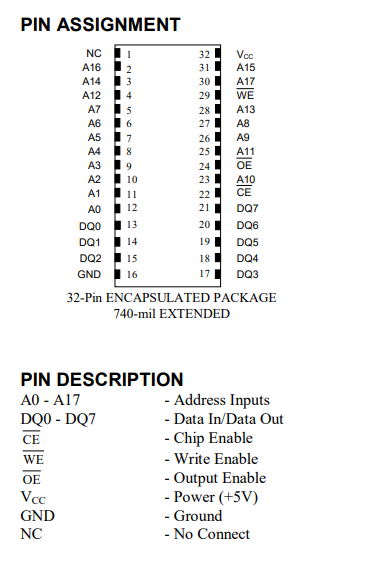

762 带幻象时钟的DS1243Y 64K NV SRAM是一款内置实时时钟、完全静态的非易失性RAM(结构为8192个字x 8位)。DS1243Y具有独立的锂能源和控制电路,可持续监控VCC是否发生超出容

2025-02-28 10:31:43 995

995

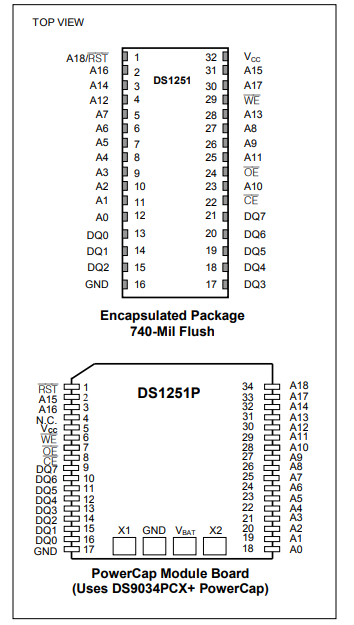

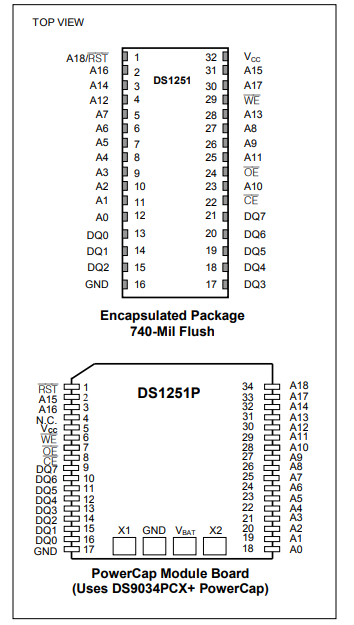

具有隐含时钟的DS1251 4096k NV SRAM为全静态非易失RAM (按照8位、512k字排列),内置实时时钟。DS1251Y自带锂电池及控制电路,控制电路连续监视V~CC~是否超出容差范围,一旦超出容差,锂电池便自动切换至供电状态,写保护将无条件使能、以防存储器和实时时钟数据被破坏。

2025-02-27 15:44:58 891

891

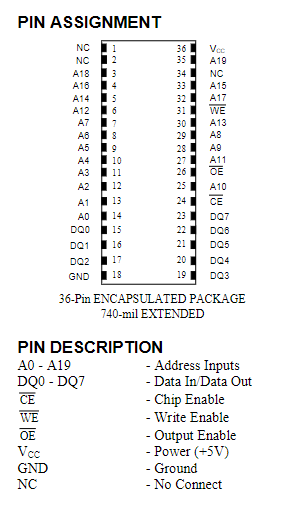

具有隐含时钟的DS1248 1024k NV SRAM为全静态非易失RAM (按照8位、128k字排列),内置实时时钟。DS1248自带锂电池及控制电路,控制电路连续监视V~CC~是否超出容差范围,一旦超出容差,锂电池便自动切换至供电状态,写保护将无条件使能、以防存储器和实时时钟数据被破坏。

2025-02-27 15:38:41 748

748

具有隐含时钟的DS1244 256k、NV SRAM为全静态非易失RAM (NV SRAM) (按照8位、32k字排列),内置实时时钟。DS1244自带锂电池及控制电路,控制电路连续监视V~CC

2025-02-27 10:10:50 932

932

DS1265 8M非易失SRAM为8,388,608位、全静态非易失SRAM,按照8位、1,048,576字排列。每个NV SRAM均自带锂电池及控制电路,控制电路连续监视V~CC~是否超出容差范围

2025-02-27 09:19:54 821

821

DS1249 2048k非易失(NV) SRAM为2,097,152位、全静态非易失SRAM,按照8位、262,144字排列。每个NV SRAM均自带锂电池及控制电路,控制电路连续监视V~CC~是否

2025-02-27 09:09:09 951

951

我们项目里面只用到了mipi接口,请问下如何处理不用的并口输入呢?

规格书中在第7页有描述PDM_CVS_TE,VSYNC_WE,HSYNC_CS,DATAEN_CMD需要下拉,但没有明确说PCLK和PDATA【0~23】该如何处理,

请问下PCLK和PDATA【0~23】该如何处理呢?

2025-02-27 08:43:29

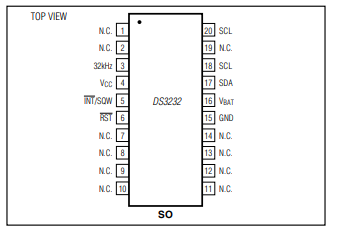

DS3232是低成本温度补偿晶体振荡器(TCXO),内置精度极高的温度补偿实时时钟(RTC)以及236字节电池备份SRAM。此外,DS3232还具有电池输入,可在器件主电源掉电时保持精确计时。集成晶

2025-02-26 15:05:23 1007

1007

DS3232M是一款低成本、极其精确的I2C实时时钟(RIC),具有236字节的电池支持SRAM。该设备集成了电池输入,并在设备主电源中断时保持精确的计时,微机电系统(MEMS)谐振器的集成提高了

2025-02-26 13:58:47 1055

1055

问下我如果只用到DLPC3433的mipi输入,将并口进行接地处理(如下图)会不会对mipi-dsi的使能有影响呢?

2025-02-26 06:54:29

请问如果仅仅使用MIPI DSI,并口不用。那么如果有些并口引脚悬空,那么会影响MIPI的使能吗?

2025-02-26 06:01:27

结果变化,因此RGB并口上发出的两帧图片间隔可能会比较长(下图Frame TIme时间)。请问这种情况下DLPC900对VSYNC的间隔是否有最小时间要求?比如必须固定60Hz之类的?

另外,请问如果我们去掉EVM的IT6535的话,是否不能直接使用官网上的FW和GUI?

2025-02-24 06:45:02

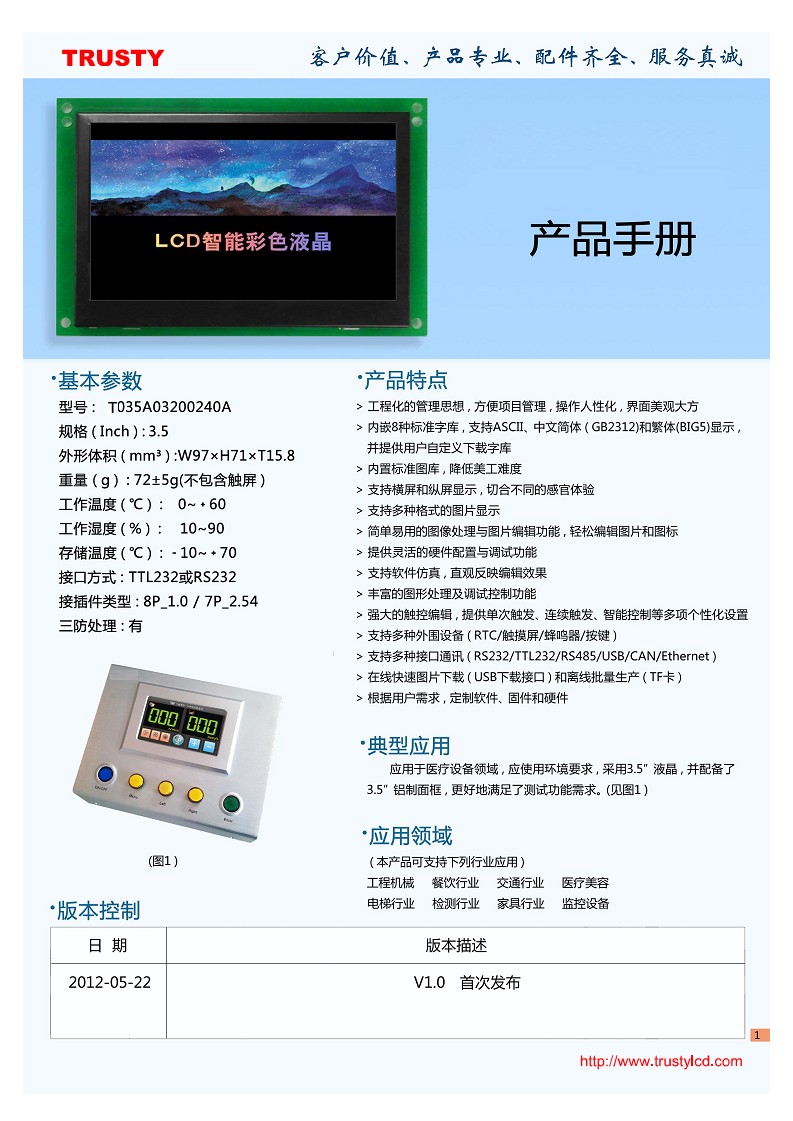

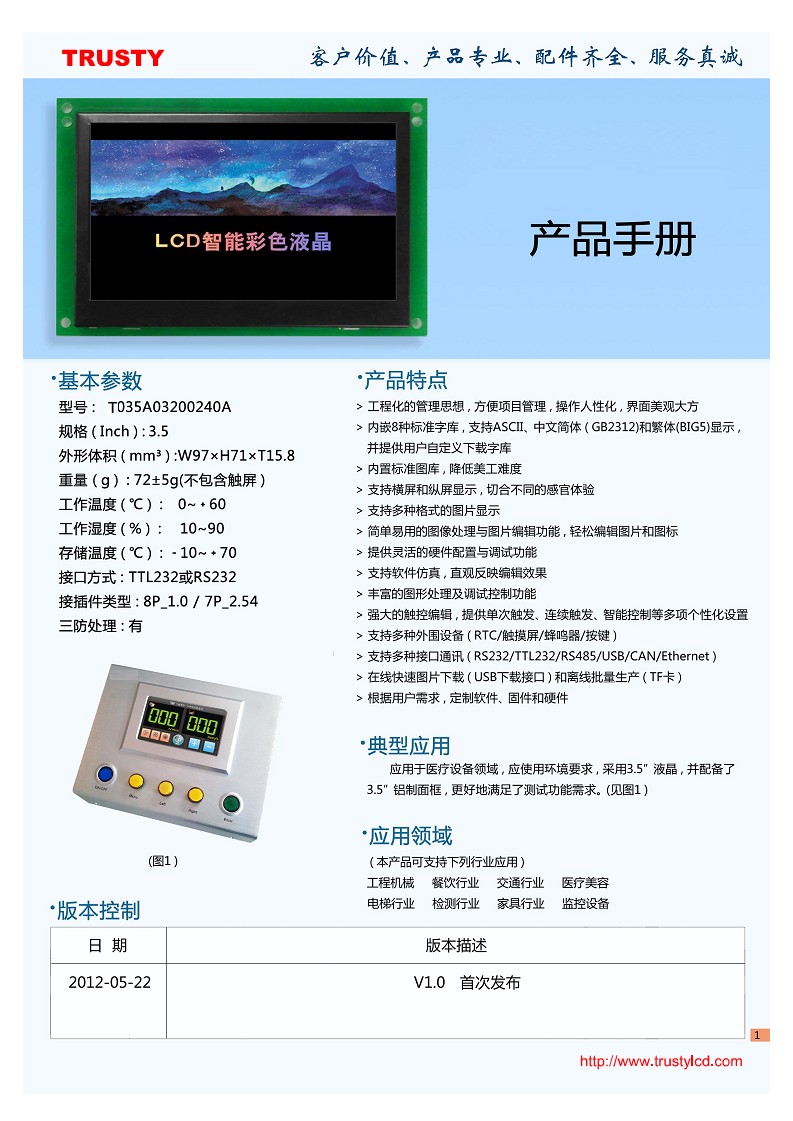

3.5英寸高清智能串口屏 8位MCU并口通信的COG裸屏 或带驱动板232串口通信的智能屏

2025-02-18 14:49:36 824

824

),

通过并口传输,在RGB888模式下,图片大小为1920*1080*24bit, 如果时钟频率是100MHz,需要多久能传输完毕?和速度1440 Hz (1-bit) and 180 Hz (8-bit)有何关系?多谢

2025-02-18 07:21:58

规格型号:T160160C027B分 辨 率:160*160外形尺寸:65.5*71.5视窗尺寸:60.0*60.0显示模式:FSTN工作电压:3.3V通讯接口:SPI或8位并口,FPC焊接"

2025-02-17 13:58:40 1

1

你好。我选用的是TI的ths1230与DSP2812之间直接并口连接,进行数据采集,时钟频率为12.5MHZ,也即采样率为12.5MHZ,XINTF选用的是ZONE6。但DSP读AD的数据

2025-02-11 06:55:58

产品概述 Korchip DCS5R5334H 是一款高性能的低功耗 SRAM(静态随机存取存储器),专为高速数据存储和处理而设计。该器件具有快速的访问时间和较高的数据传输速率,广泛应用

2025-02-09 22:38:10

这次采用ads8548作为AD芯片,采用pdf上的电路,用的是硬件模式,采集电压给的都是1V,busy信号也出来了,为什么从并口读出来的数都是全0呢?

2025-02-05 07:19:59

时的频率PWM正常、产生500K频率时在上升沿和下降沿有些尖脉冲、达到10M时PWM波直接失真变形成了类似正弦波);二是告诉ADC的并口输出的数据处理问题(我们目前使用的ADC12040为12位并口输出

2025-01-24 06:51:37

实践ADS1605

因为设计要做ADS解码专用,所以找来找去用到了ADS1605这个芯片,并口设计,信号可以识别小信号的。

因为买的是专业板子,所以上面都集成好了。

板子流程图。

用到解码流程图

效果还不错,就是数据容易受到干扰的。

2025-01-21 07:58:03

软件设置,并口。内部参考电压。REFIO 和 REFN 引脚通过0.47uF电容,REFN接地。配置寄存器为0X8C0083FF。

BUSY引脚监测读取数据,数据不正确。测量REFIO引脚电压为0.

看手册,REFIO引脚应该是内部参考的输出啊。请问哪儿出问题了。

2025-01-16 06:47:28

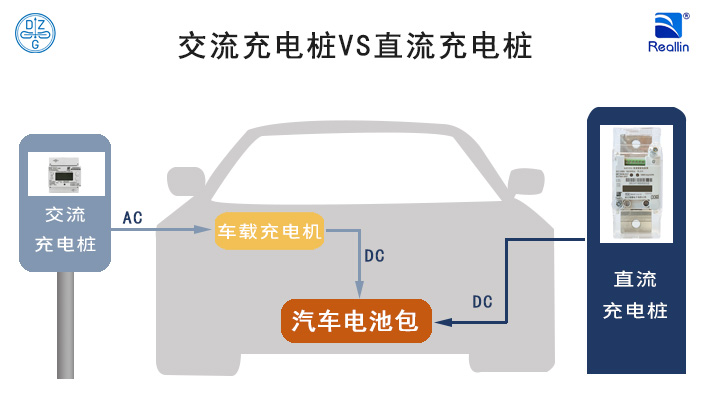

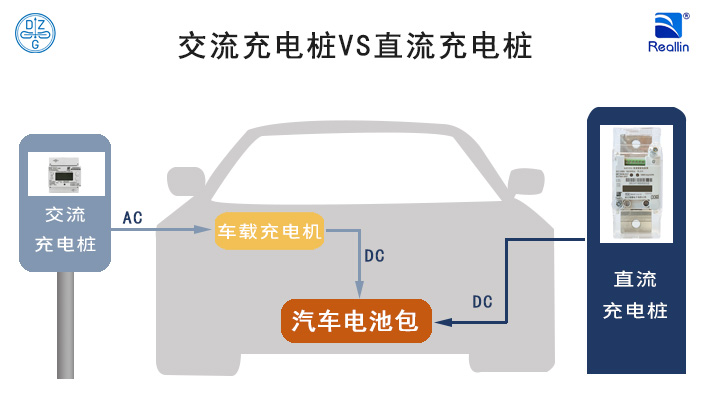

交流充电桩VS直流充电桩,您真的清楚它们的区别吗?

2025-01-14 11:24:50 2863

2863

的内部存储器进行指令获取,F-CBUS的目标是内部Flash、外部存储器(QSPI_flash)、BLE和内部SRAMs SRAM0 SRAM1 SRAM2和SRAM3。类似的 SBUS是RISC-V

2025-01-11 23:26:36

需要2个单片机同时都能访问SRAM,需要把2个单片机的总线通过开关进行切换,查了SN74CBTLV16292 芯片,是属于FET multiplexer/demultiplexer ,头一次用这个

2025-01-09 08:24:26

电子发烧友App

电子发烧友App

评论