更上一层楼???

改动很小,也就是把光模块的扇出改成激光孔的设计,客户就“偷偷瞒着我们”自己修改并投了板。花了大价钱用了激光孔的加工工艺,等板子回来的一刻,心情肯定是激动万分了,期待测试出来的性能更好。但是

2024-03-19 14:53:25

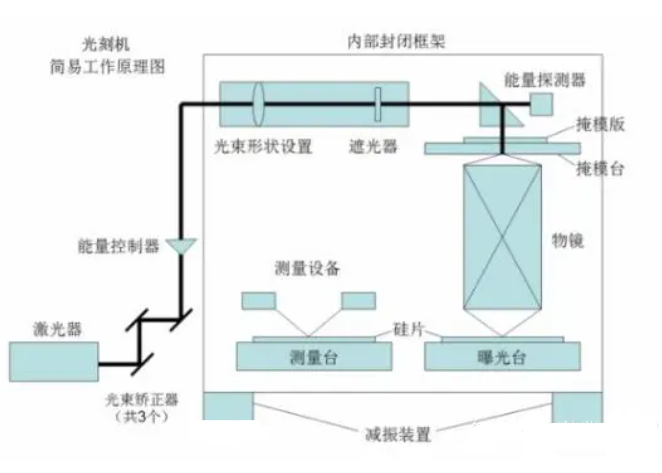

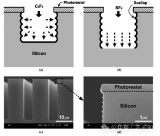

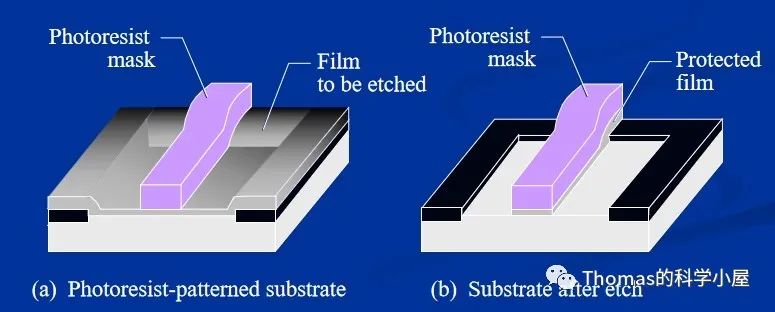

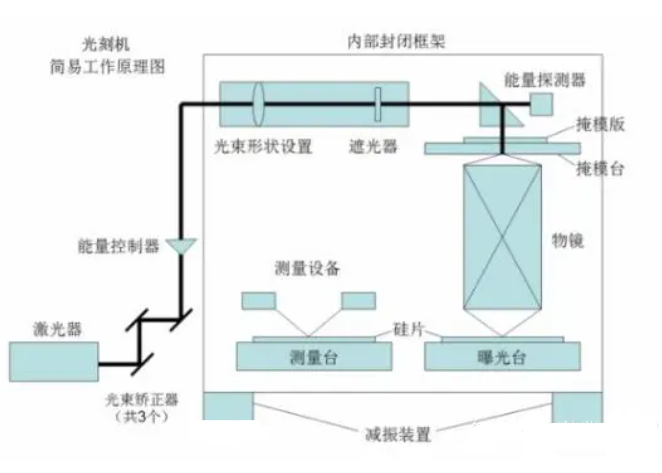

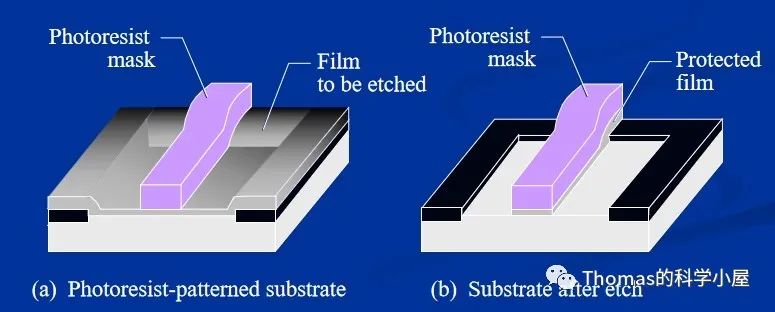

刻蚀机的刻蚀过程和传统的雕刻类似,先用光刻技术将图形形状和尺寸制成掩膜,再将掩膜与待加工物料模组装好,将样品置于刻蚀室内,通过化学腐蚀或物理磨蚀等方式将待加工物料表面的非掩膜区域刻蚀掉,以得到所需的凹槽和沟槽。

2024-03-11 15:38:24 459

459

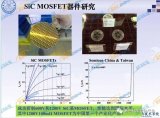

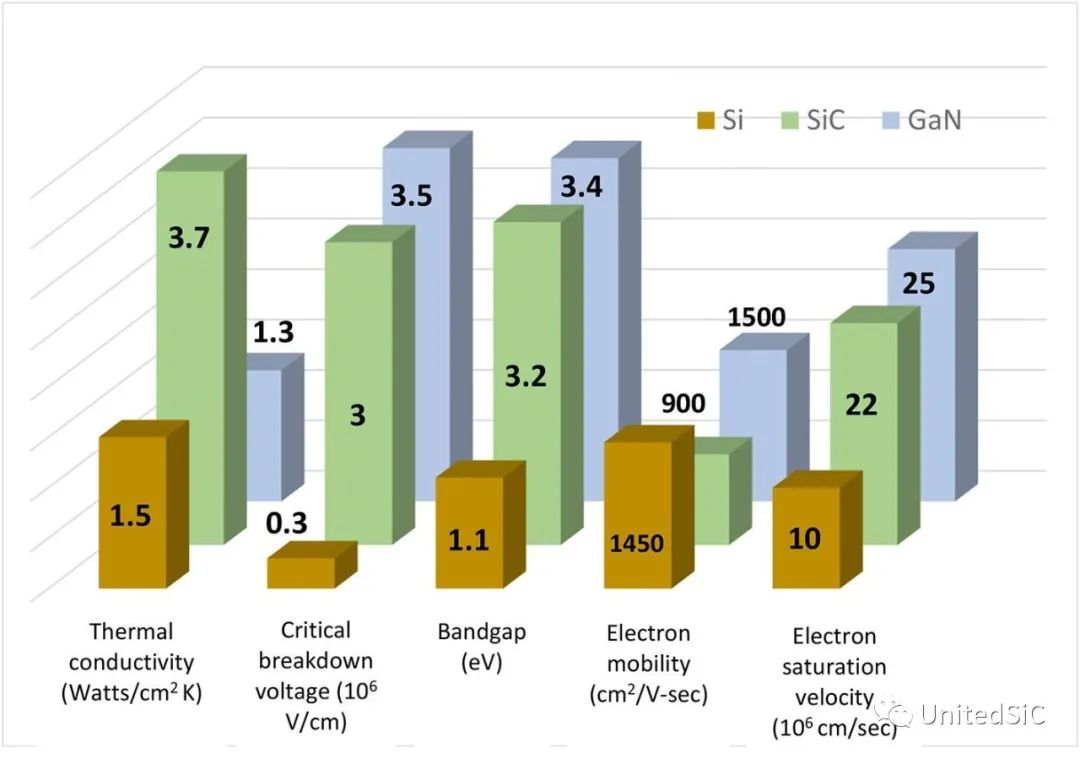

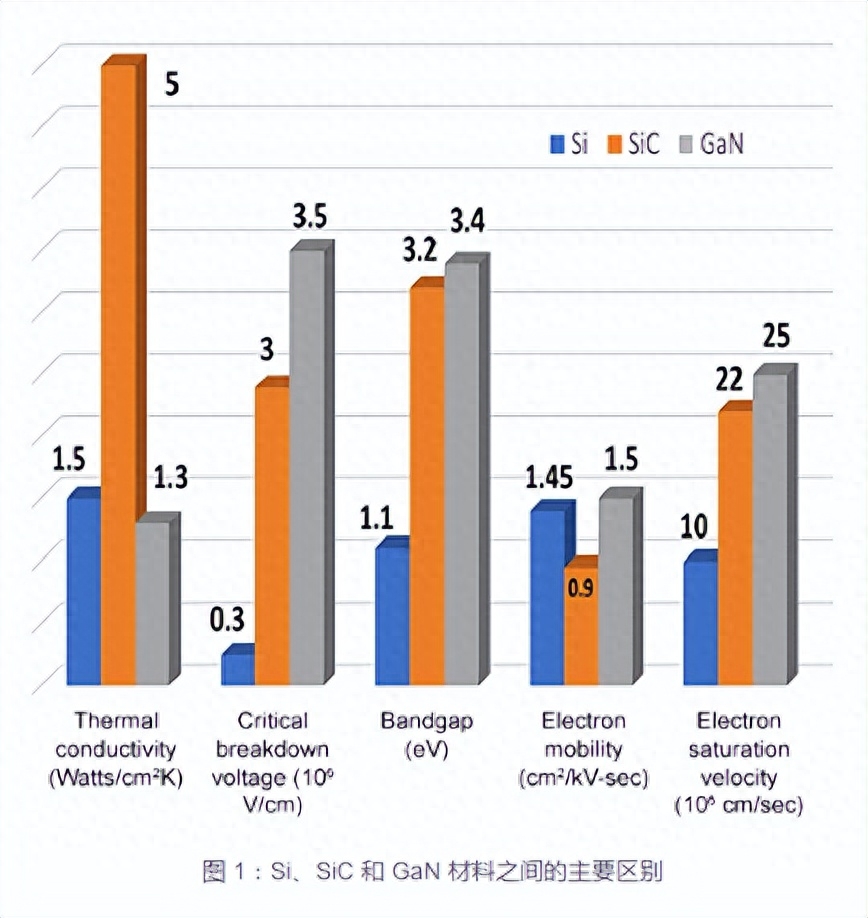

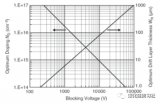

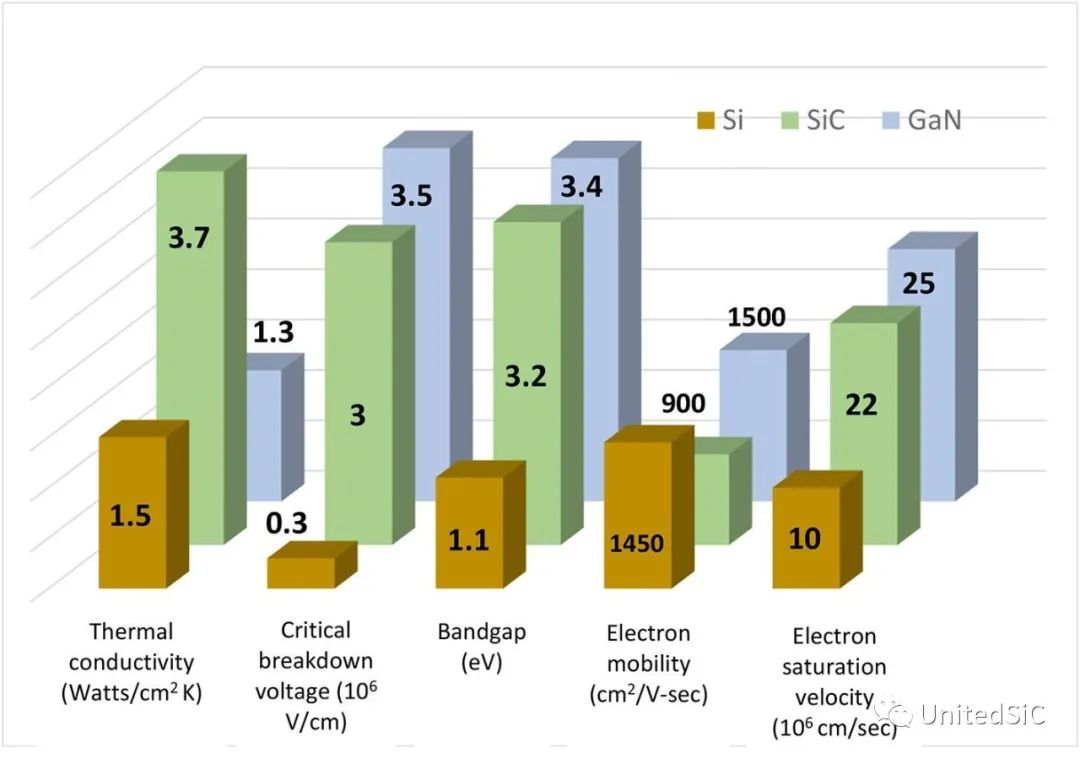

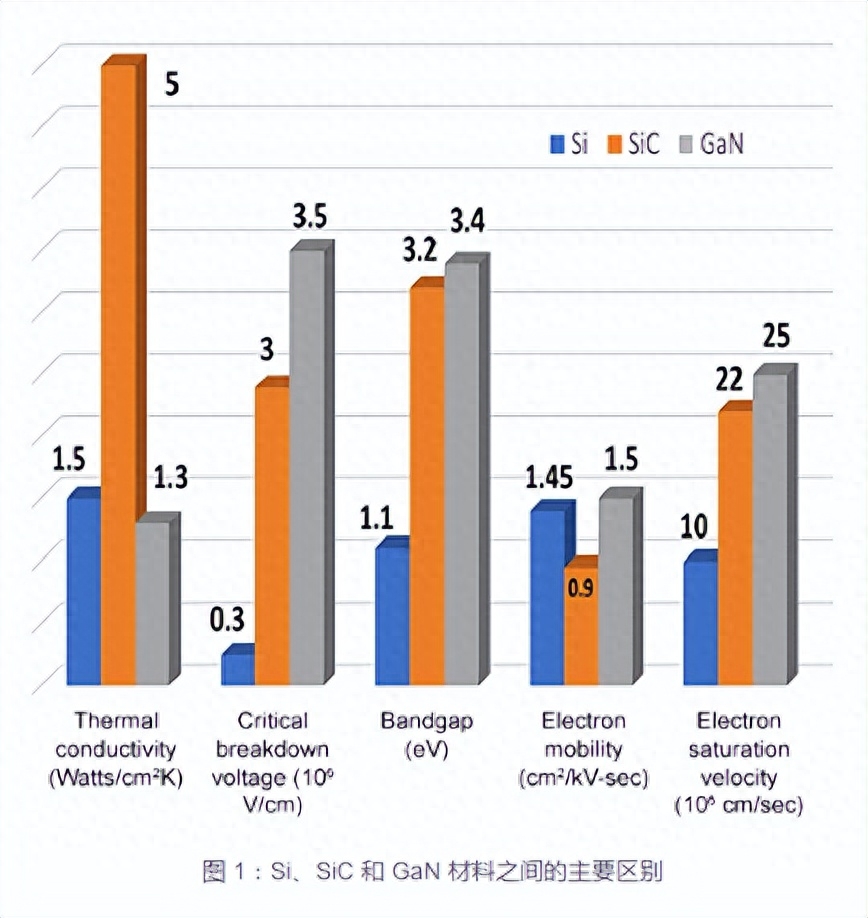

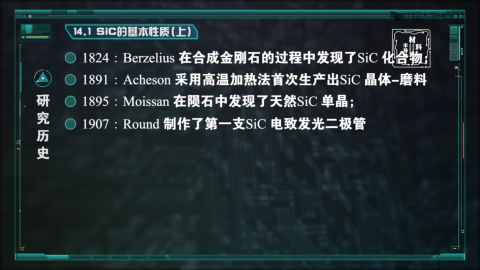

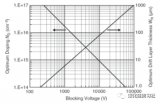

SiC器件的核心优势在于其宽禁带、高热导率、以及高击穿电压。具体来说,SiC的禁带宽度是硅的近3倍,这意味着在高温下仍可保持良好的电性能;其热导率是硅的3倍以上,有利于高功率应用中的热管理。

2024-03-08 10:27:15 42

42

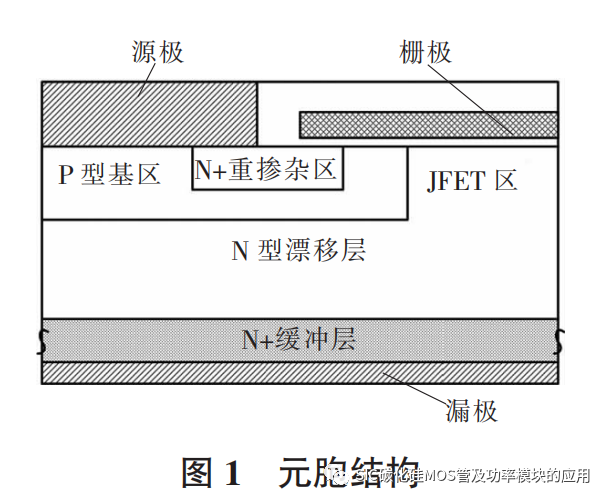

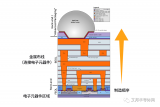

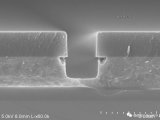

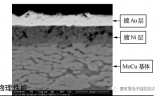

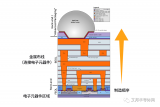

共读好书 杜隆纯 何勇 刘洪伟 刘晓鹏 (湖南国芯半导体科技有限公司 湖南省功率半导体创新中心) 摘要: 针对SiC功率器件封装的高性能和高可靠性要求,文章研究了芯片双面银烧结技术与粗铜线超声键合

2024-03-05 08:41:47 104

104

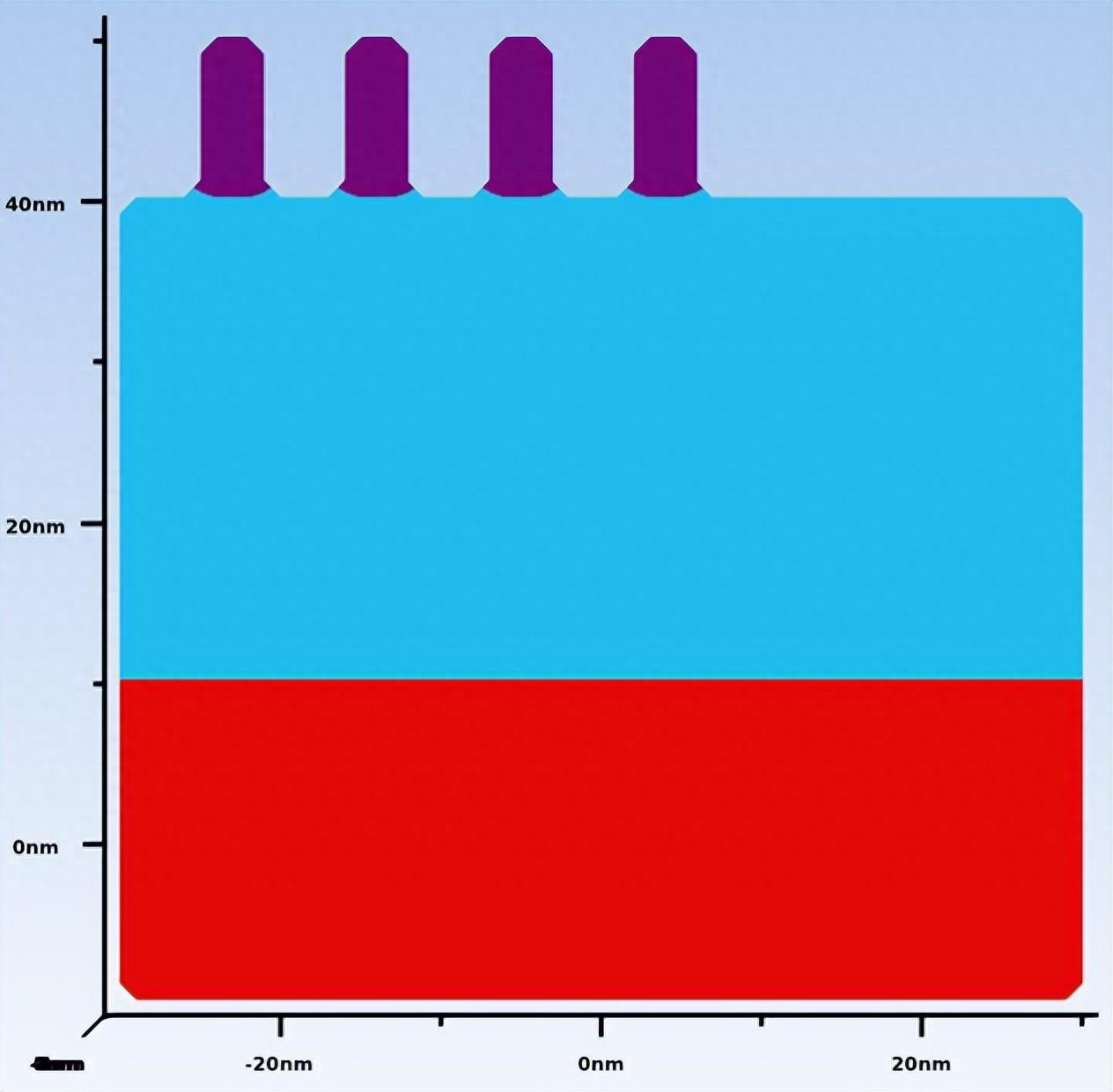

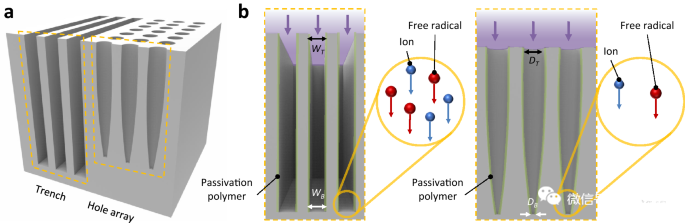

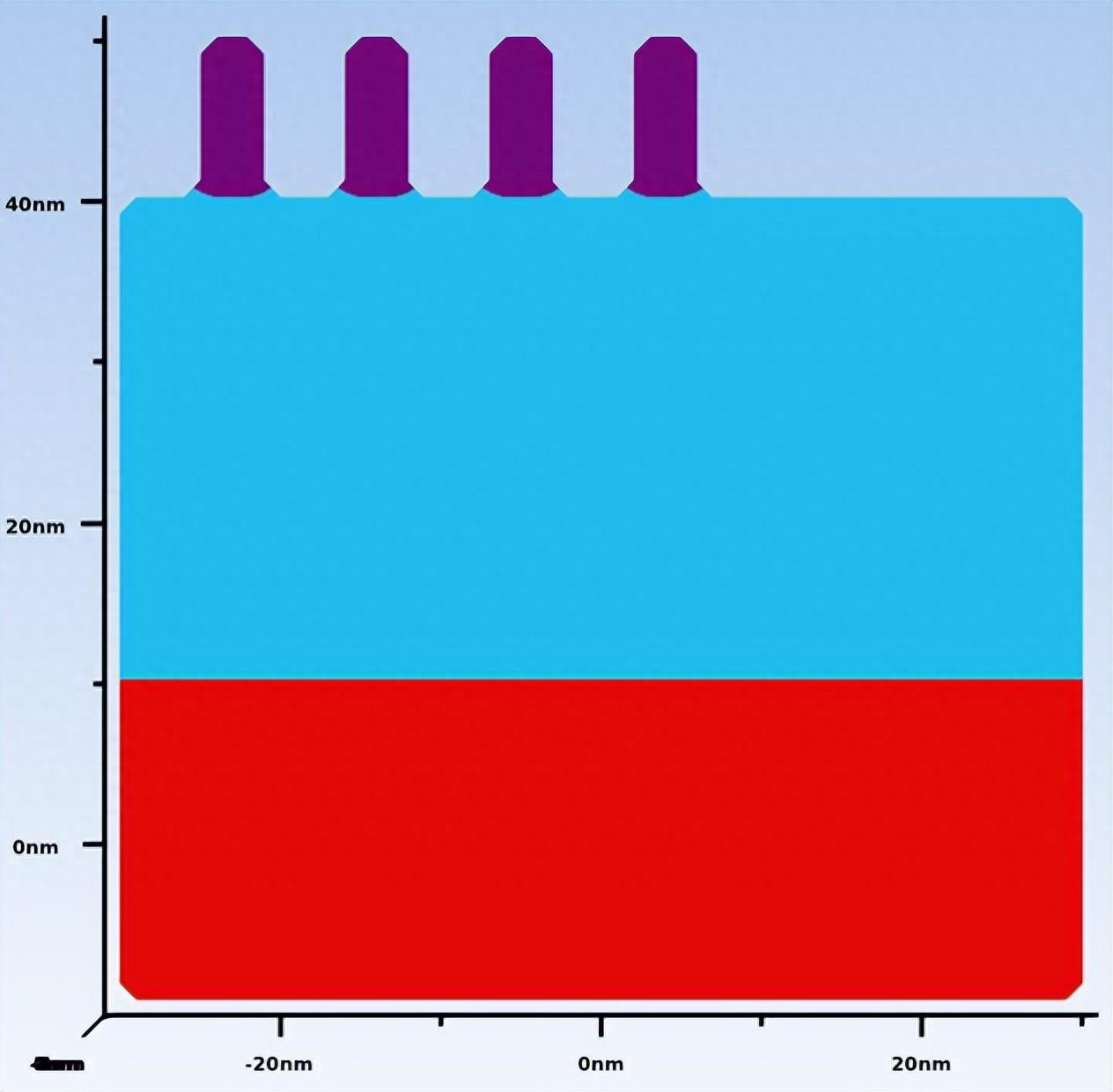

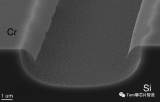

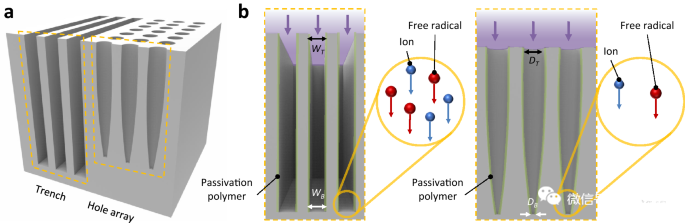

的 2.5D/3D 封装技术可以实现芯片之间的高速、低功耗和高带宽的信号传输。常见的垂直 TSV 的制造工艺复杂,容易造成填充缺陷。锥形 TSV 的侧壁倾斜,开口较大,有利于膜层沉积和铜电镀填充,可降低工艺难度和提高填充质量。在相对易于实现的刻蚀条件下制备

2024-02-25 17:19:00 119

119

影响深硅刻蚀的关键参数有:气体流量、上电极功率、下电极功率、腔体压力和冷却器。

2024-02-25 10:44:39 283

283

影响深硅刻蚀的关键参数有:气体流量、上电极功率、下电极功率、腔体压力和冷却器。

2024-02-25 10:40:16 19

19

在半导体加工工艺中,常听到的两个词就是光刻(Lithography)和刻蚀(Etching),它们像俩兄弟一样,一前一后的出现,有着千丝万缕的联系,这一节介绍半导体刻蚀工艺。

2024-01-26 10:01:58 547

547

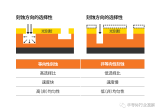

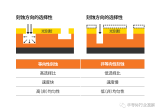

干法刻蚀技术是一种在大气或真空条件下进行的刻蚀过程,通常使用气体中的离子或化学物质来去除材料表面的部分,通过掩膜和刻蚀参数的调控,可以实现各向异性及各向同性刻蚀的任意切换,从而形成所需的图案或结构

2024-01-20 10:24:56 1106

1106

使用SEMulator3D®工艺步骤进行刻蚀终点探测 作者:泛林集团 Semiverse Solutions 部门软件应用工程师 Pradeep Nanja 介绍 半导体行业一直专注于使用先进的刻蚀

2024-01-19 16:02:42 128

128

对DRIE刻蚀,是基于氟基气体的高深宽比硅刻蚀技术。与RIE刻蚀原理相同,利用硅的各向异性,通过化学作用和物理作用进行刻蚀。不同之处在于,两个射频源:将等离子的产生和自偏压的产生分离

2024-01-14 14:11:59 510

510

在红外探测器的制造技术中,台面刻蚀是完成器件电学隔离的必要环节。

2024-01-08 10:11:01 206

206

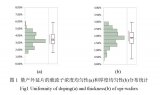

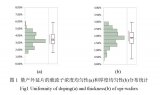

探索SiC外延层的掺杂浓度控制与缺陷控制,揭示其在高性能半导体器件中的关键作用。

2024-01-08 09:35:41 623

623

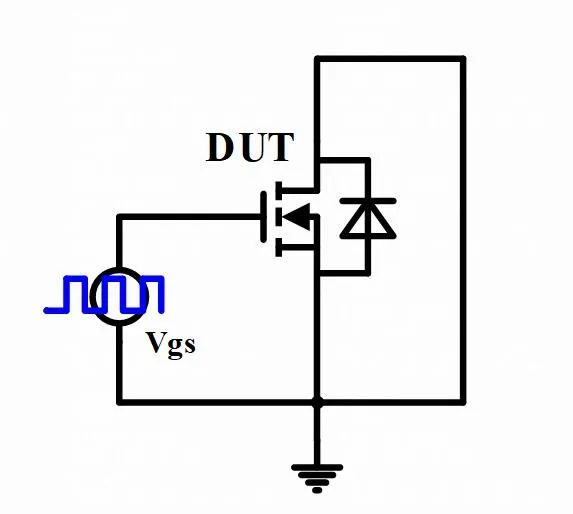

等大功率领域,能显著提高效率,降低装置体积。在这些应用领域中,对功率器件的可靠性要求很高,为此,针对自主研制的3300V SiC MOSFET 开展栅氧可靠性研究。首先,按照常规的评估技术对其进行了高温

2024-01-04 09:41:54 594

594

摘要:论述了传统的集成电路装片工艺面临的挑战以及现有用DAF膜(DieAttachmentFilm,装片胶膜)技术进行装片的局限性;介绍了一种先进的、通过喷雾结合旋转的涂胶模式制备晶圆背面

2023-12-30 08:09:58 337

337

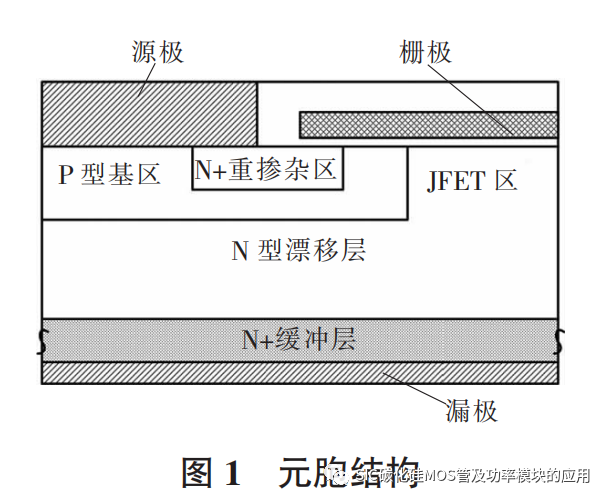

SiC具有高效节能、稳定性好、工作频率高、能量密度高等优势,SiC沟槽MOSFET(UMOSFET)具有高温工作能力、低开关损耗、低导通损耗、快速开关速度等特点

2023-12-27 09:34:56 473

473

TOPCon 电池的制备工序包括清洗制绒、正面硼扩散、BSG 去除和背面刻蚀、氧化层钝化接触制备、正面氧化铝沉积、正背面氮化硅沉积、丝网印刷、烧结和测试分选,约 12 步左右。从技术路径角度:LPCVD 方式为目前量产的主流工艺,预计 PECVD 路线有望成为未来新方向。

2023-12-26 14:59:11 2707

2707

SiC材料具有优异的高温稳定性、耐腐蚀性、热导性能和机械强度等优势,因此受到广泛关注和应用。

2023-12-26 10:13:44 462

462

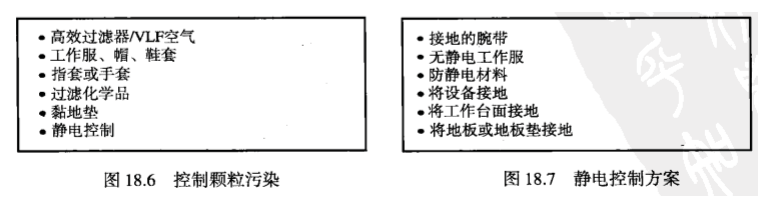

合的生产工艺就直接影响了HDI板成品的可靠性,压合的方法也尤为重要,本文主要介绍HDI(盲、埋孔)板的压合工艺问题。

机械盲孔板压合

压合是利用高温高压使半固化片受热融化,并使其流动,再转变为固化片

2023-12-25 14:09:38

在新能源产业强劲需求下,全球SiC产业步入高速成长期,推升了对SiC衬底产能的需求。

2023-12-19 10:09:18 294

294

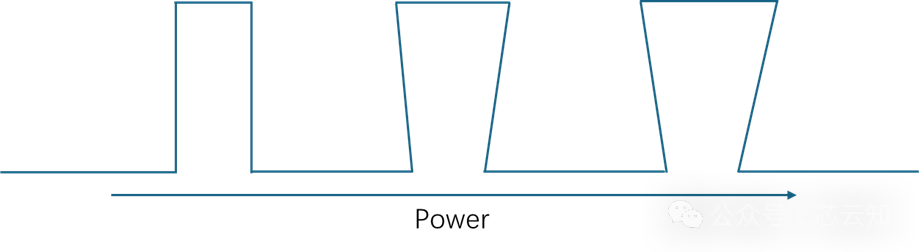

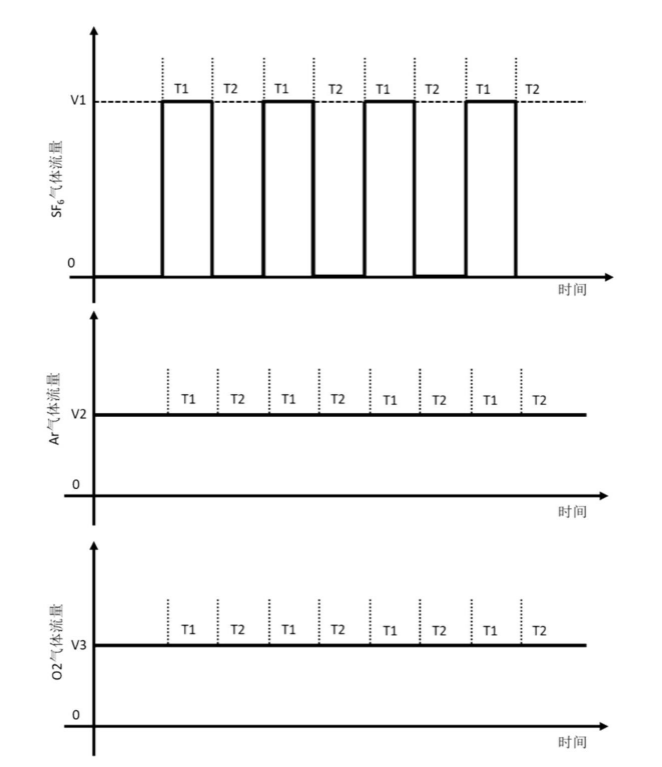

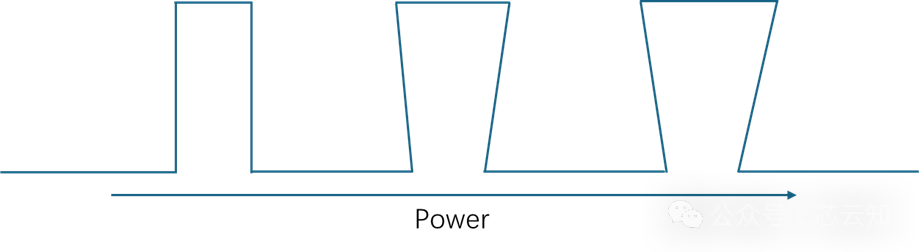

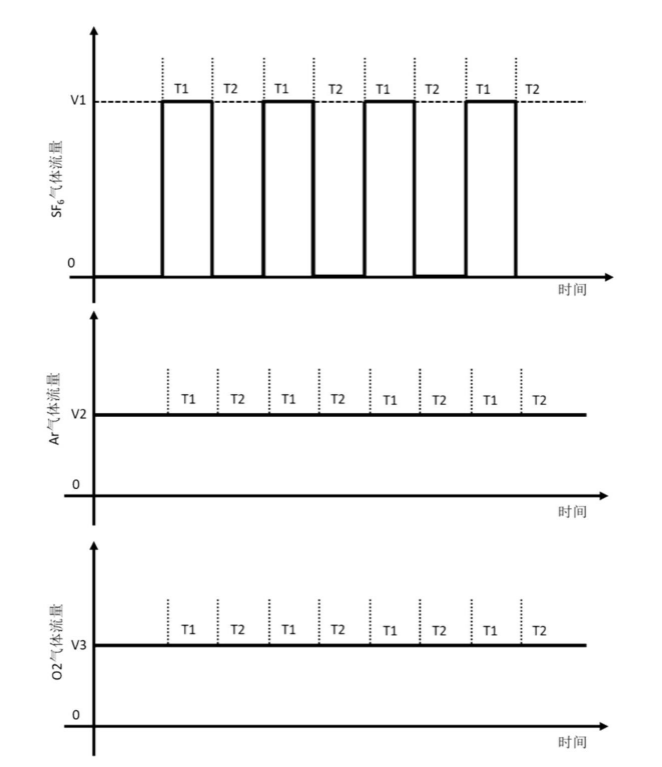

该专利详细阐述了一种针对含硅有机介电层的高效刻蚀方法及相应的半导体工艺设备。它主要涉及到通过交替运用至少两个刻蚀步骤来刻蚀含硅有机介电层。这两个步骤分别为第一刻蚀步骤和第二刻蚀步骤。

2023-12-06 11:58:16 370

370

W刻蚀工艺中使用SF6作为主刻步气体,并通过加入N2以增加对光刻胶的选择比,加入O2减少碳沉积。在W回刻工艺中分为两步,第一步是快速均匀地刻掉大部分W,第二步则降低刻蚀速率减弱负载效应,避免产生凹坑,并使用对TiN有高选择比的化学气体进行刻蚀。

2023-12-06 09:38:53 1536

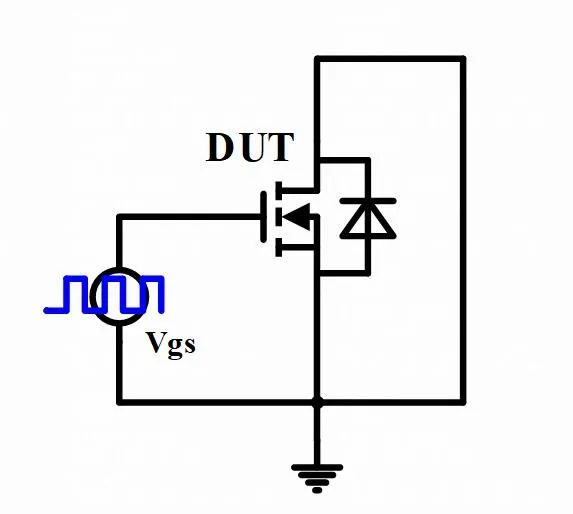

1536 SiC MOSFET AC BTI 可靠性研究

2023-11-30 15:56:02 345

345

还没使用SiC FET?快来看看本文,秒懂SiC FET性能和优势!

2023-11-29 16:49:23 273

273

在晶圆生产工艺的结尾,有些晶圆需要被减薄(晶圆减薄)才能装进特定的封装体重,以及去除背面损伤或结;对于有将芯片用金-硅共晶封装中的芯片背面要求镀一层金(背面金属化,简称背金);

2023-11-29 12:31:26 203

203

半导体前端工艺(第四篇):刻蚀——有选择性地刻蚀材料,以创建所需图形

2023-11-27 16:54:26 256

256

湿法刻蚀由于成本低、操作简单和一些特殊应用,所以它依旧普遍。

2023-11-27 10:20:17 452

452

合封芯片工艺是一种先进的芯片封装技术,将多个芯片或不同的功能的电子模块封装在一起,从而形成一个系统或子系统。合封芯片更容易实现更复杂、更高效的任务。本文将从合封芯片工艺的工作原理、应用场景、技术要点等方面进行深入解读。

2023-11-24 17:36:32 332

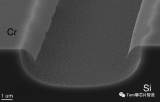

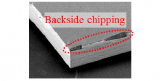

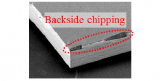

332 近日,一家日本厂商发布了一种全新的SiC晶圆划片工艺,与传统工艺相比,这项技术可将划片速度提升100倍,而且可以帮助SiC厂商增加13%的芯片数量。

2023-11-21 18:15:09 901

901

在芯片制程中,很多金属都能用等离子的方法进行刻蚀,例如金属Al,W等。但是唯独没有听说过干法刻铜工艺,听的最多的铜互连工艺要数双大马士革工艺,为什么?

2023-11-14 18:25:33 2618

2618

但是里面也有几个关键的工艺参数需要控制的。同样Etch GaAs也可以用ICP干法刻蚀的工艺,比湿法工艺效果要好些,侧壁也垂直很多。

2023-11-14 09:31:29 406

406 晶圆承载系统是指针对晶圆背面减薄进行进一步加工的系统,该工艺一般在背面研磨前使用。晶圆承载系统工序涉及两个步骤:首先是载片键合,需将被用于硅通孔封装的晶圆贴附于载片上;其次是载片脱粘,即在如晶圆背面凸点制作等流程完工后,将载片分离。

2023-11-13 14:02:49 1410

1410

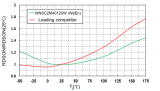

点击蓝字 关注我们 对于高压开关电源应用,碳化硅或 SiC MOSFET 与传统硅 MOSFET 和 IGBT 相比具有显著优势。SiC MOSFET 很好地兼顾了高压、高频和开关性能优势。它是电压

2023-11-02 19:10:01 361

361

下面将对于SiC MOSFET和SiC SBD两个系列,进行详细介绍

2023-11-01 14:46:19 736

736

为什么TPS54331DR这个DCDC芯片这么多人用的,有什么优势?

2023-10-27 06:13:48

碳化硅(SiC)技术已达到临界点,即不可否认的优势推动技术快速采用的状态。 如今,出于多种原因,希望保持竞争力并降低长期系统成本的设计人员正在转向基于SiC的技术,其中包括: 降低总拥有

2023-10-13 09:24:17 824

824 刻蚀(或蚀刻)是从晶圆表面去除特定区域的材料以形成相应微结构。但是,在目标材料被刻蚀时,通常伴随着其他层或掩膜的刻蚀。

2023-10-07 14:19:25 2067

2067

有过深硅刻蚀的朋友经常会遇到这种情况:在一片晶圆上不同尺寸的孔或槽刻蚀速率是不同的。

2023-10-07 11:29:17 1446

1446

,华润微电子在宽禁带半导体领域匠心深耕,利用全产业链优势,从产品设计、制造工艺、封装技术和系统应用等方面大力推进SiC器件产品产业化。华润微SiC SBD系列产品具有可媲美国际先进水平的卓越产品性能,均已

2023-10-07 10:12:26

在半导体制造中,刻蚀工序是必不可少的环节。而刻蚀又可以分为干法刻蚀与湿法刻蚀,这两种技术各有优势,也各有一定的局限性,理解它们之间的差异是至关重要的。

2023-09-26 18:21:00 3305

3305

在半导体制程工艺中,有很多不同名称的用于移除多余材料的工艺,如“清洗”、“刻蚀”等。如果说“清洗”工艺是把整张晶圆上多余的不纯物去除掉,“刻蚀”工艺则是在光刻胶的帮助下有选择性地移除不需要的材料,从而创建所需的微细图案。半导体“刻蚀”工艺所采用的气体和设备,在其他类似工艺中也很常见。

2023-09-24 17:42:03 995

995

硅碳化物(SiC)技术已经达到了临界点,即无可否认的优势推动一项技术快速被采用的状态。

2023-09-07 16:13:00 659

659

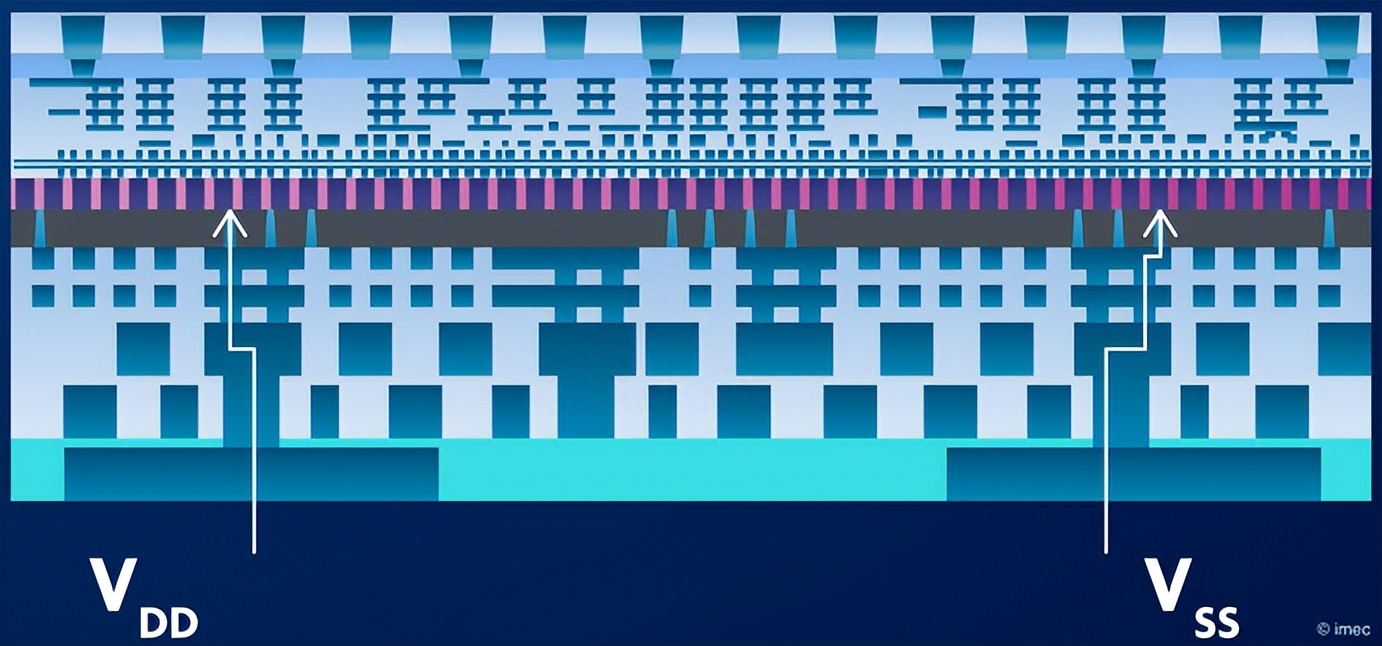

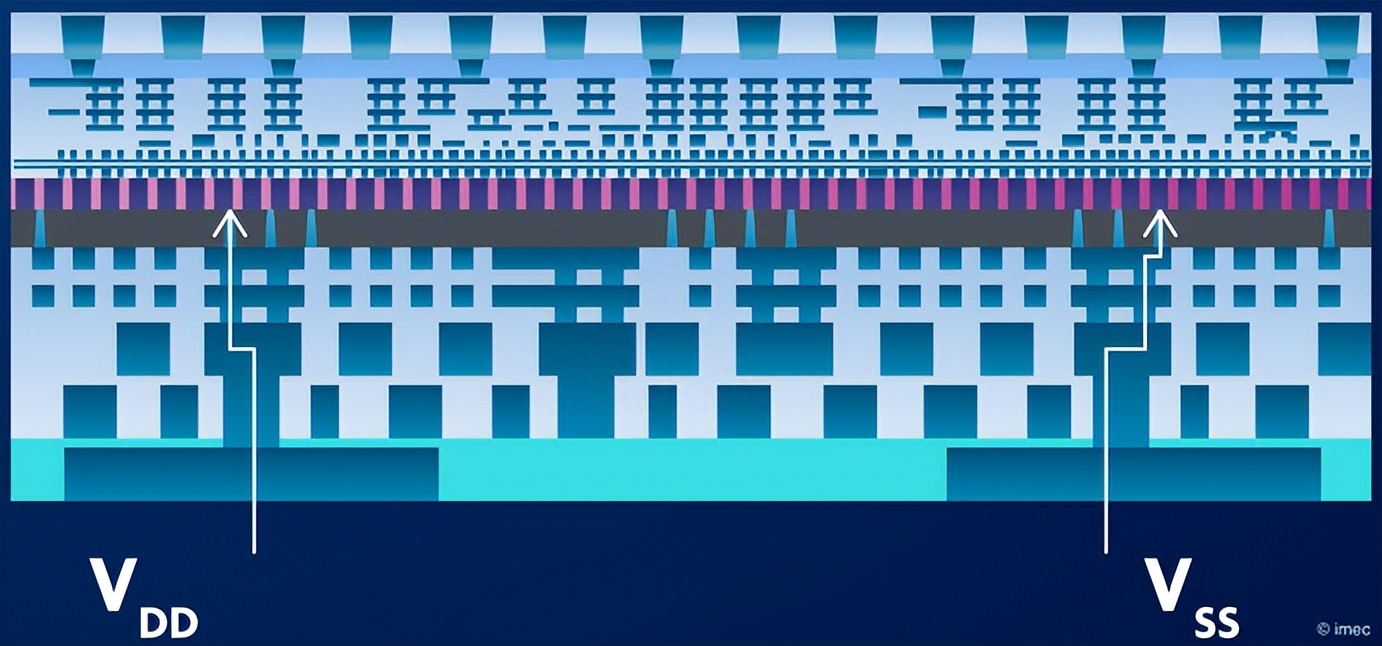

,整个配电网络被移至晶圆的背面。硅通孔(TSV)将电源直接从背面传送到正面,而无需电子穿过芯片正面上日益复杂的后道工序(BEOL)堆栈。 图1. 背面供电网络的示意图,该网络允许将电力传输与信号网络解耦。 背面供电网络(BSPDN)的目标是缓解

2023-09-05 16:39:38 464

464

背面电力传输打破了在硅晶圆正面处理信号和电力传输网络的长期传统。通过背面供电,整个配电网络被移至晶圆的背面。硅通孔 (TSV) 将电源直接从背面传送到正面,而无需电子穿过芯片正面日益复杂的后道工序 (BEOL) 堆栈。

2023-08-30 10:34:20 547

547

电子发烧友网站提供《SiC应用优势及趋势.pdf》资料免费下载

2023-08-29 16:24:51 1

1 湿法刻蚀由于精度较差,只适用于很粗糙的制程,但它还是有优点的,比如价格便宜,适合批量处理,酸槽里可以一次浸泡25张硅片,所以有些高校和实验室,还在用湿法做器件,芯片厂里也会用湿法刻蚀来显露表面缺陷(defect),腐蚀背面多晶硅。

2023-08-28 09:47:44 890

890

识别,从而显著提高系统性能。碲镉汞材料、量子阱材料和锑化物Ⅱ类超晶格材料均可用于制备双色红外探测器。其中,InAs/GaSb Ⅱ类超晶格材料因其带隙灵活可调、电子有效质量更大、大面积均匀性高等特点以及成本优势,成为制备双色

2023-08-25 09:16:42 886

886

光刻蚀(Photolithography)是一种在微电子和光电子制造中常用的加工技术,用于制造微细结构和芯片元件。它的基本原理是利用光的化学和物理作用,通过光罩的设计和控制,将光影投射到光敏材料上,形成所需的图案。

2023-08-24 15:57:42 2265

2265 前言新能源汽车依旧火热,今年上半年国内销量突破370万辆,比亚迪、特斯拉、丰田、现代、吉利、上海大众、日产等车企都已经在引入SIC器件。为何车企都采用SiC器件?SiC器件具备哪些优势?碳化硅

2023-08-17 16:41:23 816

816

PVP可以在刻蚀过程中形成一层保护性的膜,降低刻蚀剂对所需刻蚀材料的腐蚀作用。它可以填充材料表面的裂缝、孔洞和微小空隙,并防止刻蚀剂侵入。这样可以减少不需要的蚀刻或损伤,提高刻蚀的选择性。

2023-08-17 15:39:39 2855

2855 在半导体前端工艺第三篇中,我们了解了如何制作“饼干模具”。本期,我们就来讲讲如何采用这个“饼干模具”印出我们想要的“饼干”。这一步骤的重点,在于如何移除不需要的材料,即“刻蚀(Etching)工艺”。

2023-08-10 15:06:10 505

505 刻蚀(Etching)的目的是在材料表面上刻出所需的图案和结构。刻蚀的原理是利用化学反应或物理过程,通过移除材料表面的原子或分子,使材料发生形貌变化。

2023-08-01 16:33:38 3904

3904 电子发烧友网报道(文/周凯扬)在半导体制造的各路工序中,尤其是前道工序中,技术难度最大的主要三大流程当属光刻、刻蚀和薄膜沉积了。这三大工艺的先进程度直接决定了晶圆厂所能实现的最高工艺节点,所用产品

2023-07-30 03:24:48 1556

1556

刻蚀和蚀刻实质上是同一过程的不同称呼,常常用来描述在材料表面上进行化学或物理腐蚀以去除或改变材料的特定部分的过程。在半导体制造中,这个过程常常用于雕刻芯片上的细微结构。

2023-07-28 15:16:59 4138

4138 最近有许多正在全球范围内研究和开发的技术,例如晶体管GAA(Gate All around)、背面供电以及3D IC。

2023-07-26 18:21:58 1843

1843

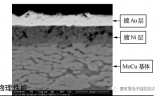

及能谱仪分析接头的显微组织、元素分布,通过X射线检测仪测定接头的孔洞率,研究GaAs芯片背面和MoCu基板表面的镀层与焊料之间的相互作用以及焊缝的凝固过程。GaAs芯片背面的Au层部分溶解在AuSn焊料

2023-07-15 14:01:42 1276

1276

第一种是间歇式刻蚀方法(BOSCH),即多次交替循环刻蚀和淀积工艺,刻蚀工艺使用的是SF6气体,淀积工艺使用的是C4F8气体

2023-07-14 09:54:46 3213

3213

背面实施流程已通过成功的 SF2 测试芯片流片得到验证。这是 2nm 设计的一项关键功能,但可能会受到三星、英特尔和台积电缺乏布线的限制,而是在晶圆背面布线并使用过孔连接电源线。

2023-07-05 09:51:37 460

460 在上一篇文章,我们介绍了光刻工艺,即利用光罩(掩膜)把设计好的电路图形绘制在涂覆了光刻胶的晶圆表面上。下一步,将在晶圆上进行刻蚀工艺,以去除不必要的材料,只保留所需的图形。

2023-06-28 10:04:58 843

843

图案化工艺包括曝光(Exposure)、显影(Develope)、刻蚀(Etching)和离子注入等流程。其中,刻蚀工艺是光刻(Photo)工艺的下一步,用于去除光刻胶(Photo Resist

2023-06-26 09:20:10 816

816

英特尔表示,它是业内第一个在类似产品的测试芯片上实现背面供电的公司,实现了推动世界进入下一个计算时代所需的性能。PowerVia 将于 2024 年上半年在英特尔 20A 工艺节点上推出,正是英特尔业界领先的背面供电解决方案。它通过将电源路由移动到晶圆的背面,解决了面积缩放中日益严重的互连瓶颈问题。

2023-06-20 15:39:06 326

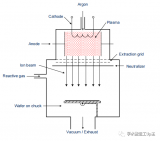

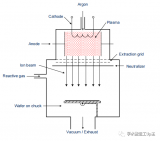

326 离子束蚀刻 (Ion beam etch) 是一种物理干法蚀刻工艺。由此,氩离子以约1至3keV的离子束辐射到表面上。由于离子的能量,它们会撞击表面的材料。晶圆垂直或倾斜入离子束,蚀刻过程是绝对

2023-06-20 09:48:56 3989

3989

基于SiC器件的电力电子变流器研究

2023-06-20 09:36:23 410

410

在半导体制程工艺中,有很多不同名称的用于移除多余材料的工艺,如“清洗”、“刻蚀”等。如果说“清洗”工艺是把整张晶圆上多余的不纯物去除掉,“刻蚀”工艺则是在光刻胶的帮助下有选择性地移除不需要的材料,从而创建所需的微细图案。半导体“刻蚀”工艺所采用的气体和设备,在其他类似工艺中也很常见。

2023-06-15 17:51:57 1176

1176

时,,另一次是其它非盘中孔的电镀。按照IPC-A-6012里面的规定,最小的过孔孔铜二级是18um,平均孔铜是20um,三级是最小20um,平均孔铜是25um。如果按照IPC二级标准,使用1/3OZ基铜

2023-06-14 16:33:40

光刻工艺后,在硅片或晶圆上形成了光刻胶的图形,下一步就是刻蚀。

2023-06-08 10:52:35 3314

3314

英特尔率先在产品级芯片上实现背面供电技术,使单元利用率超过90%,同时也在其它维度展现了业界领先的性能。 英特尔宣布在业内率先在产品级测试芯片上实现背面供电(backside power

2023-06-06 16:22:00 314

314 外延层是在晶圆的基础上,经过外延工艺生长出特定单晶薄膜,衬底晶圆和外延薄膜合称外延片。其中在导电型碳化硅衬底上生长碳化硅外延层制得碳化硅同质外延片,可进一步制成肖特基二极管、MOSFET、 IGBT 等功率器件,其中应用最多的是4H-SiC 型衬底。

2023-05-31 09:27:09 2823

2823

经过前端工艺处理并通过晶圆测试的晶圆将从背面研磨(Back Grinding)开始后端处理。背面研磨是将晶圆背面磨薄的工序,其目的不仅是为了减少晶圆厚度,还在于联结前端和后端工艺以解决前后两个工艺

2023-05-22 12:44:23 691

691

经过前端工艺处理并通过晶圆测试的晶圆将从背面研磨(Back Grinding)开始后端处理。背面研磨是将晶圆背面磨薄的工序,其目的不仅是为了减少晶圆厚度,还在于联结前端和后端工艺以解决前后两个工艺

2023-05-12 12:39:18 759

759

图案化工艺包括曝光(Exposure)、显影(Develope)、刻蚀(Etching)和离子注入等流程。

2023-04-28 11:24:27 1073

1073

主要讲述 PCB Layout 中焊盘和过孔的设计标准及工艺要求,包括 BGA 焊盘。

一、 过孔的设置(适用于二层板,四层板和多层板)孔的设计

过线孔:制成板的最小孔径定义取决于板厚度

2023-04-25 18:13:15

利。

工艺性设计要考虑:

a)自动化生产所需的传送边、定位孔、光学定位符号;

b)与生产效率有关的拼板;

c)与焊接合格率有关的元件封装选型、基板材质选择、组装方式、元件布局、焊盘设计、阻焊

2023-04-25 16:52:12

本篇要讲的金属布线工艺,与前面提到的光刻、刻蚀、沉积等独立的工艺不同。在半导体制程中,光刻、刻蚀等工艺,其实是为了金属布线才进行的。在金属布线过程中,会采用很多与之前的电子元器件层性质不同的配线材料(金属)。

2023-04-25 10:38:49 986

986

技术中的个工艺环节。通孔回流焊大的好处就是可以在发挥表面贴装制造工艺的优点的同时使用通孔插件来得到较好的机械连接强度。 通孔回流焊接工艺与波峰焊接工艺相比的优势 1、通孔回流焊接工艺首先是减少

2023-04-21 14:48:44

等离子体均匀性和等离子体位置的控制在未来更加重要。对于成熟的技术节点,高的产量、低的成本是与现有生产系统竞争的关键因素。如果可以制造低成本的可靠的刻蚀系统,从长远来看,可以为客户节省大量费用,有可能

2023-04-21 09:20:22 1347

1347 压力主要控制刻蚀均匀性和刻蚀轮廓,同时也能影响刻蚀速率和选择性。改变压力会改变电子和离子的平均自由程(MFP),进而影响等离子体和刻蚀速率的均匀性。

2023-04-17 10:36:43 1922

1922 的电气参量;然后研究分析了功率器件结温测量的各类方法, 并重点阐述了温敏电参数 (TSEP) 法在 SiC MOSFET 结温评估领域的应用前景, 从线性度、 灵敏度等 6 个方面对比分析了 各方

2023-04-15 10:03:06 1452

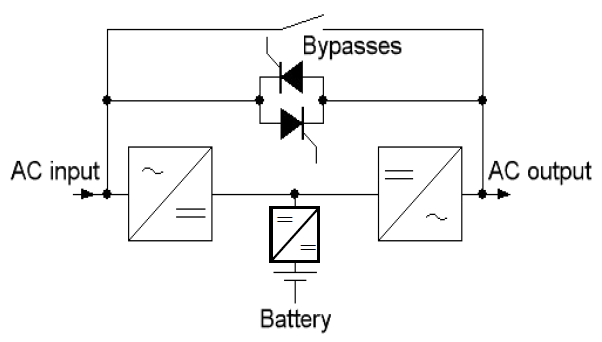

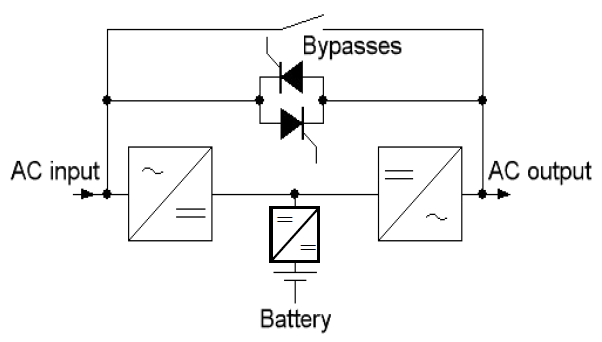

1452 我们聊了关于UPS的概念和分类,以及在线式UPS的三个工作模式。第三代宽禁带半导体WBG的诞生和发展,让很多使用Si基半导体器件的行业得到提升,今天我们就简单地聊聊SiC在UPS中的应用优势。

2023-04-14 14:35:10 788

788

金属刻蚀具有良好的轮廓控制、残余物控制,防止金属腐蚀很重要。金属刻蚀时铝中如果 有少量铜就会引起残余物问题,因为Cu Cl2的挥发性极低且会停留在晶圆表面。

2023-04-10 09:40:54 2330

2330 DRAM栅工艺中,在多晶硅上使用钙金属硅化物以减少局部连线的电阻。这种金属硅化物和多晶硅的堆叠薄膜刻蚀需要增加一道工艺刻蚀W或WSi2,一般先使用氟元素刻蚀钧金属硅化合物层,然后再使用氯元素刻蚀多晶硅。

2023-04-07 09:48:16 2198

2198 SIC438BEVB-B

2023-04-06 23:31:02

PCB生产商的通孔插装工艺模板的印刷方法有几种?

2023-04-06 16:12:14

的蓝牙模组/NBlot模组,这些不可或缺的通信模组可以像芯片一样焊接到PCB板上。这些小载板特点为:尺寸较小、单元边有整排金属化半孔,通过这些金属化半孔与母板以及元器件的引脚焊接到一起,行业内对于这种

2023-03-31 15:03:16

介绍了SIC碳化硅材料的特性,包括材料结构,晶体制备,晶体生长,器件制造工艺细节等等。。。欢迎大家一起学习

2023-03-31 15:01:48 17

17 陕西光电子先导院先进光子器件工程创新平台3月30日在西安全面启用。该平台具备光子芯片制程中的光刻、刻蚀、蒸镀等多项核心工艺,将为光子产业项目提供产品研发、中试、检测等全流程技术服务,为光子产业各类

2023-03-30 19:09:10 410

410

FinFET三维器件也可以用体硅衬底制作,这需要更好地控制单晶硅刻蚀工艺,如CD、深度和轮廓。

2023-03-30 09:39:18 2458

2458 V SiC MOSFET“S4101”和650V SiC SBD“S6203”是以裸芯片的形式提供的,采用ROHM的这些产品将有助于应用的小型化并提高模块的性能和可靠性。另外

2023-03-29 15:06:13

,大概是12um(基铜)+20um(盘中孔孔铜)+20um(非盘中孔孔铜),总的铜厚度在52um左右。从上面POFV的工艺流程中,我们可以看出第5工序有减铜的流程,但是通常铜厚不能减太多,大概在

2023-03-27 14:33:01

作为半导体制造的后工序,封装工艺包含背面研磨(Back Grinding)、划片(Dicing)、芯片键合(Die Bonding)、引线键合(Wire Bonding)及成型(Molding)等步骤。

2023-03-27 09:33:37 7222

7222

电子发烧友App

电子发烧友App

评论