英特尔率先在产品级芯片上实现背面供电技术,使单元利用率超过90%,同时也在其它维度展现了业界领先的性能。

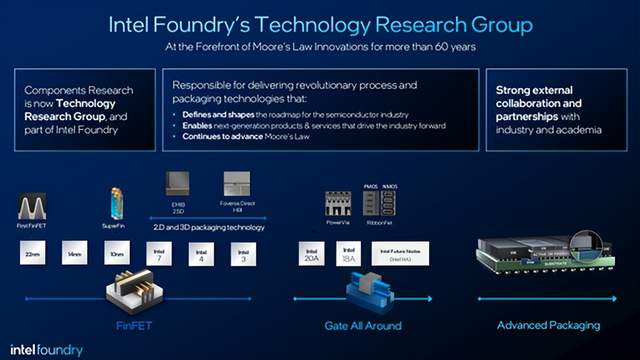

英特尔宣布在业内率先在产品级测试芯片上实现背面供电(backside power delivery)技术,满足迈向下一个计算时代的性能需求。作为英特尔业界领先的背面供电解决方案,PowerVia将于2024年上半年在Intel 20A制程节点上推出。通过将电源线移至晶圆背面,PowerVia解决了芯片单位面积微缩中日益严重的互连瓶颈问题。

英特尔技术开发副总裁Ben Sell表示:“英特尔正在积极推进‘四年五个制程节点’计划,并致力于在2030年实现在单个封装中集成一万亿个晶体管,PowerVia对这两大目标而言都是重要里程碑。通过采用已试验性生产的制程节点及其测试芯片,英特尔降低了将背面供电用于先进制程节点的风险,使得我们能领先竞争对手一个制程节点,将背面供电技术推向市场。”

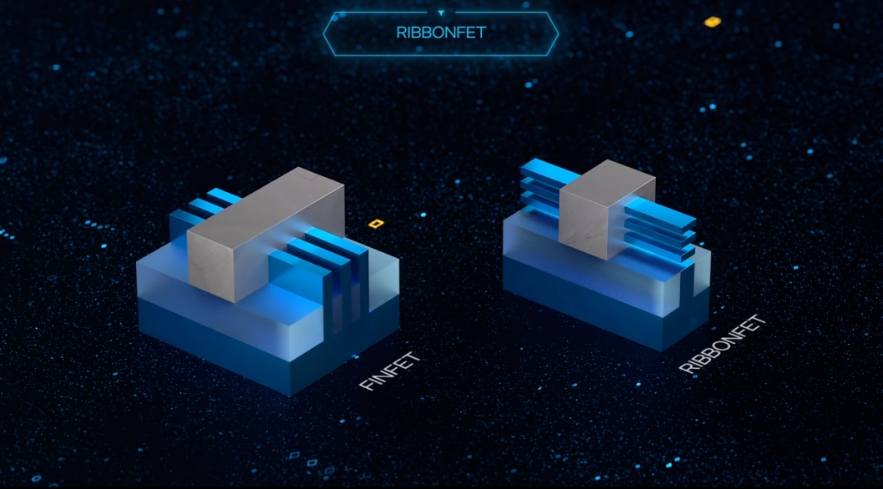

英特尔将PowerVia技术和晶体管的研发分开进行,以确保PowerVia可以被妥善地用于Intel 20A和Intel 18A制程芯片的生产中。在与同样将与Intel 20A制程节点一同推出的RibbonFET晶体管集成之前,PowerVia在其内部测试节点上进行了测试,以不断调试并确保其功能良好。经在测试芯片上采用并测试PowerVia,英特尔证实了这项技术确实能显著提高芯片的使用效率,单元利用率(cell utilization)超过90%,并有助于实现晶体管的大幅微缩,让芯片设计公司能够提升产品性能和能效。

英特尔将在于6月11日至16日在日本京都举行的VLSI研讨会上通过两篇论文展示相关研究成果。

作为大幅领先竞争对手的背面供电解决方案,PowerVia让包含英特尔代工服务(IFS)客户在内的芯片设计公司能更快地实现产品能效和性能的提升。长期以来,英特尔始终致力于推出对行业具有关键意义的创新技术,如应变硅(strained silicon)、高K金属栅极(Hi-K metal gate)和FinFET晶体管,以继续推进摩尔定律。随着PowerVia和RibbonFET全环绕栅极技术在2024年的推出,英特尔在芯片设计和制程技术创新方面将继续处于行业领先地位。

通过率先推出PowerVia技术,英特尔可帮助芯片设计公司突破日益严重的互连瓶颈。越来越多的使用场景,包括AI或图形计算,都需要尺寸更小、密度更高、性能更强的晶体管来满足不断增长的算力需求。从数十年前到现在,晶体管架构中的电源线和信号线一直都在“抢占”晶圆内的同一块空间。通过在结构上将这两者的布线分开,可提高芯片性能和能效,为客户提供更好的产品。背面供电对晶体管微缩而言至关重要,可使芯片设计公司在不牺牲资源的同时提高晶体管密度,进而显著地提高功率和性能。

此外,Intel 20A和Intel 18A制程节点将同时采用PowerVia背面供电技术和RibbonFET全环绕栅极技术。作为一种向晶体管供电的全新方式,背面供电技术也带来了散热和调试设计方面的全新挑战。

通过将PowerVia与RibbonFET这两项技术的研发分开进行,英特尔能够迅速应对上述挑战,确保能在基于Intel 20A和Intel 18A制程节点的芯片中实现PowerVia技术。英特尔开发了散热技术,以避免过热问题的出现,同时,调试团队也开发了新技术,确保这种新的晶体管设计结构在调试中出现的各种问题都能得到适当解决。因此,在集成到RibbonFET晶体管架构之前,PowerVia就已在测试中达到了相当高的良率和可靠性指标,证明了这一技术的预期价值。

PowerVia的测试也利用了极紫外光刻技术(EUV)带来的设计规则。在测试结果中,芯片大部分区域的标准单元利用率都超过90%,同时单元密度也大幅增加,可望降低成本。测试还显示,PowerVia将平台电压(platform voltage)降低了30%,并实现了6%的频率增益( frequency benefit)。PowerVia测试芯片也展示了良好的散热特性,符合逻辑微缩预期将实现的更高功率密度。

接下来,在将于VLSI研讨会上发表的第三篇论文中,英特尔技术专家Mauro Kobrinsky还将阐述英特尔对PowerVia更先进部署方法的研究成果,如同时在晶圆正面和背面实现信号传输和供电。

英特尔领先业界为客户提供PowerVia背面供电技术,并将在未来继续推进相关创新,延续了其率先将半导体创新技术推向市场的悠久历史。

审核编辑黄宇

-

芯片

+关注

关注

462文章

53530浏览量

458864 -

英特尔

+关注

关注

61文章

10275浏览量

179249

发布评论请先 登录

吉方工控荣膺英特尔中国2025市场突破奖

18A工艺大单!英特尔将代工微软AI芯片Maia 2

硬件与应用同频共振,英特尔Day 0适配腾讯开源混元大模型

英特尔先进封装,新突破

新思科技与英特尔在EDA和IP领域展开深度合作

英特尔持续推进核心制程和先进封装技术创新,分享最新进展

背面供电搭配全环绕栅极,英特尔打造芯片制造“新星组合”

详细解读英特尔的先进封装技术

英特尔代工在IEDM 2024展示多项技术突破

英特尔IEDM 2024大晒封装、晶体管、互连等领域技术突破

半导体未来三大支柱:先进封装、晶体管和互连

英特尔展示互连微缩技术突破性进展

英特尔推出全新英特尔锐炫B系列显卡

英特尔PowerVia技术率先实现芯片背面供电,突破互连瓶颈

英特尔PowerVia技术率先实现芯片背面供电,突破互连瓶颈

评论