在硬件系统设计中,通常我们关注的串扰主要发生在连接器、芯片封装和间距比较近的平行走线之间。但在某些设计中,高速差分过孔之间也会产生较大的串扰,本文对高速差分过孔之间的产生串扰的情况提供了实例仿真分析和解决方法。

2015-12-18 10:45:12 4970

4970 在高速PCB设计的学习过程中,串扰是一个需要大家掌握的重要概念。它是电磁干扰传播的主要途径,异步信号线,控制线,和I/O口走线上,串扰会使电路或者元件出现功能不正常的现象。

2022-08-22 10:45:08 4444

4444

在高速PCB设计的学习过程中,串扰是一个需要大家掌握的重要概念。它是电磁干扰传播的主要途径,异步信号线,控制线,和I/O口走线上,串扰会使电路或者元件出现功能不正常的现象。

2022-08-29 09:38:57 2560

2560

在高速PCB设计的学习过程中,串扰是一个需要大家掌握的重要概念。它是电磁干扰传播的主要途径,异步信号线,控制线,和I/O口走线上,串扰会使电路或者元件出现功能不正常的现象。 串扰(crosstalk

2022-09-05 18:55:08 3020

3020

01 . 什么是串扰? 串扰 是 PCB 的走线之间产生的不需要的噪声 (电磁耦合)。 串扰是 PCB 可能遇到的最隐蔽和最难解决的问题之一。最难搞的是,串扰一般都会发生在项目的最后阶段,而且

2023-05-23 09:25:59 8732

8732

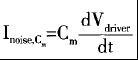

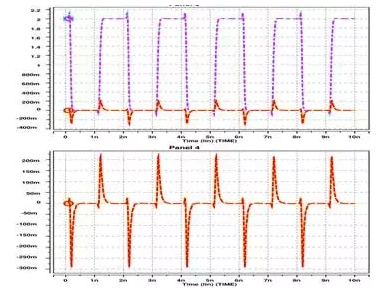

针对SiC MOSFET模块应用过程中出现的串扰问题,文章首先对3种测量差分探头的参数和测 量波形进行对比,有效减小测量误差;然后详细分析串扰引起模块栅源极出现电压正向抬升和负向峰值过大 的原因

2023-06-05 10:14:21 8497

8497

串扰在电子产品的设计中普遍存在,通过以上的分析与仿真,了解了串扰的特性,总结出以下减少串扰的方法。

2023-06-13 10:41:52 2372

2372

先来说一下什么是串扰,串扰就是PCB上两条走线,在互不接触的情况下,一方干扰另一方,或者相互干扰。

2023-09-11 14:18:42 2335

2335

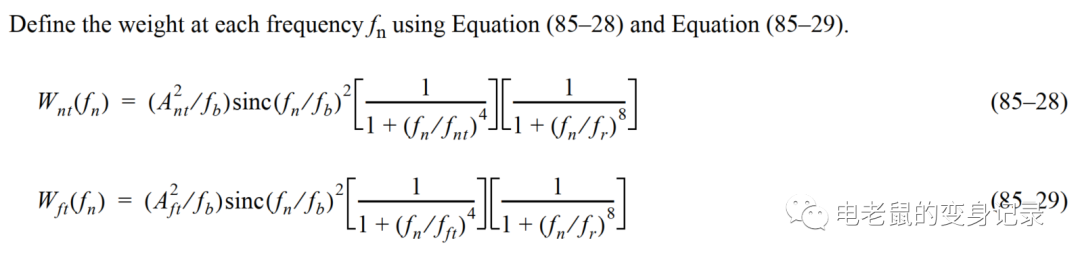

讲到串扰,基础的串扰知识比如串扰是由电场耦合和磁场耦合的共同结果啊,从串扰影响的方向来分有FEXT和NEXT这些小P就都不说了。当小P在学习一篇PCIe 5.0连接器一致性的paper里出现了ICN的字样。

2023-10-25 14:43:22 7932

7932

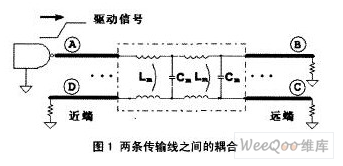

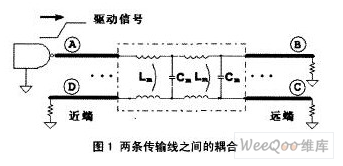

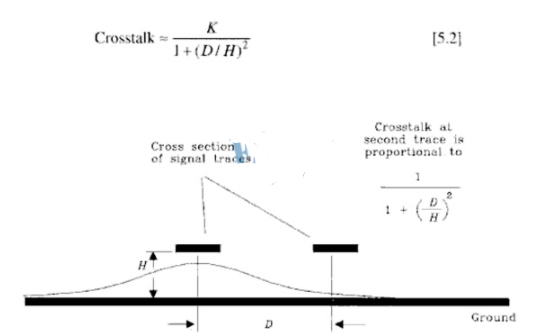

串扰是信号在传输线上传播时,由于电磁耦合而在相邻的传输线上产生不期望的电压和电流噪声,信号线的边缘场效应是导致串扰产生的根本原因。

2024-01-18 10:13:09 7438

7438

信号串扰(Crosstalk)是指在信号传输过程中,一条信号线上的信号对相邻信号线产生的干扰,这种干扰是由于电磁场耦合或直接电容、电感耦合引起的。根据耦合类型和位置的不同,信号串扰主要分为以下几类

2024-09-12 08:08:34 4568

4568

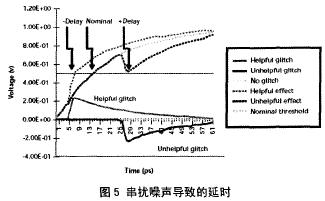

串扰是信号完整性中最基本的现象之一,在板上走线密度很高时串扰的影响尤其严重。我们知道,线性无缘系统满足叠加定理,如果受害线上有信号的传输,串扰引起的噪声会叠加在受害线上的信号,从而使其信号产生畸变

2019-05-31 06:03:14

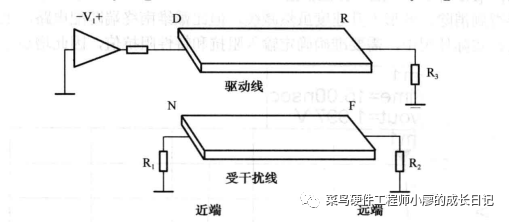

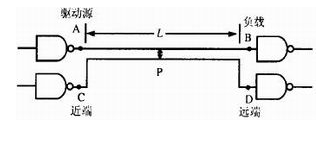

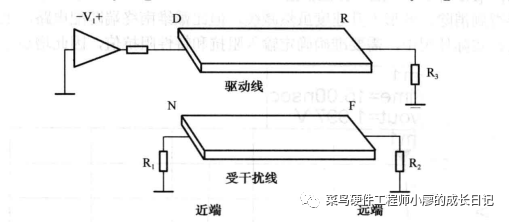

所谓串扰,是指有害信号从一个传输线耦合到毗邻传输线的现象,噪声源(攻击信号)所在的信号网络称为动态线,***扰的信号网络称为静态线。串扰产生的过程,从电路的角度分析,是由相邻传输线之间的电场(容性)耦合和磁场(感性)耦合引起,需要注意的是串扰不仅仅存在于信号路径,还与返回路径密切相关。

2019-08-02 08:28:35

高速PCB串扰分析及其最小化 1.引言 &

2009-03-20 13:56:06

的串扰进行仿真,可以在PCB实现中迅速地发现、定位和解决串扰问题。本文以Mentor公司的仿真软件HyperLynx为例对串扰进行分析。

高速设计中的仿真包括布线前的原理图仿真和布线后

2018-08-28 11:58:32

和远端串扰这种方法来研究多线间串扰问题。利用Hyperlynx,主要分析串扰对高速信号传输模型的侵害作用并根据仿真结果,获得了最佳的解决办法,优化设计目标。【关键词】:信号完整性;;反射;;串扰;;近

2010-05-13 09:10:07

在硬件系统设计中,通常我们关注的串扰主要发生在连接器、芯片封装和间距比较近的平行走线之间。但在某些设计中,高速差分过孔之间也会产生较大的串扰,本文对高速差分过孔之间的产生串扰的情况提供了实例仿真分析

2018-09-04 14:48:28

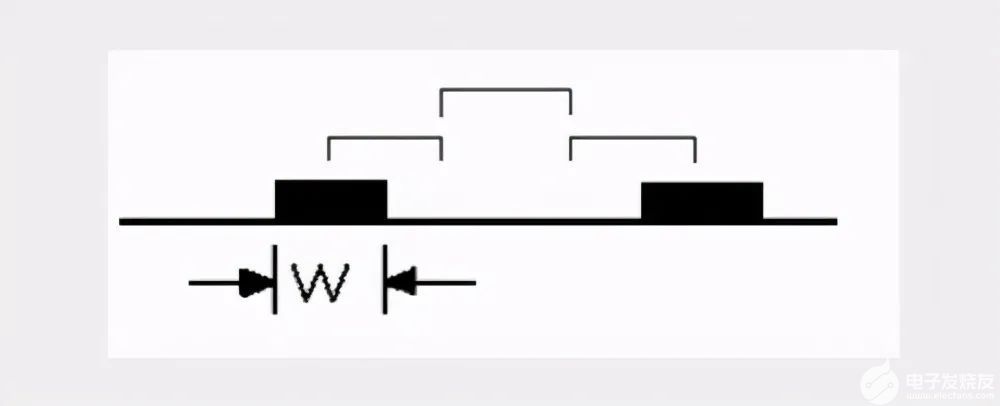

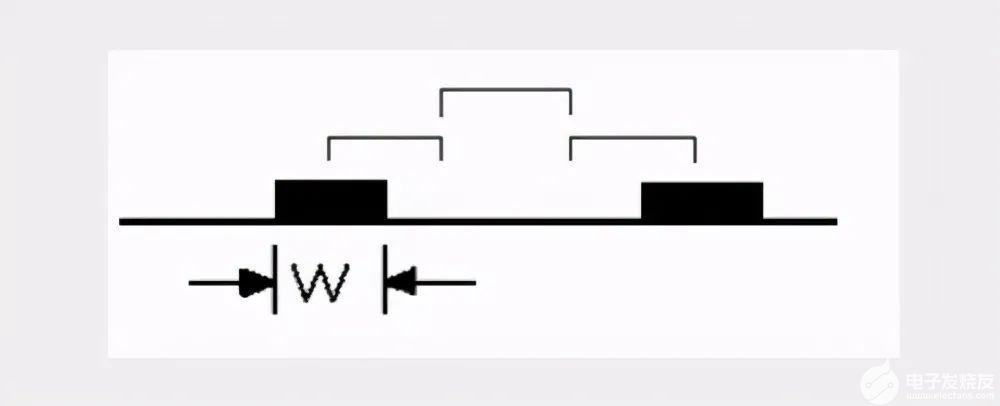

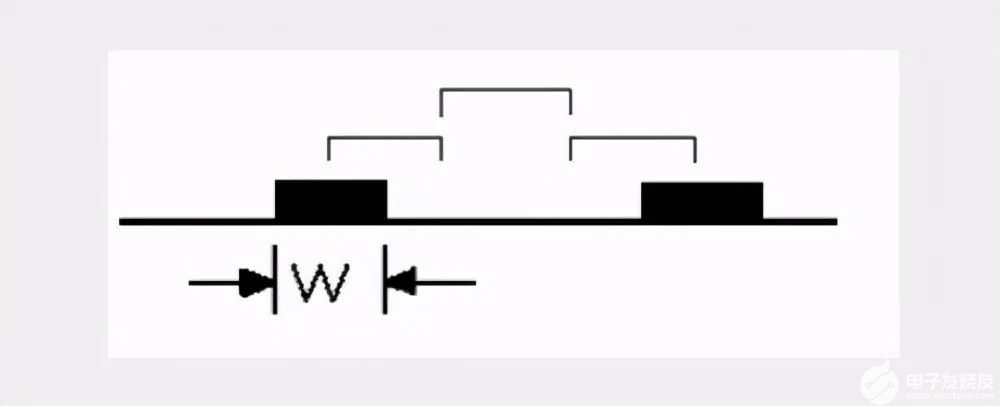

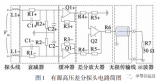

可以采用背钻的方式。图1:高速差分过孔产生串扰的情况(H》100mil, S=31.5mil )差分过孔间串扰的仿真分析下面是对一个板厚为3mm,0.8mm BGA扇出过孔pitch为31.5mil

2020-08-04 10:16:49

串扰问题产生的机理是什么高速数字系统的串扰问题怎么解决?

2021-04-25 08:56:13

高速电路信号完整性分析与设计—串扰串扰是由电磁耦合引起的,布线距离过近,导致彼此的电磁场相互影响串扰只发生在电磁场变换的情况下(信号的上升沿与下降沿)[此贴子已经被作者于2009-9-12 10:32:03编辑过]

2009-09-12 10:31:08

高速PCB设计中的信号完整性概念以及破坏信号完整性的原因高速电路设计中反射和串扰的形成原因

2021-04-27 06:57:21

PCB板上的高速信号需要进行仿真串扰吗?

2023-04-07 17:33:31

作者:一博科技SI工程师陈德恒摘要:随着电子设计领域的高速发展,产品越来越小,速率越来越高,信号完整性越来越成为一个硬件工程师需要考虑的问题。串扰,阻抗匹配等词汇也成为了硬件工程师的口头禅。电路板

2014-10-21 09:53:31

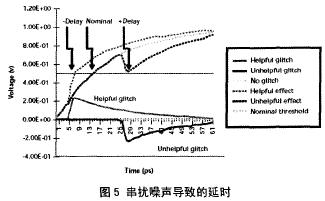

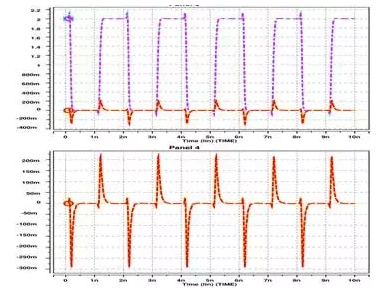

4.2,与两侧间距同为8mil。 图5 图6图6中四个电路分别为微带线的近端串扰,微带线的远端串扰,带状线的近端串扰,带状线的远端串扰。红色为攻击线上信号,蓝色为静态线串扰。我们将线长定为2000mil

2014-10-21 09:52:58

串扰极性相同,叠加增强。串扰分析的模式通常包括默认模式,三态模式和最坏情况模式分析。 默认模式类似我们实际对串扰测试的方式,即侵害网络驱动器由翻转信号驱动,受害网络驱动器保持初始状态(高电平或低电平

2020-06-13 11:59:57

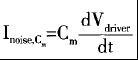

了各自的见解,比如串扰,绕线,过孔,跨分割等等。本期我们就以不同模态下的串扰对信号时延的影响继续通过理论分析和仿真验证的方式跟大家一起进行探讨。在开始仿真之前我们先简单的了解一下什么是串扰以及串扰

2023-01-10 14:13:01

串扰的概念是什么?到底什么是串扰?

2021-03-05 07:54:17

航空通信系统变得日益复杂,我们通常需要在同一架飞机上安装多条天线,这样可能会在天线间造成串扰,或称同址干扰,影响飞机运行。在本教程模型中,我们利用COMSOL Multiphysics 5.1 版本模拟了飞机机身上两个完全相同的天线之间的干扰,其中一个负责发射,另一个负责接收,以此来分析串扰的影响。

2019-08-26 06:36:54

。对于8Gbps及以上的高速应用更应该注意避免此类问题,为高速数字传输链路提供更多裕量。本文针对PCB设计中由小间距QFN封装引入串扰的抑制方法进行了仿真分析,为此类设计提供参考。那么,什么是小间距QFN封装PCB设计串扰抑制呢?

2019-07-30 08:03:48

原创|高速SI培训1.信号串扰的成因串扰(Crosstalk),顾名思义、是指不同信号互连链路之间的相互干扰。对于传输线而言,即能量从一条传输线耦合到另一条传输线上,当不同传输线产生的电磁场发生

2016-10-10 18:00:41

变小,布线密度加大等都使得串扰在高速PCB设计中的影响显著增加。串扰问题是客观存在,但超过一定的界限可能引起电路的误触发,导致系统无法正常工作。设计者必须了解串扰产生的机理,并且在设计中应用恰当的方法

2018-09-11 15:07:52

传输线上出现,它将和任何其它信号一样的传播,最终被传输到传输线末端的接收机上,这种串扰将会影响到接收机所能承受的噪声的裕量。在低端的模拟应用中,小到0.01%的串扰也许是可以接受的,在高速数字应用中,一般

2019-07-08 08:19:27

在嵌入式系统硬件设计中,串扰是硬件工程师必须面对的问题。特别是在高速数字电路中,由于信号沿时间短、布线密度大、信号完整性差,串扰的问题也就更为突出。设计者必须了解串扰产生的原理,并且在设计时应用恰当的方法,使串扰产生的负面影响降到最小。

2019-11-05 08:07:57

。对于8Gbps及以上的高速应用更应该注意避免此类问题,为高速数字传输链路提供更多裕量。本文针对PCB设计中由小间距QFN封装引入串扰的抑制方法进行了仿真分析,为此类设计提供参考。二、问题分析在PCB设计

2018-09-11 11:50:13

本文讨论了串扰的组成,并向读者展示了如何利用泰克的TDS8000B系列采样示波器或CSA8000B系列通信信号分析仪来测量单面PCB板上的串扰。 随着通信、视频、网络和计算机技术领域中数字系统

2018-11-27 10:00:09

矢量网络分析仪串扰如何测试,设备如何设置

2023-04-09 17:13:25

在PCB电路设计中有很多知识技巧,之前我们讲过高速PCB如何布局,以及电路板设计最常用的软件等问题,本文我们讲一下关于怎么解决PCB设计中消除串扰的问题,快跟随小编一起赶紧学习下。 串扰是指在一根

2020-11-02 09:19:31

高频数字信号串扰的产生及变化趋势串扰导致的影响是什么怎么解决高速高密度电路设计中的串扰问题?

2021-04-27 06:13:27

,还是过孔。。。

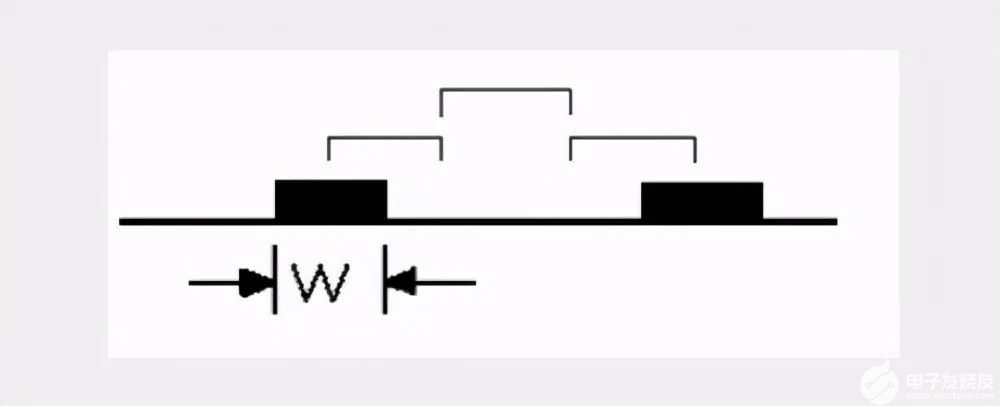

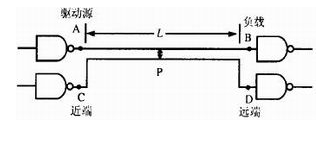

别急嘛,虽然也还是过孔,但是角度是不同的嘛。今天我们来讲讲两对高速过孔之间的串扰怎么通过合理的规划隔离地过孔放的位置来减少。说白了,我们这篇文章想研究的是两对高速信号的过孔位置定了

2025-11-14 14:05:21

高速PCB设计中的串扰分析与控制:物理分析与验证对于确保复杂、高速PCB板级和系统级设计的成功起到越来越关键的作用。本文将介绍在信号完整性分析中抑制和改善信号串扰的

2009-06-14 10:02:38 0

0 高速电路信号完整性分析与设计—串扰串扰是由电磁耦合引起的,布线距离过近,导致彼此的电磁场相互影响串扰只发生在电磁场变换的情况下(信号的上升沿与下降沿)

2009-10-06 11:10:15 0

0 高速PCB 串扰分析及其最小化乔 洪(西南交通大学 电气工程学院 四川 成都 610031)摘要:技术进步带来设计的挑战,在高速、高密度PCB 设计中,串扰问题日益突出。本文就串

2009-12-14 10:55:22 0

0 用于PCB 品质验证的时域串扰测量法作者:Tuomo Heikkil关键词:TDS8000B,串扰,采样示波器,PCB,通信信号分析仪摘要:本文讨论了串扰的组成,并展示了如何利用泰克的TDS8000

2010-02-07 16:40:00 37

37 高速PCB串扰分析及其最小化

1.引言 随着电子产品功能的日益复杂和性能的提高,印刷电路

2009-03-20 13:55:35 888

888

分析了在超深亚微米阶段,串扰对高性能芯片设计的影响,介绍了消除串扰影响的方法。 关键词:串扰,布线,关键路径,

2009-05-05 20:59:16 1434

1434

用于PCB品质验证的时域串扰测量法分析

本文讨论了串扰的组成,并向读者展示了如何利用泰克的TDS8000B系列采样示波器或CSA8000

2009-11-16 16:51:41 932

932 高速PCB串扰分析及其最小化

1.引言

随着电子产品功能的日益复杂和性能的提高,印刷电路板的密度和其相关器件的频率都不断攀升,保持并提高系统的速

2010-03-08 10:50:17 1163

1163

串扰是 高速电路板 设计中干扰信号完整性的主要噪声之一;为有效地抑制串扰噪声,保证系统设计的功能正确,有必要分析串扰问题。针对实际PCB中互连线拓扑和串扰的特点,构

2011-06-22 15:58:54 0

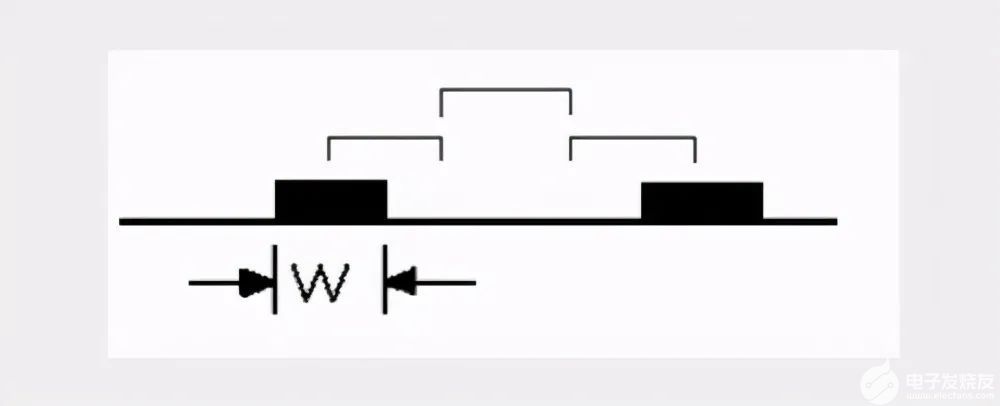

0 对高速PCB中的微带线在多种不同情况下进行了有损传输的串扰仿真和分析, 通过有、无端接时改变线间距、线长和线宽等参数的仿真波形中近端串扰和远端串扰波形的直观变化和对比,

2011-11-21 16:53:02 0

0 通过端接电路在抑制攻击线上反射的同时,减小了受害线上信号的串扰,从而使信号在两条耦合线上的传输质量得到改善。最后进行了多组数据的串扰比较研究,分析了串扰减小的原因。

2011-12-12 14:31:21 28

28 串扰是不同传输线之间的能量耦合。当不同结构的电磁场相互作用时,就会发生串扰。在数字设计中,串扰现象是非常普遍的。串扰可能出现在芯片、PCB板、连接器、芯片封装和连接器

2012-05-28 09:09:38 2951

2951 PCB印制线间串扰的MATLAB分析理论分析给实际布线做参考依据

2015-12-08 10:05:46 0

0 使用实时示波器进行串扰分析

2017-09-07 17:24:58 13

13 力科的信号完整性网络分析仪SPARQ可快速定位连接器,背板和电缆的串扰,可使用单端或差分端口分配来测量近端串扰(NEXT,next-end crosstalk)或远端串扰(FEXT, far-end

2017-12-07 06:34:01 1792

1792 本文对高速差分过孔之间的产生串扰的情况提供了实例仿真分析和解决方法。 高速差分过孔间的串扰 对于板厚较厚的PCB来说,板厚有可能达到2.4mm或者3mm。以3mm的单板为例,此时一个通孔在PCB上Z方向的长度可以达到将近118mil。

2018-03-20 14:44:00 1793

1793

信号频率变高,边沿变陡,印刷电路板的尺寸变小,布线密度加大等都使得串扰在高速PCB设计中的影响显著增加。串扰问题是客观存在,但超过一定的界限可能引起电路的误触发,导致系统无法正常工作。设计者必须了解串扰产生的机理,并且在设计中应用恰当的方法,使串扰产生的负面影响最小化。

2019-05-29 14:09:48 1271

1271

PCB布局上的串扰可能是灾难性的。如果不纠正,串扰可能会导致您的成品板完全无法工作,或者可能会受到间歇性问题的困扰。让我们来看看串扰是什么以及如何减少PCB设计中的串扰。

2019-07-25 11:23:58 3989

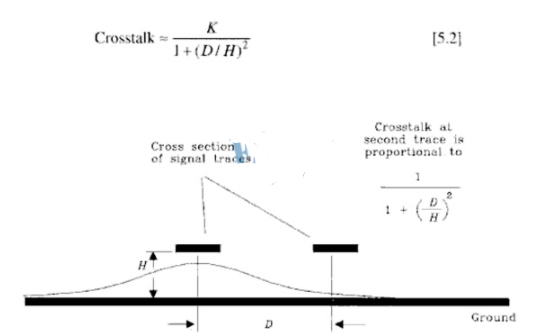

3989 在实际的设计中,板层特性(如厚度,介质常数等)以及线长、线宽、线距、信号的上升时间等都会对串扰有所影响。

2019-08-14 09:13:41 6832

6832

串扰在电子产品的设计中普遍存在,通过以上的分析与仿真,了解了串扰的特性,总结出以下减少串扰的方法:

2019-08-14 11:50:55 20421

20421 串扰是信号完整性中最基本的现象之一,在板上走线密度很高时串扰的影响尤其严重。我们知道,线性无缘系统满足叠加定理,如果受害线上有信号的传输,串扰引起的噪声会叠加在受害线上的信号,从而使其信号产生畸变。

2019-09-18 15:10:37 15882

15882

耦合电感电容产生的前向串扰和反向串扰同时存在,并且大小几乎相等,这样,在受害网络上的前向串扰信号由于极性相反,相互抵消,反向串扰极性相同,叠加增强。串扰分析的模式通常包括默认模式,三态模式和最坏情况模式分析。

2019-09-19 14:39:54 1448

1448 串扰在电路板设计中无可避免,如何减少串扰就变得尤其重要。在前面的一些文章中给大家介绍了很多减少串扰和仿真串扰的方法。

2020-03-07 13:30:00 4390

4390 串扰是指当信号在传输线上传播时,相邻信号之间由于电磁场的相互耦合而产生的不期望的噪声电压信号,即能量由一条线耦合到另一条线上。

2020-04-02 15:30:52 2622

2622

串扰是信号完整性中最基本的现象之一,在板上走线密度很高时串扰的影响尤其严重。我们知道,线性无缘系统满足叠加定理,如果受害线上有信号的传输,串扰引起的噪声会叠加在受害线上的信号,从而使其信号产生畸变。

2020-11-12 10:39:00 2

2 8Gbps及以上的高速应用更应该注意避免此类问题,为高速数字传输链路提供更多裕量。本文针对PCB设计中由小间距QFN封装引入串扰的抑制方法进行了仿真分析,为此类设计提供参考。

2020-10-19 10:42:00 0

0 传输线上出现,它将和任何其它信号一样的传播,最终被传输到传输线末端的接收机上,这种串扰将会影响到接收机所能承受的噪声的裕量。在低端的模拟应用中,小到0.01%的串扰也许是可以接受的,在高速数字应用中,一般能接受高达

2020-10-10 10:43:00 0

0 高速PCB设计中,信号之间由于电磁场的相互耦合而产生的不期望的噪声电压信号称为信号串扰。串扰超出一定的值将可能引发电路误动作从而导致系统无法正常工作,解决PCB串扰问题可以从以下几个方面考虑。

2020-07-19 09:52:05 2820

2820 串扰是高速 PCB 设计人员存在的基础之一。市场需要越来越小和更快的电路板,但是两条平行走线或导体放置在一起的距离越近,一条走线上产生的电磁场干扰另一条走线的机会就越大。 在本文中,我们将介绍串扰

2020-09-16 22:59:02 3130

3130 用于网络的RF板、高速处理器的板以及许多其他系统对串扰强度有严格的要求。信号标准中并不总是规定最大串扰强度,而且在设计中串扰最强烈的地方也不总是很明显。尽管您可能会尝试对设计进行正确的布局规划,但

2021-01-13 13:25:55 3420

3420 来源:电源网 力科的信号完整性网络分析仪SPARQ可快速定位连接器,背板和电缆的串扰,可使用单端或差分端口分配来测量近端串扰(NEXT,next-end crosstalk)或远端串扰(FEXT

2020-10-12 01:59:22 2613

2613 1、 层叠设计与同层串扰 很多时候,串扰超标的根源就来自于层叠设计。也就是我们第一篇文章说的设计上先天不足,后面纠正起来会比较困难。 讲到层叠对串扰的影响,这里有另一张图片,和上文提到的参考平面

2021-04-09 17:21:57 5483

5483

文章——串扰溯源。 提到串扰,防不胜防,令人烦恼。不考虑串扰,仿真波形似乎一切正常,考虑了串扰,信号质量可能就让人不忍直视了,于是就出现了开头那惊悚的一幕。下面就来说说串扰是怎么产生的。 所谓串扰,是指有害信号从一

2021-03-29 10:26:08 4155

4155 串扰是两条信号线之间的耦合、信号线之间的互感和互容引起线上的噪声。容性耦合引发耦合电流,而感性耦合引发耦合电压。PCB板层的参数、信号线间距、驱动端和接收端的电气特性及线端接方式对串扰都有一定的影响。

2021-01-23 08:19:24 16

16 电子发烧友网为你提供实例分析:高速差分过孔之间的串扰资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-04 08:55:27 11

11 高速电路信号完整性分析与设计—串扰

2022-02-10 17:23:04 0

0 串扰是两条信号线之间的耦合、信号线之间的互感和互容引起线上的噪声。容性耦合引发耦合电流,而感性耦合引发耦合电压。PCB板层的参数、信号线间距、驱动端和接收端的电气特性及线端接方式对串扰都有一定的影响。

2022-08-15 09:32:06 11704

11704 在高速链路设计或者射频链路设计中,串扰是一个非常重要的分析参数。如何测量、如何分析。一般遵循着一些设计经验或者规则可以减小串扰的影响,但是很多时候却难以按照规则设计,这就会带来串扰影响的风险。

2022-08-24 09:32:27 3527

3527 串扰是两条信号线之间的耦合、信号线之间的互感和互容引起线上的噪声。容性耦合引发耦合电流,而感性耦合引发耦合电压。PCB板层的参数、信号线间距、驱动端和接收端的电气特性及线端接方式对串扰都有一定的影响。串扰也可以理解为感应噪声。

2022-09-14 09:49:55 3781

3781

小间距QFN封装PCB设计串扰抑制分析

2022-11-04 09:51:54 2

2 在硬件系统设计中,通常我们关注的串扰主要发生在连接器、芯片封装和间距比较近的平行走线之间。但在某些设计中,高速差分过孔之间也会产生较大的串扰,本文对高速差分过孔之间的产生串扰的情况提供了实例仿真分析和解决方法。

2022-11-07 11:20:35 2558

2558 假设差分端口D1—D4是芯片的接收端,我们通过观察D5、D7、D8端口对D2端口的远端串扰来分析相邻通道的串扰情况。

2022-11-11 12:28:19 1477

1477 串扰是 PCB 的走线之间产生的不需要的噪声 (电磁耦合)。

2023-05-22 09:54:24 5605

5605

串扰是一种信号干扰现象,表现为一根信号线上有信号通过时,由于两个相邻导体之间所形成的互感和互容,导致在印制电路板上与之相邻线的信号线就会感应相关的信号,称之为串扰。

2023-07-03 15:45:10 5328

5328

串扰 :即两条信号线之间的耦合引起的线上噪声干扰。

2023-07-06 09:15:48 2670

2670

当信号通过电缆发送时,它们面临两个主要的通信影响因素:EMI和串扰。EMI和串扰严重影响信噪比。通过容易产生EMI 和串扰的电缆发送关键数据是有风险的。下面,让我们来看看这两个问题。

2023-07-06 10:07:03 3408

3408 串扰是指一个信号在传输通道上传输时,因电磁耦合而对相邻的传输线产生不期望的影响,在被干扰信号表现为被注入了一定的耦合电压和耦合电流。过大的串扰可能引起电路的误触发,导致系统无法正常工作。

2023-08-01 14:30:52 1591

1591

pcb上的高速信号需要仿真串扰吗 在数字电子产品中,高速信号被广泛应用于芯片内部和芯片间的数据传输。这些信号通常具有高带宽,并且需要在特定的时间内准确地传输数据。然而,在高速信号传输的过程中,会出

2023-09-05 15:42:31 1458

1458 AllegroSI分析串扰

2022-12-30 09:19:29 0

0 双绞线的串扰就是其中一个线对被相邻的线对的信号串进来所干扰就是串扰。串扰本身是消除不了的,但只要控制在标准所要求以内就不会对网络传输产生大的影响。

2023-11-01 10:10:37 2314

2314

电子发烧友App

电子发烧友App

评论