串扰是高速PCB设计人员存在的基础之一。市场需要越来越小和更快的电路板,但是两条平行走线或导体放置在一起的距离越近,一条走线上产生的电磁场干扰另一条走线的机会就越大。

在本文中,我们将介绍串扰是什么,以及如何在高速设计中分析,模拟和消除串扰。

什么是串扰?

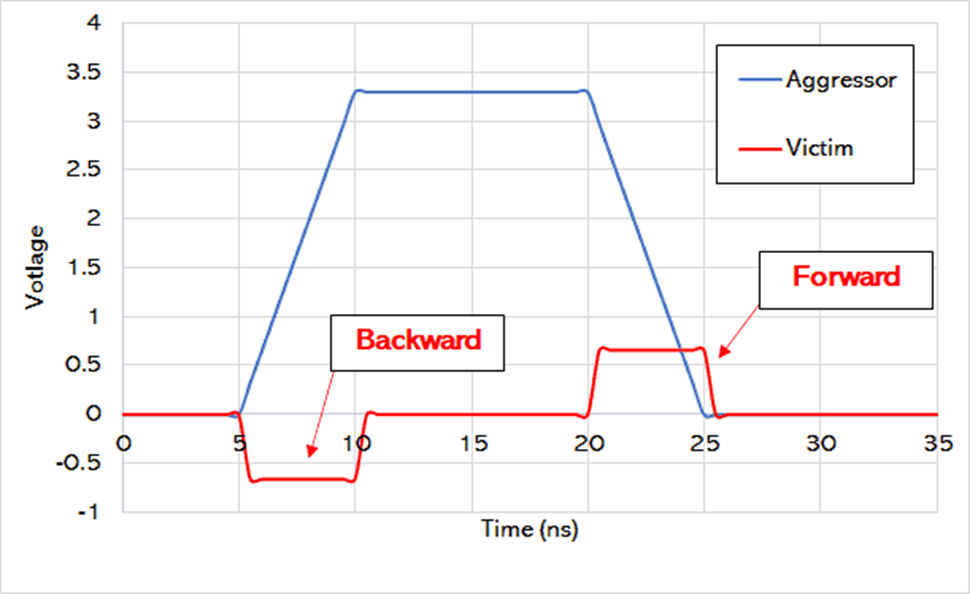

串扰是由走线之间有害的电磁耦合引起的干扰。具有移动电荷的导体将始终产生一些电磁场。增大信号速度会增加其在相邻信号上引起耦合的可能性。让我们仔细看看电磁耦合的两个组成部分。

电感/磁耦合

当电流流过诸如PCB走线之类的导体时,会产生磁场。当该场通过相邻导体时,它会通过法拉第第二感应定律感应出电动势或电压。这被称为磁耦合或电感耦合,如果感应电压足以破坏经历电感耦合的走线信号,则可能会出现问题。

电容/电耦合

除磁场外,流经PCB走线的电流还会产生相应的电场。当来自一条迹线的电场与相邻的平行迹线接触时,会产生一个电容器。当两条线路电容耦合时,一条线路上的信号有可能在另一条线路上引起串扰,从而导致噪声和信号完整性下降。这种现象也称为寄生电容。

避免串扰的PCB最佳实践

因此,既然您对串扰背后的物理原理有所了解,那么如何在PCB设计中防止串扰呢?消除串扰的关键是,尽管串扰无处不在,但它是并行信号线之间的最大串扰。

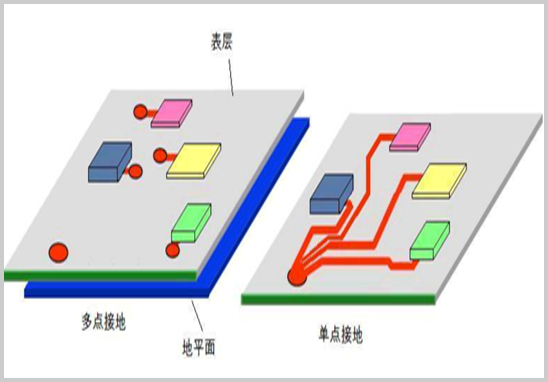

消除串扰的最好方法是通过将返回路径与地面紧密耦合到高速信号来利用导致其产生的并行性。由于返回路径的大小相等但方向相反,因此磁场相互抵消并减少了串扰。

确保信号完整性的另一种方法是使用差分信号,其中两条大小相等但极性相反的电压线用于创建单个高速数据信号。由于实际数据信号被视为接收器上两条电压线之间的电压差,并且由于电磁噪声趋于同等地影响两条线,因此即使在存在外部噪声的情况下,信号本身仍然可以感知。

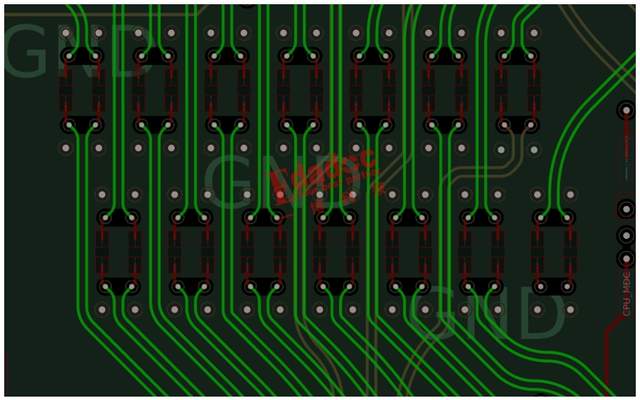

以下是用于减少串扰的PCB布线技巧的快速摘要:

l减少允许两条线并行运行的长度。

l确保尽可能有可靠的返回路径。

l在适当的地方使用差分信令。

l使用带有过孔接地的保护线。

l尽可能将高速信号(尤其是时钟信号)与其他走线隔离。

l使相邻层中的迹线彼此垂直。

使用EDA软件执行串扰分析

即使您了解了高速PCB设计中可能导致串扰的情况,也可能很难跟踪所有可能导致电容性和电感性耦合的变量。值得庆幸的是,EDA工具已经发展为使高速PCB的设计更易于管理。

-

PCB设计

+关注

关注

396文章

4939浏览量

95816 -

PCB布线

+关注

关注

22文章

473浏览量

43656 -

线路板设计

+关注

关注

0文章

61浏览量

8487 -

华秋DFM

+关注

关注

20文章

3516浏览量

6544

发布评论请先 登录

在高速PCB设计中消除串扰的方法与讨论

在高速PCB设计中消除串扰的方法与讨论

评论