在硬件系统设计中,通常我们关注的串扰主要发生在连接器、芯片封装和间距比较近的平行走线之间。但在某些设计中,高速差分过孔之间也会产生较大的串扰,本文对高速差分过孔之间的产生串扰的情况提供了实例仿真分析和解决方法。

2015-12-18 10:45:12 4534

4534 损耗如何造成上升边退化?分析介质损耗与耗散因子的特点,损耗 . 如何吃掉高频分量?如何影响数据完整性?如何用眼图分析符号间干扰及抖动?第七讲 PCB 多网络串扰分析与设计 基于互容、互感的传输线串扰分析

2010-12-16 10:03:11

,由于干扰源的不确定性,串扰噪声一般会同时影响信号的边沿和幅度。因此,对于串扰来说两个方面的影响都应该考虑。串扰形成的根源在于耦合。在多导体系统中,导体间通过电场和磁场发生耦合。这种耦合会把信号的一部分能量传递到邻近的导体上,从而形成噪声。耦合的方式主要有两种:1、容性耦合。2、感性耦合。

2019-05-31 06:03:14

继上一篇“差模(常模)噪声与共模噪声”之后,本文将对“串扰”进行介绍。串扰串扰是由于线路之间的耦合引发的信号和噪声等的传播,也称为“串音干扰”。特别是“串音”在模拟通讯时代是字如其意、一目了然的表达

2018-11-29 14:29:12

串扰的基本原理

2021-03-18 06:26:37

所谓串扰,是指有害信号从一个传输线耦合到毗邻传输线的现象,噪声源(攻击信号)所在的信号网络称为动态线,***扰的信号网络称为静态线。串扰产生的过程,从电路的角度分析,是由相邻传输线之间的电场(容性)耦合和磁场(感性)耦合引起,需要注意的是串扰不仅仅存在于信号路径,还与返回路径密切相关。

2019-08-02 08:28:35

在选择模数转换器时,是否应该考虑串扰问题?ADI高级系统应用工程师Rob Reeder:“当然,这是必须考虑的”。串扰可能来自几种途径从印刷电路板(PCB)的一条信号链到另一条信号链,从IC中的一个

2019-02-28 13:32:18

ad 21 我有百多对差分线过孔 我改了过孔间距规则 需要重新调整差分对过孔 但是太多了 调整太慢了 有没有简单的方式一次调很多个

2022-05-18 20:06:54

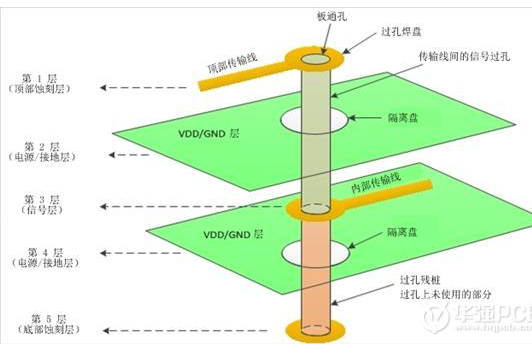

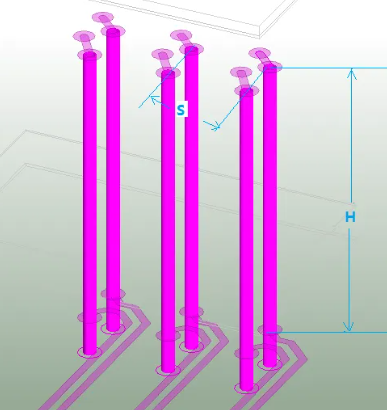

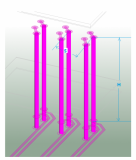

间的距离被称为过孔间距。过孔间距越小,互耦合电容越多。图2:使用背面钻孔的GSSG差分过孔不要忘记,在传输速率超过10Gbps时,过孔残桩会严重影响高速信号完整性。幸运的是,有一种背面钻孔PCB制造

2018-09-11 11:22:04

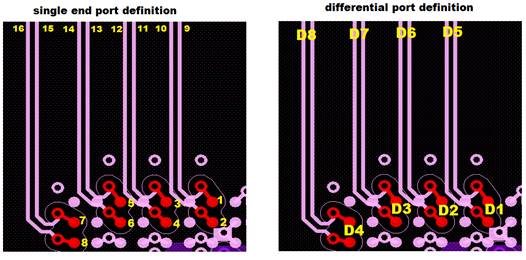

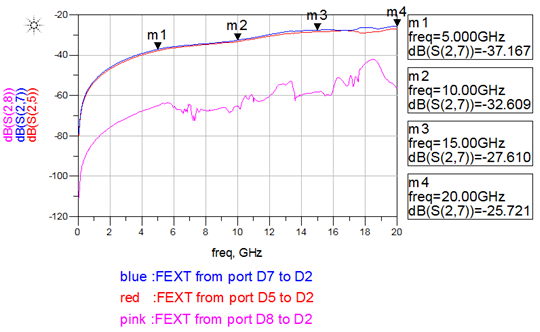

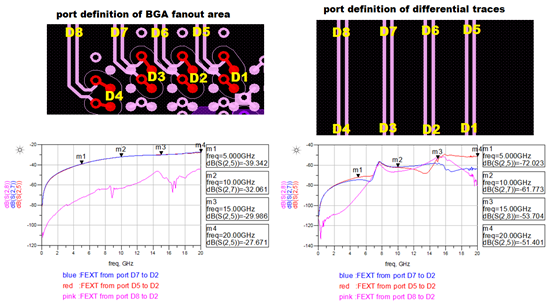

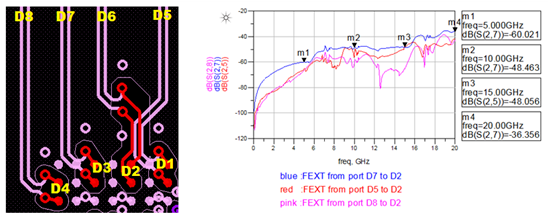

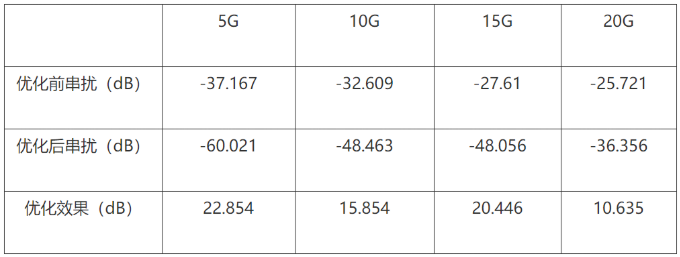

走线这样Stub会比较短。或者可以采用背钻的方式。图1:高速差分过孔产生串扰的情况(H>100mil, S=31.5mil ) 差分过孔间串扰的仿真分析下面是对一个板厚为3mm,0.8mm

2018-09-04 14:48:28

可以采用背钻的方式。图1:高速差分过孔产生串扰的情况(H》100mil, S=31.5mil )差分过孔间串扰的仿真分析下面是对一个板厚为3mm,0.8mm BGA扇出过孔pitch为31.5mil

2020-08-04 10:16:49

做深入的研究,发现这的确是一个苦差事。刚好今年的文章中就有一篇讲得比较透彻的仿真测试拟合的案例,下面我们一起来看看。题目有点长,但是也很容易理解,讲的就是对差分过孔的分析,分析的方法就是通过仿真和测试

2020-04-16 17:10:26

最新的高速电路设计与信号完整性分析技术要点;深入讲解信号完整性的四类问题:反射(reflection);串扰(crosstalk);电源轨道塌陷(rail collapse);电磁干扰(EMI)。介绍的分析

2010-11-09 14:21:09

高速PCB串扰分析及其最小化 1.引言 &

2009-03-20 13:56:06

中传输时,在返回路径中对付串扰和突变的鲁棒性更好; · 因为每个信号都有自己的返回路径,所以差分新信号通过接插件或封装时,不易受 到开关噪声的干扰; 但是差分信号也有其缺点:首先是会产生潜在

2018-11-27 10:56:15

的串扰进行仿真,可以在PCB实现中迅速地发现、定位和解决串扰问题。本文以Mentor公司的仿真软件HyperLynx为例对串扰进行分析。

高速设计中的仿真包括布线前的原理图仿真和布线后

2018-08-28 11:58:32

和远端串扰这种方法来研究多线间串扰问题。利用Hyperlynx,主要分析串扰对高速信号传输模型的侵害作用并根据仿真结果,获得了最佳的解决办法,优化设计目标。【关键词】:信号完整性;;反射;;串扰;;近

2010-05-13 09:10:07

串扰问题产生的机理是什么高速数字系统的串扰问题怎么解决?

2021-04-25 08:56:13

高速电路信号完整性分析与设计—串扰串扰是由电磁耦合引起的,布线距离过近,导致彼此的电磁场相互影响串扰只发生在电磁场变换的情况下(信号的上升沿与下降沿)[此贴子已经被作者于2009-9-12 10:32:03编辑过]

2009-09-12 10:31:08

高速PCB设计中的信号完整性概念以及破坏信号完整性的原因高速电路设计中反射和串扰的形成原因

2021-04-27 06:57:21

是ADI的SAR型 18位单通道全差分输入的ADC。ADC的后端是MCU,MCU将数字信号处理之后再画到显示屏上显示实时波形。

调试发现显示的信号有串扰,表现为某一路信号悬空之后,相邻的那一路信号

2023-12-18 08:27:39

是ADI的SAR型 18位单通道全差分输入的ADC。ADC的后端是MCU,MCU将数字信号处理之后再画到显示屏上显示实时波形。 调试发现显示的信号有串扰,表现为某一路信号悬空之后,相邻的那一路信号上

2018-09-06 14:32:00

多少,能不能通过其他指标更清晰的量化出来呢,雷豹心里其实是打鼓的!

Chris看破不点破,决定亲自来接手这个案例后续的串扰分析。我们知道,去衡量任何信号质量的手段无非就两种,要么是在时域上判断,要么就是在

2023-06-06 17:24:55

串扰是由于线路之间的耦合引发的信号和噪声等的传播,也称为“串音干扰”。特别是“串音”在模拟通讯时代是字如其意、一目了然的表达。两根线(也包括PCB的薄膜布线)独立的情况下,相互间应该不会有电气信号

2019-08-08 06:21:47

PCB板上的高速信号需要进行仿真串扰吗?

2023-04-07 17:33:31

尺寸变小,成本要求提高,电路板层数变少,使得布线密度越来越大,串扰的问题也就越发严重。本文从3W规则,串扰理论,仿真验证几个方面对真实世界中的串扰控制进行量化分析。关键词:3W,串扰理论,仿真验证,量化分析

2014-10-21 09:53:31

影响非常大,要特别注意。以上的结论为一个量化估值,具体情况需要具体分析,不同信号对于串扰的敏感程度不一样,实际的上升时间也需要根据模型来定,除了靠经验之外,仿真也能帮助我们更精确的判断串扰。

2014-10-21 09:52:58

初始状态,仿真器计算所有默认侵害网络对每一个受害网络的串扰的总和。这种方式一般只对个别关键网络进行分析,因为要计算的组合太多,仿真速度比较慢。

2009-03-20 14:04:47

将受害网络的驱动器保持初始状态,仿真器计算所有默认侵害网络对每一个受害网络的串扰的总和。 这种方式一般只对个别关键网络进行分析,因为要计算的组合太多,仿真速度比较慢。

2018-08-29 10:28:17

分析是指将受害网络的驱动器保持初始状态,仿真器计算所有默认侵害网络对每一个受害网络的串扰的总和。 这种方式一般只对个别关键网络进行分析,因为要计算的组合太多,仿真速度比较慢。

2020-06-13 11:59:57

了各自的见解,比如串扰,绕线,过孔,跨分割等等。本期我们就以不同模态下的串扰对信号时延的影响继续通过理论分析和仿真验证的方式跟大家一起进行探讨。在开始仿真之前我们先简单的了解一下什么是串扰以及串扰

2023-01-10 14:13:01

,线宽10mil,线距6mil,每两组HDMI差分信号对的间距超过20mil; (4)DDR布线规则。DDR1走线要求信号尽量不走过孔,信号线等宽,线与线等距,走线必须满足2W原则,以减少信号间的串扰

2017-01-20 11:44:22

完整性与电磁兼容性测试。主要特色:●支持各种传输线的阻抗规划和计算●支持反射 / 串扰 / 损耗 / 过孔效应及 EMC 分析●通过匹配向导为高速网络提供串行、并行及差分匹配方案●支持多板分析,可对板间

2018-02-13 13:57:12

噪声一般会同时影响信号的边沿和幅度。因此,对于串扰来说两个方面的影响都应该考虑。串扰形成的根源在于耦合。在多导体系统中,导体间通过电场和磁场发生耦合。这种耦合会把信号的一部分能量传递到邻近的导体上,从而形成噪声。耦合的方式主要有两种:1、容性耦合。2、感性耦合。

2019-04-18 09:30:40

多了,这样我想有个问题就是,在正常采集时,这几个通道间会不会有互相串扰的问题。谢谢。

另外我想知道互相串扰产生原因,如果能成放大器内部解释更好

2023-11-21 08:15:40

继上一篇“差模(常模)噪声与共模噪声”之后,本文将对“串扰”进行介绍。串扰串扰是由于线路之间的耦合引发的信号和噪声等的传播,也称为“串音干扰”。特别是“串音”在模拟通讯时代是字如其意、一目了然的表达

2019-03-21 06:20:15

串扰的概念是什么?到底什么是串扰?

2021-03-05 07:54:17

什么是串扰?互感和互容电感和电容矩阵串扰引起的噪声

2021-02-05 07:18:27

航空通信系统变得日益复杂,我们通常需要在同一架飞机上安装多条天线,这样可能会在天线间造成串扰,或称同址干扰,影响飞机运行。在本教程模型中,我们利用COMSOL Multiphysics 5.1 版本模拟了飞机机身上两个完全相同的天线之间的干扰,其中一个负责发射,另一个负责接收,以此来分析串扰的影响。

2019-08-26 06:36:54

。对于8Gbps及以上的高速应用更应该注意避免此类问题,为高速数字传输链路提供更多裕量。本文针对PCB设计中由小间距QFN封装引入串扰的抑制方法进行了仿真分析,为此类设计提供参考。那么,什么是小间距QFN封装PCB设计串扰抑制呢?

2019-07-30 08:03:48

数百毫伏的差分幅度。入侵(aggressor)信号与受害(victim)信号出现能量耦合时会产生串扰,表现为电场或磁场干扰。电场通过信号间的互电容耦合,磁场则通过互感耦合。方程式(1)和(2)分别是入侵信号

2019-05-28 08:00:02

我用AD9910做了块板子,使用AD9910内部的PLL,参考时钟为10MHz,64倍频,输出80MHz,发现在70MHz和90MHz处有串扰信号,幅值与80MHz差65dB。怀疑是AD9910

2018-11-19 09:46:32

领域的工程师离不开它,近些年来,高速信号完整性领域也越来越多的工程师喜欢上了这款“不要不要”的软件。鉴于国内外的很多ADS的资料都是微波射频领域的,接下来,我们会慢慢的分享一些ADS在信号完整性领域经常使用的小功能和技巧。今天给大家介绍使用ADS进行串扰的仿真。

2019-06-28 08:09:46

间耦合以及绕线方式等有关。随着PCB走线信号速率越来越高,对时序要求较高的源同步信号的时序裕量越来越少,因此在PCB设计阶段准确知道PCB走线对信号时延的影响变的尤为重要。本文基于仿真分析DK,串扰,过孔

2015-01-05 11:02:57

串扰信号产生的机理是什么串扰的几个重要特性分析线间距P与两线平行长度L对串扰大小的影响如何将串扰控制在可以容忍的范围

2021-04-27 06:07:54

和上面仿真波形的50ps来比,真的是很微不足道。实际上串扰在DDR模块里的确会有更为严重的影响,试想一下,我们在高速串行信号里面5mV的串扰都觉得非常大了,在DDR模块里居然能有上百mV。当然两者还是有

2019-09-05 11:01:14

面对串扰,包地是万能的吗?请看不一样的解答

2016-12-30 16:29:07

,同样对传输线2有 。 图1 双传输线系统中电容示意图在实际的电路PCB中,往往N多条传输线共存,如果要考虑所有传输线间的串扰情况,那将是非常复杂的N阶矩阵。信号间串扰信号的仿真分析一般通过电磁场仿真

2016-10-10 18:00:41

> 2S 以最小化串扰;2.在信号离开器件后,尽可能的靠近两条差分信号对,最小化信号反射;3.在两条差分信号对的整个走线过程中保持恒定的距离;4.保持两条差分信号对的走线长度一致,最小化偏斜

2018-09-21 10:28:30

条线上。 如图1所示,为便于分析,我们依照离散式等效模型来描述两个相邻传输线的串扰模型,传输线AB和CD的特性阻抗为Z0,且终端匹配电阻R=Z0。如果位于A 点的驱动源为干扰源,则A—B间的线网称为干扰源

2018-09-11 15:07:52

传输线上出现,它将和任何其它信号一样的传播,最终被传输到传输线末端的接收机上,这种串扰将会影响到接收机所能承受的噪声的裕量。在低端的模拟应用中,小到0.01%的串扰也许是可以接受的,在高速数字应用中,一般

2019-07-08 08:19:27

时,字线放电。通过后仿真,我们看到在读操作时,防串扰结构布局的存储器平均输出时间比一般结构的存储器输出时间短,可见在速度上,防串扰结构布局的存储器具有一定的优势。在性能方面,该结构减小了SRAM读写

2020-05-20 15:24:34

怎么区别过孔开窗和过孔盖油?

2021-02-03 07:39:09

在嵌入式系统硬件设计中,串扰是硬件工程师必须面对的问题。特别是在高速数字电路中,由于信号沿时间短、布线密度大、信号完整性差,串扰的问题也就更为突出。设计者必须了解串扰产生的原理,并且在设计时应用恰当的方法,使串扰产生的负面影响降到最小。

2019-11-05 08:07:57

。对于8Gbps及以上的高速应用更应该注意避免此类问题,为高速数字传输链路提供更多裕量。本文针对PCB设计中由小间距QFN封装引入串扰的抑制方法进行了仿真分析,为此类设计提供参考。二、问题分析在PCB设计

2018-09-11 11:50:13

8Gbps及以上的高速应用更应该注意避免此类问题,为高速数字传输链路提供更多裕量。本文针对PCB设计中由小间距QFN封装引入串扰的抑制方法进行了仿真分析,为此类设计提供参考。

2021-03-01 11:45:56

这些变量的影响量化出来,从而根据这些变量计算出一个过孔的阻抗。感觉在缺少仿真的情况下也能大概得到过孔的阻抗了!的确,有一些软件能大概量化出单个过孔的阻抗。但是如果是下面的差分过孔呢?除了单端过孔

2021-11-18 17:04:51

矢量网络分析仪串扰如何测试,设备如何设置

2023-04-09 17:13:25

示波器通道间串扰的影响 目前几乎所有通用品牌的主流示波器通道都不是隔离的,那么在进行多通道测试的时候,通道与通道之间会一定程度互相干扰,因此通道隔离度指标非常重要,隔离度越高的示波器测量就越精确

2020-03-23 18:53:35

串扰分析)进行故障定位,HDTDX可以准确的告诉你在多少米处NEXT存在问题。PS NEXT(综合近端串绕)是一对线感应到的所有其它绕对的近端串扰的总和,它是一个计算值;通常适用于2对或2对以上的线

2018-01-19 11:15:04

在PCB电路设计中有很多知识技巧,之前我们讲过高速PCB如何布局,以及电路板设计最常用的软件等问题,本文我们讲一下关于怎么解决PCB设计中消除串扰的问题,快跟随小编一起赶紧学习下。 串扰是指在一根

2020-11-02 09:19:31

是SAR型 18位单通道全差分输入的ADC。ADC的后端是MCU,MCU将数字信号处理之后再画到显示屏上显示实时波形。 调试发现显示的信号有串扰,表现为某一路信号悬空之后,相邻的那一路信号上就会出现噪声。将采样的时间延长也无法消除串扰。想请教一下各路专家,造成串扰的原因和如何消除串扰,谢谢。

2019-05-14 14:17:00

高频数字信号串扰的产生及变化趋势串扰导致的影响是什么怎么解决高速高密度电路设计中的串扰问题?

2021-04-27 06:13:27

高速差分信号传输中也存在着信号完整性问题。差分过孔在频率很高的时候会明显地影响差分信号的完整性, 现介绍差分过孔的等效RLC 模型, 在HFSS 中建立了差分过孔仿真模型并分析了过

2012-01-16 16:31:37 55

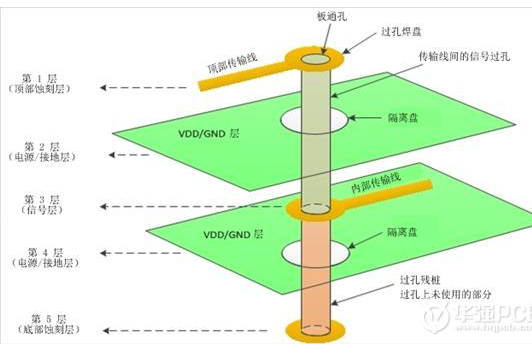

55 在一个高速印刷电路板 (PCB) 中,通孔在降低信号完整性性能方面一直饱受诟病。然而,过孔的使用是不可避免的。在标准的电路板上,元器件被放置在顶层,而差分对的走线在内层。内层的电磁辐射和对与对之间

2017-10-27 17:52:48 4

4 本文对高速差分过孔之间的产生串扰的情况提供了实例仿真分析和解决方法。 高速差分过孔间的串扰 对于板厚较厚的PCB来说,板厚有可能达到2.4mm或者3mm。以3mm的单板为例,此时一个通孔在PCB上Z方向的长度可以达到将近118mil。

2018-03-20 14:44:00 1316

1316

PCB allegro中如何替换部分过孔,或全局的过孔。在PCB allegro设计中,如果一不留意,就把过孔打错了,或打大小,这时,我们要PCB中的某一部过孔进行替换:更多设计内容在小北PCB设计

2018-08-07 00:49:44 1661

1661 PCB allegro中如何替换部分过孔,或全局的过孔。在PCB allegro设计中,如果一不留意,就把过孔打错了,或打大小,这时,我们要PCB中的某一部过孔进行替换:下面为大家介绍下在没有

2018-08-07 00:52:03 888

888 一、via在转换过程中,因设计不标准或是你对转换gerber设置规则不清楚,而导致出问题当你发的是gerber文件那工厂厂家则无法分出那些是过孔那些是插键孔,则唯一能识别的是按文件加工,那有

2019-06-11 14:52:30 1323

1323 过孔是镀在电路板顶层与底层之间的通孔外的金属圆柱体。信号过孔连接不同层上的传输线。过孔残桩是过孔上未使用的部分。过孔焊盘是圆环状垫片,它们将过孔连接至顶部或内部传输线。隔离盘是每个电源或接地层内的环形空隙,以防止到电源和接地层的短路。

2019-05-14 14:46:48 2453

2453

对于板厚较厚的PCB来说,板厚有可能达到2.4mm或者3mm。以3mm的单板为例,此时一个通孔在PCB上Z方向的长度可以达到将近118mil。如果PCB上有0.8mm pitch的BGA的话,BGA器件的扇出过孔间距只有大约31.5mil。

2019-11-21 16:05:48 1722

1722 电子发烧友网为你提供实例分析:高速差分过孔之间的串扰资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-04 08:55:27 11

11 在硬件系统设计中,通常我们关注的串扰主要发生在连接器、芯片封装和间距比较近的平行走线之间。但在某些设计中,高速差分过孔之间也会产生较大的串扰,本文对高速差分过孔之间的产生串扰的情况提供了实例仿真分析和解决方法。

2022-11-07 11:20:35 1018

1018 在高速电路设计中,过孔可以说贯穿着设计的始终。而对于高速PCB设计而言,过孔的设计是非常复杂的,通常需要通过仿真来确定过孔的结构和尺寸。

2023-06-19 10:33:08 570

570

电子发烧友App

电子发烧友App

评论