串扰是一种信号干扰现象,表现为一根信号线上有信号通过时,由于两个相邻导体之间所形成的互感和互容,导致在印制电路板上与之相邻线的信号线就会感应相关的信号,称之为串扰。信号线距离地线越近,线间距越大,产生的串扰信号越小,异步信号与时钟信号更容易产生串扰。

因此,消除串扰的方法是移开发生串扰的信号或屏蔽被严重干扰的信号。随着印制电路板的绕线布局密度增加,尤其是长距离总线的布局使得串扰成为信号完整性中最严重的问题之一。

信号串扰原理

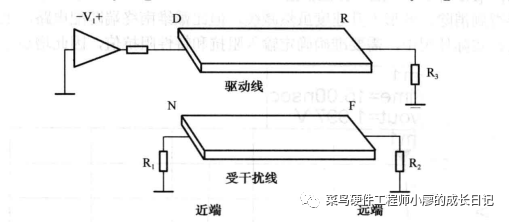

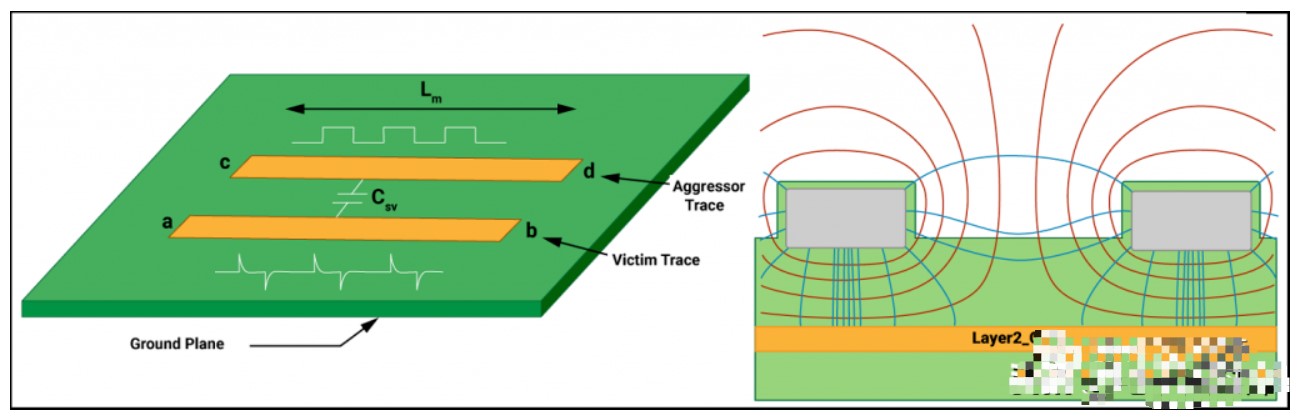

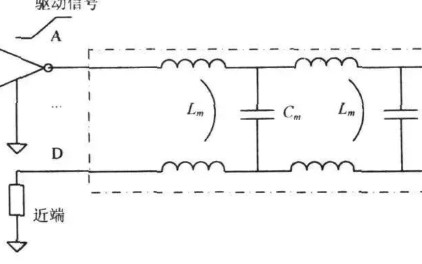

信号串扰根据发生位置可以分为近端信号串扰(Near-end Crosstalk)和远端信号串扰(Far-end Crosstalk)。图12.105所示为两传输线发生信号串扰的示意图及等效电路图,两并行线长度为l,驱动线上传送一个脉冲信号,设在x点经互容Cm及互感Km会在受干扰线上造成不必要的干扰信号。

驱动线在x点通过互容Cm产生一个电流Ic流向受干扰线,此电流将分成大小相等方向相反的电流,分别受干扰线的两个端点流动,而驱动线在x点也通过互感Km感应产生一个电流IL流向干扰线,此电流在受干扰线方向与驱动线电流方向相反,因此在受干扰线将有Ic/2-IL的电流流向远端,同时也将有Ic/2+IL电流流向近端。

信号串扰仿真实例

在射频电路板设计中,信号串扰主要通过包地线、差分走线、避免过长平行走向等措施来改善。在采取合理的措施之前,首先要对信号串扰有一个直观的了解,本节主要通过两类微带线的信号串扰仿真来进行讨论。

1、对称双导体微带线近端和远端的信号串扰仿真、数据观察。

2、非对称三导体微带线近端和远端的信号串扰仿真、数据观察

实验步骤

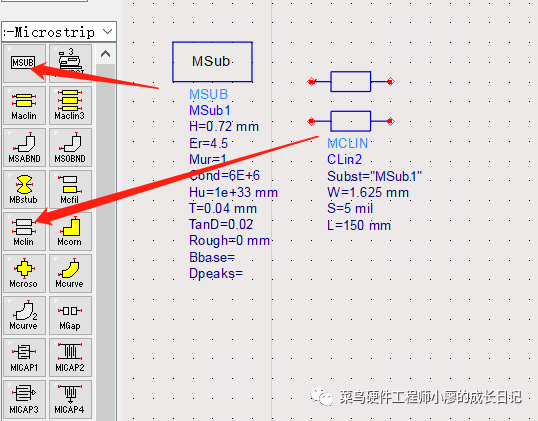

2、添加微带控制其MSUB和MCLIN

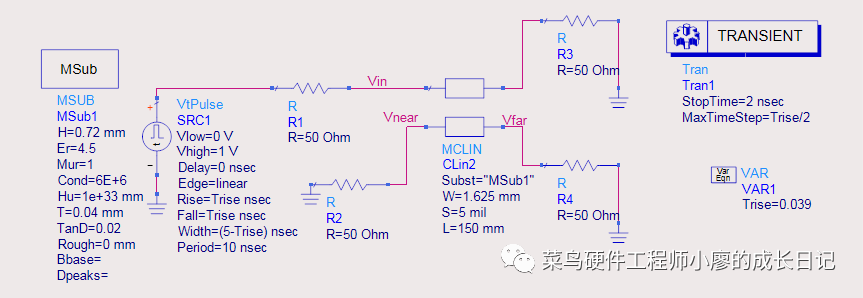

3、完成电路图

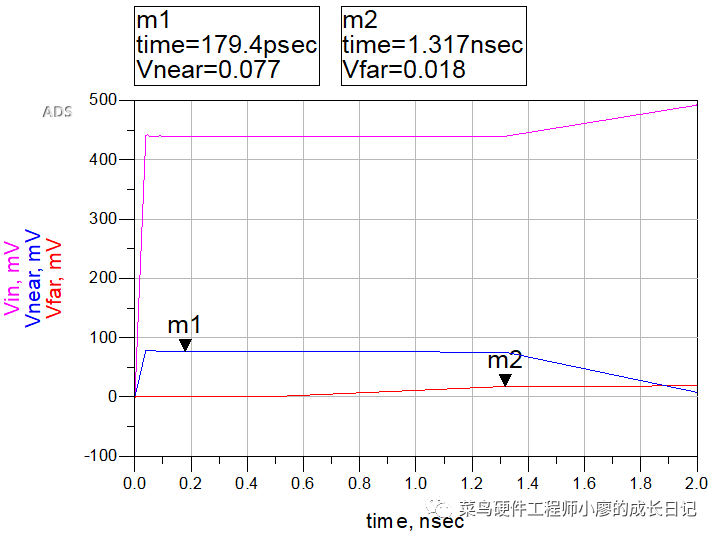

4、仿真结果如下,可见近端最大串扰为0.077V,远端串扰为0.018V。

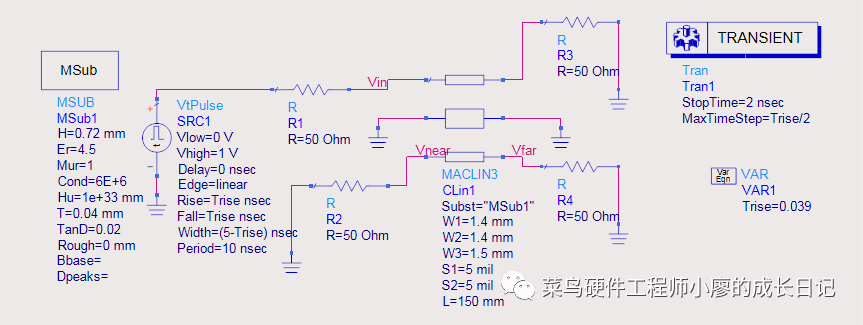

5、完成对微带线串扰仿真后,继续对非对称三导体微带线进行串扰仿真。将MCLIN改为MACLIN3,进行设置:

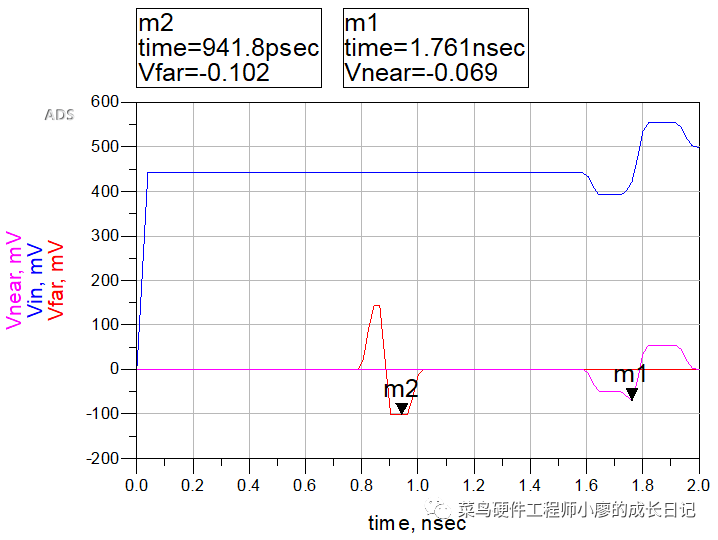

6、仿真结果

与对称微带线相比,非对称三导体微带线在远端的串扰要大许多。因此,在进行射频电路板设计时,要注意采用包地线等措施,以减小远端串扰。

-

ADS仿真

+关注

关注

2文章

71浏览量

11148 -

射频电路板

+关注

关注

2文章

14浏览量

8931 -

信号串扰

+关注

关注

0文章

15浏览量

8828

发布评论请先 登录

信号串扰的原理、实例以及实现步骤

信号串扰的原理、实例以及实现步骤

评论