在实际的设计中,板层特性(如厚度,介质常数等)以及线长、线宽、线距、信号的上升时间等都会对串扰有所影响。

下面结合使用Mentor Graphie公司的信号完整性仿真软件Hyperlynx,对上述的影响串扰的因素进行分析。

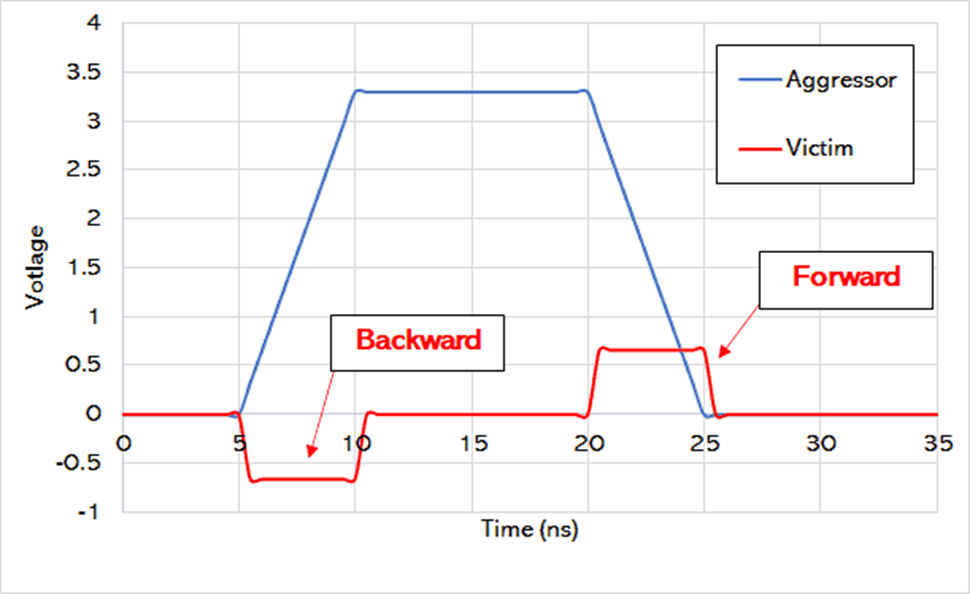

首先在Hyperlynx中建立两线串扰的模型,如图4所示,设两线的线宽为5 mil,线长为6 in,线距为5 mil,两线均为顶层微带线,特性阻抗为49.5Ω,两线都端接50Ω的电阻,以消除反射的影响。

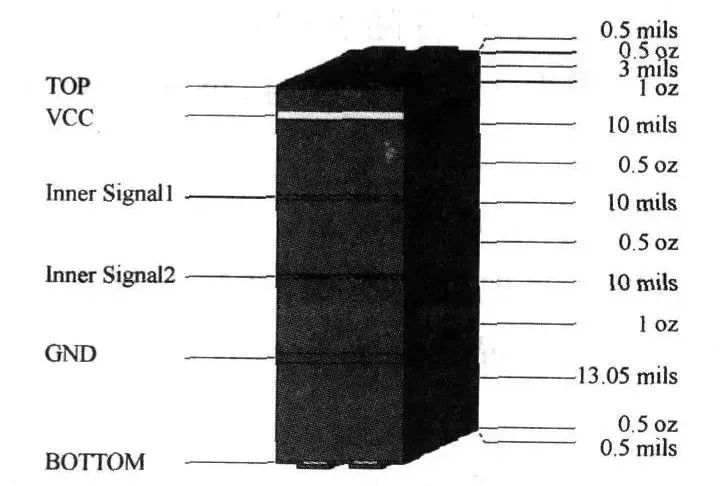

干扰线的驱动器采用CMOS工艺器件的IBIS模型,电压为3.3 V,频率为100 MHz。PCB的介电常数为4.3,六层板,其叠层结构如图5所示。

图4:两线串扰模型

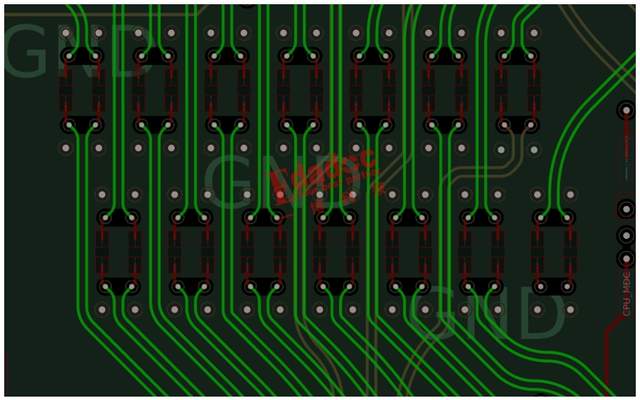

图5:PCB叠层结构

1耦合长度对串扰的影响

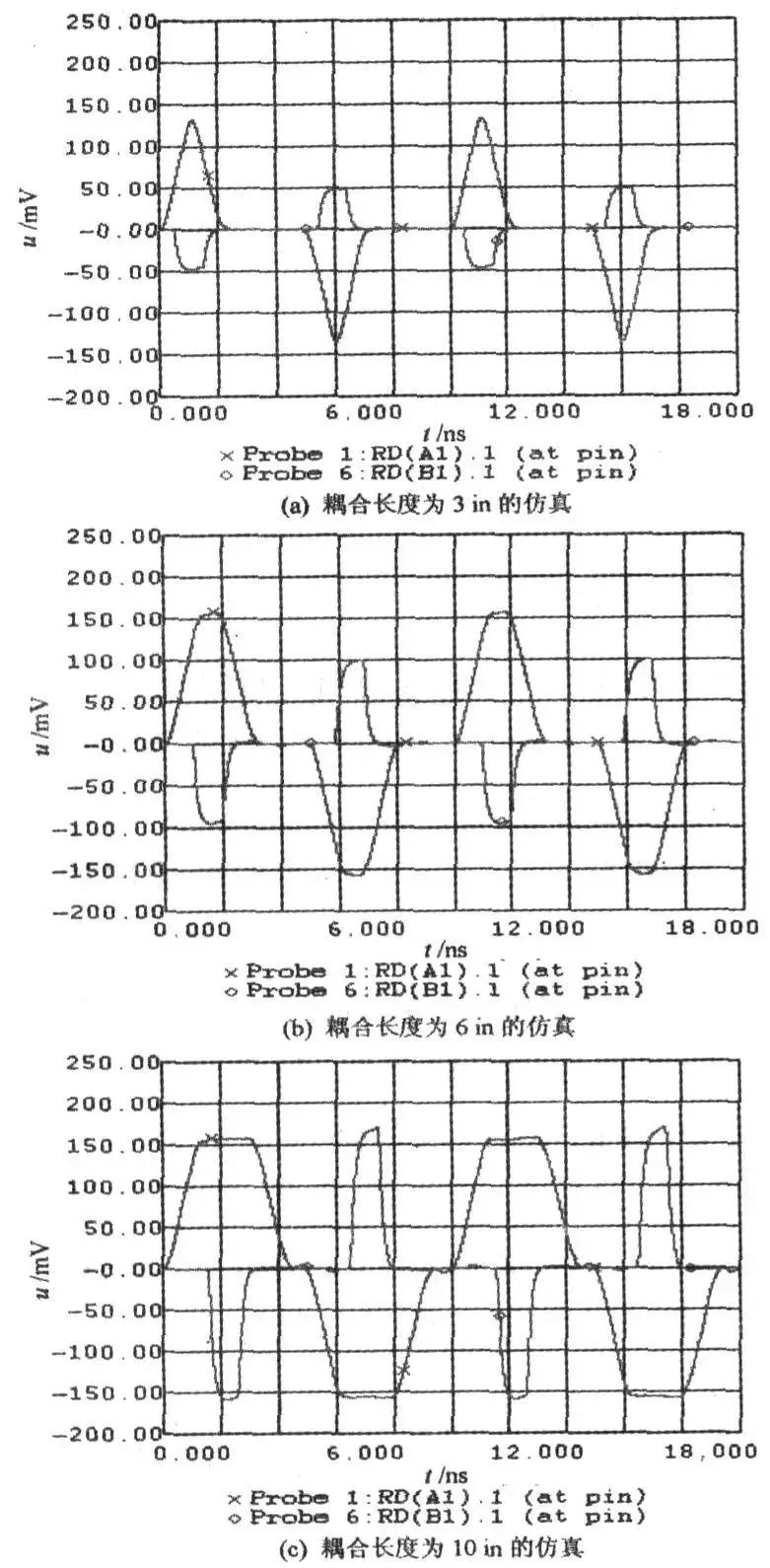

改变两线的耦合长度,分别将耦合长度设置为3 in,6 in,10 in,其他设置不变。

图6(a)是耦合长度为3 in的串扰波形,其中近端串扰峰值为126.34 mV,远端为43.01 mV;图6(b)是耦合长度为6 in的串扰波形,其近端串扰峰值为153.23 mV,远端为99.46 mV;图6(c)是耦合长度为10 in的串扰波形,其近端串扰峰值为153.23 mV,远端为163.98 mV。

由此可见,对于远端串扰峰值与耦合长度成正比,耦合长度越长,串扰越大;而对于近端串扰,当耦合长度小于饱和长度时,串扰将随着耦合长度的增加而增加,但是当耦合长度大于饱和长度时,近端串扰值将为一个稳定值。

图6:不同耦合长度的仿真结果

2线间距对串扰的影响

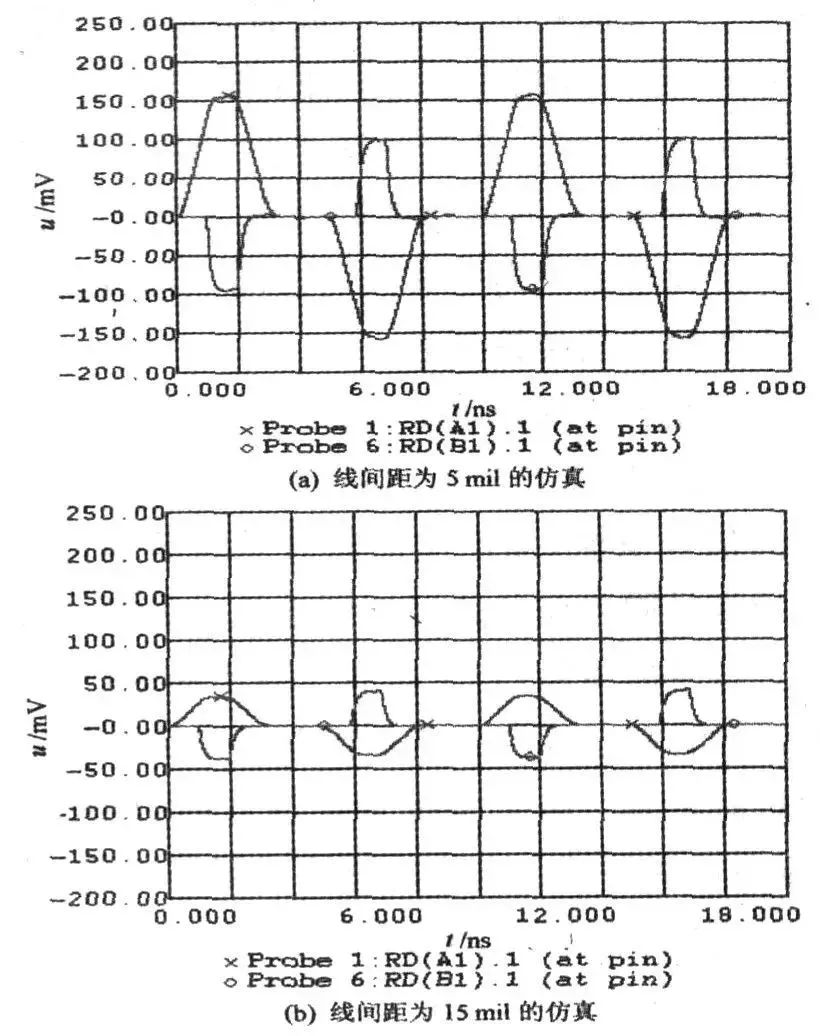

以下是保持其他设置不变,考察线间距的改变对串扰的影响。分别设置线距为5 mil,15 mil,仿真波形如图7所示。

图7:不同线间距的仿真结果

由图7可知,当线间距为5 mil时,近段串扰峰值为153.23 mV,远端为99.46 mV;而线间距为15 mil时,近端串扰峰值为33.40 mV,远端为40.49 mV。

可见随着线间距的增大,无论是近端还是远端串扰都将减小,当线间距大于等于线宽的3倍时,串扰已经很小。

3上升时间对串扰的影响

下面考察上升沿时间的变化对串扰的影响,其他设置保持不变。分别设置驱动器为CMOS 3.3 V MEDI—UM;CMOS 3.3 V FAST;CMOS 3.3 V ULTRA—FAST,仿真波形如图8所示。

图8:不同驱动器设置的仿真结果

图8(a)中的近端串扰峰值为153.9 mV,远端串扰为46.3 mV;图8(b)中近端串扰峰值为153.2 mV,远端串扰为99.5 mV;图8(c)中近段串扰峰值为153.2 mV,远端串扰为349.9 mV。

可见,当上升沿时间缩短时,远端串扰噪声越来越大。

对于近端串扰来说,如果与传输线的时延相比,上升时间较短,则近端串扰与上升时间无关;而如果与传输线时迟相比,上升时间较长,则近端串扰噪声与上升时间有关(随着上升沿时间的减小,近端串扰变大)。

4介质层厚度对串扰的影响

在PCB的叠层编辑器中将介质层厚度分别设置为3 mil和6 mil,其他设置不变,仿真波形如图9所示。

图9:不同介质层厚度的仿真结果

考察以上的仿真波形可知,当介质层厚度为3 mil时,近端串扰峰值为153.2 mV,远端串扰为99.5 mV;当介质层厚度为6 mil时,近端串扰峰值为277.3 mV,远端串扰为163.9 mV。

可见,随着介质层厚度的减小,串扰也将变小。

-

串扰

+关注

关注

4文章

196浏览量

27874 -

仿真分析

+关注

关注

3文章

115浏览量

34223

原文标题:龙泉寺,一夜之间被刷屏的神秘组织!

文章出处:【微信号:Interflow-Platform,微信公众号:WPR】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

碳化硅MOSFET串扰抑制策略深度解析:负压关断与寄生电容分压的根本性优势

EXCUSE ME,表层的AC耦合电容和PCB内层的高速线会有串扰?

为什么“负压够深”是解决SiC MOSFET串扰问题的最有力措施

隔离地过孔要放哪里,才能最有效减少高速信号过孔串扰?

昊衡科技全新推出——偏振串扰分析仪OLI-P助力保偏光纤系统性能跃升

SiC MOSFET并联均流及串扰抑制驱动电路的研究

技术资讯 I 哪些原因会导致近端和远端串扰?

高速AC耦合电容挨得很近,PCB串扰会不会很大……

高速AC耦合电容挨得很近,PCB串扰会不会很大……

NEXT(Near-End Crosstalk,近端串扰)

OLI-P——分布式偏振串扰测量利器

白光干涉精析偏振串扰,OLI-P重新定义保偏光纤检测新标准

串扰的仿真分析

串扰的仿真分析

评论