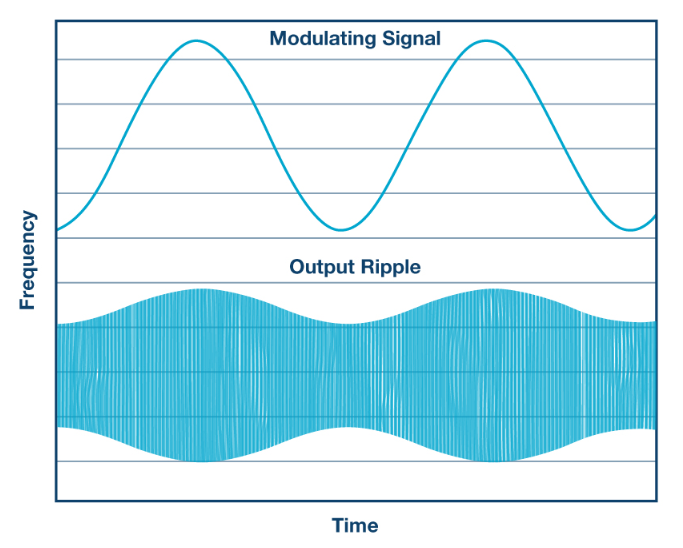

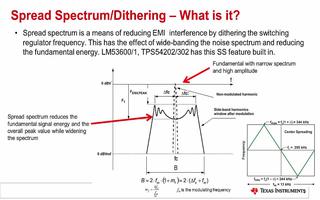

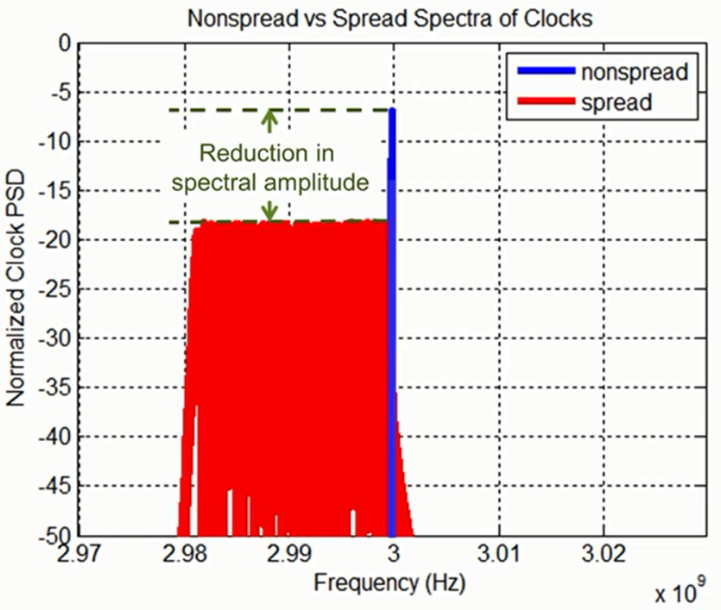

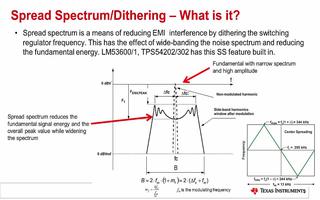

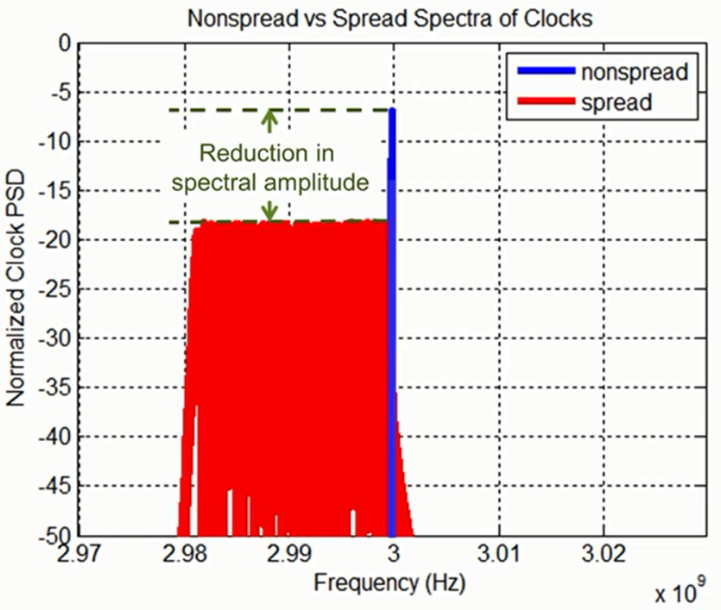

ADI 公司为减少传导干扰和辐射干扰实施的一项技术是扩频频率调制 (SSFM)。该技术用于我们一些基于电感和电容的开关电源、硅振荡器和 LED 驱动器,将噪声扩展到更宽的频带上,从而降低特定频率下的峰值噪声和平均值噪声。

2020-02-28 09:46:40 4236

4236

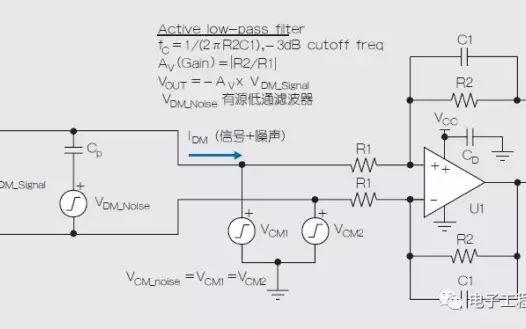

本文介绍了如何准确地估算采样时钟抖动,以及如何计算正确的上下整合边界。

2012-04-01 10:19:38 2333

2333

为了正确理解时钟相关器件的抖动指标规格,同时选择抖动性能适合系统应用的时钟解决方案,本文详细介绍了如何理解两种类型时钟驱动器的抖动参数,以及从锁相环输出噪声特性理解时钟器件作为合成器、抖动滤除功能时的噪声特性。

2013-06-21 15:40:41 19928

19928

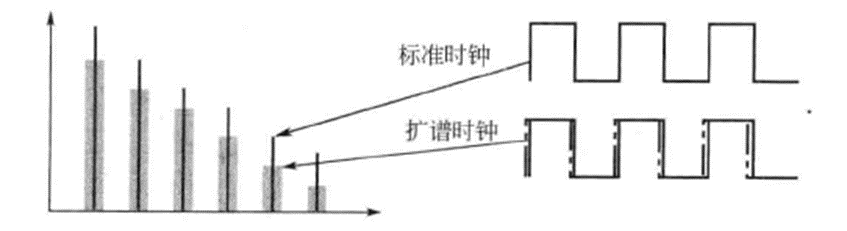

本文介绍了时钟扩频技术的原理、分类,结合它在摄像头的具体应用案例,与传统EMI抑制手段的实际效果进行对比,突显时钟扩频技术在抑制时钟EMI上的优势。目前,时钟扩展频谱技术被广泛使用在图像采集、图像

2018-05-18 02:13:00 3137

3137

为了应对日益紧缩的时钟抖动预算,麦瑞半导体(Micrel, Inc)已推出两个全新系列的ClockWorks超低抖动时钟合成器,能够满足这些精确计时要求。SM84xxxx标准时钟合成器系列,以及ClockWorks Flex可编程时钟系列的首台新型合成器SM802xxx。

2018-10-31 08:24:00 4690

4690 时钟抖动是相对于理想时钟沿实际时钟存在不随时间积累的、时而超前、时而滞后的偏移称为时钟抖动,简称抖动

2023-11-08 15:08:01 3278

3278

在本文中,我们将讨论抖动传递及其性能,以及相位噪声测量技术的局限性。 时钟抖动和边沿速率 图1显示了由一个通用公式表述的三种波形。该公式包括相位噪声项“φ(t)”和幅度噪声项“λ(t)。对评估的三个

2022-11-23 07:59:49

开关架构,具有一个内部旁路电容器以降低辐射EMI。电容器将吸收多余的EMI电流(在充电模式下)。此外,开发人员可以通过建议的PCB布局,通过在调节器附近添加两个小的1微法(uF)电容器来进一步降低EMI

2021-12-27 09:31:00

CC2530芯片 ZED 和ZC,在组网正常的情况下,ZED可以进入低功耗模式,电流在uA级别。当关闭ZC后,ZED会持续的进行网络发现,无法进入低功耗模式。电流达28mA;求教,如何降低ZC发现网络的频次以降低功耗?或者有其他什么方法来降低功耗?

2016-04-07 14:19:54

STM8在低功耗模式下可以降低主频运行吗

2023-10-11 06:57:20

cc2640修改哪些参数可以降低连接后的功耗?cc2640我使用simpleBLEMulti修改的多角色从机连接,未连接的时候,待机功耗1.7uA,但是连接后,功耗0.2mA。我看文档,连接后不会

2016-04-01 11:43:28

,频率固定在396MHz;设备树里关掉了不用的外设;imx6q的GPU频率是否可以降低?还有没有什么其他方法可以降低功耗的?谢谢。

2022-01-10 07:30:09

如图,这个ADP150给PLL供电为什么可以降低相位噪声

2019-01-10 09:49:23

你知道有哪些措施可以降低单片机系统的功耗吗?

2021-12-20 08:00:04

各种抖动技术规范是什么抖动的影响有哪些

2021-04-06 09:22:00

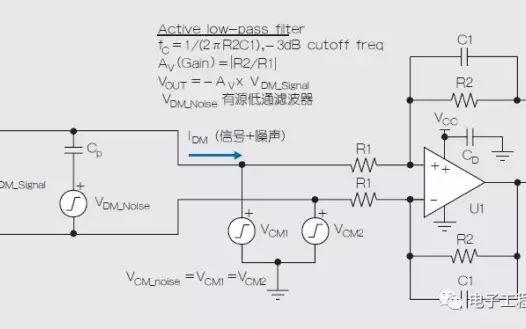

本文针对全方位的信号路径系统中的高速全差分运放及高频宽14位模拟/数字转换器的随机及固定时钟抖动,具体分析、研究了超低噪声兼时钟抖动滤除技术。研究选用双级联PLLatinum架构,配置高性能压控振荡器(VCXO),很好地实现了降噪和时钟抖动滤除的作用。

2019-07-05 07:47:46

ZED 和ZC,在组网正常的情况下,ZED可以进入低功耗模式,电流在uA级别。CC2530芯片当关闭ZC后,ZED会持续的进行网络发现,无法进入低功耗模式。电流达28mA;求教TI工程师,如何降低ZC发现网络的频次以降低功耗?或者有其他什么方法来降低功耗?

2020-08-07 07:03:22

问题:如何使用摆率控制来降低EMI?

2019-03-05 20:59:44

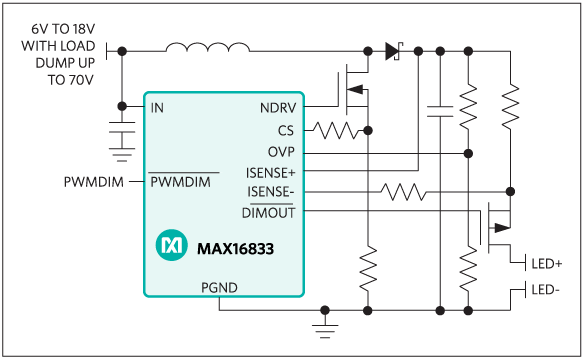

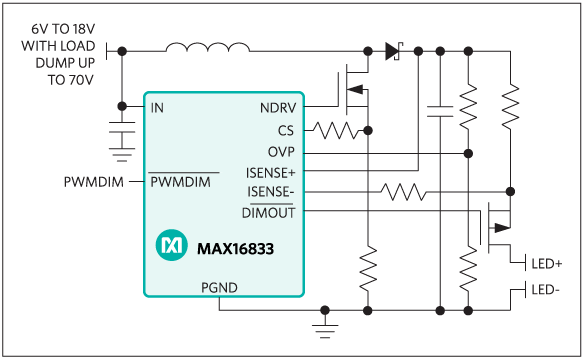

问题:如何通过驱动高功率LED降低EMI?

2019-03-05 14:33:29

应用基准的CISPR 25,以及针对信息技术设备的CISPR 22。如何降低电源设计的EMI辐射呢?一种方法是用金属完全屏蔽开关电源。但在大多数应用中,由于成本和空间的原因,这种方法无法实现。一种更好的方法

2019-06-03 00:53:17

刚学没多久,关于数字地模拟地怎么连接不是很会啊,为了区分我把模拟地改为GND1了,这样连接可以吗?摄像头这样连接,可以降低高频干扰吗?发了一下自己画的PCB,希望各位大神给点建议啊!PCB.zip (84.32 KB )

2019-04-08 09:35:47

有什么方法可以降低D类放大器音频中的电磁干扰吗?

2021-06-04 06:12:13

有什么方法可以降低IC封装的热阻吗?求解

2021-06-23 07:24:48

液晶显示(LCD)技术的基本原理是什么?液晶显示(LCD)噪声产生的原因是什么?有什么方法可以降低LCD的噪声?

2021-05-31 06:08:04

请问有什么方法可以降低Linux的成本吗?

2021-04-25 06:15:12

有什么方法可以降低微波/射频器件的成本吗?

2021-05-25 06:49:40

有什么方法可以降低电缆的电感量吗?

2021-05-11 07:02:45

),原边RCD吸收电路(R7,C5,D6和R8),二次侧RC吸收(R14,C6)以及结构优化的变压器以降低共模EMI干扰。2.2变压器设计中的共模噪声抑制技术图4显示了变压器内部的电荷分布结构,其中Qps

2018-06-11 09:36:41

看到有文章说滤波的时候提高电容容量可以降低负荷,增加使用寿命,这种说法正确吗?这样做有什么弊端吗?

2023-09-27 07:54:19

电源门控可以降低泄漏功耗吗?有哪几种情况采用PG能显著减小泄漏功耗呢?

2022-02-11 06:34:36

一块音视频处理芯片输出1080i的数据Data及其同步时钟Clk,但是时钟clk的抖动很大,我该如何处理呢?另外,抖动很大的时钟源能否在后面接入一个模拟锁相环降低时钟的抖动呢?

2018-11-12 09:12:43

时钟抖动或结束时钟抖动的最佳方法是什么?

2021-03-17 07:04:07

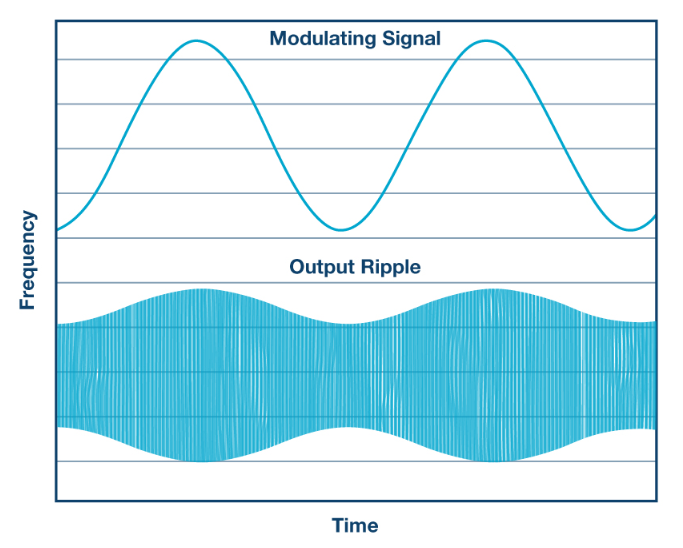

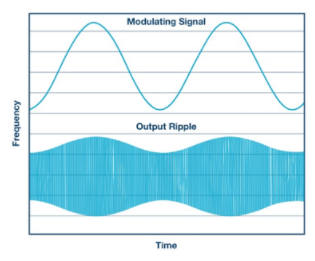

Jitter)是一种从分散谐波干扰能量着手解决EMI问题的新方法。频率抖动技术是指开关电源的工作频率并非固定不变,而是周期性地由窄带变为宽带的方式来降低EMI,来减小电磁干扰的方法。 频率抖动技术

2013-02-01 15:30:40

AD811和AD744应用电路的设计可以降低结型FET运算放大器的谐波失真:

2009-06-02 10:50:26 46

46 本文主要讨论采样时钟抖动对ADC 信噪比性能的影响以及低抖动采样时钟电路的设计。

2009-11-27 11:24:07 15

15 摘要:这是一篇关于时钟(CLK)信号质量的应用笔记,介绍如何测量抖动和相位噪声,包括周期抖动、逐周期抖动和累加抖动。本文还描述了周期抖动和相位噪声谱之间的关系,并介绍

2009-04-22 10:16:50 4761

4761

理解不同类型的时钟抖动

抖动定义为信号距离其理想位置的偏离。本文将重点研究时钟抖动,并探讨下面几种类型的时钟抖动:相邻周期抖动、周期抖动、时间间隔误

2010-01-06 11:48:11 2094

2094

时钟抖动时域分析(下):

2012-05-08 15:26:25 29

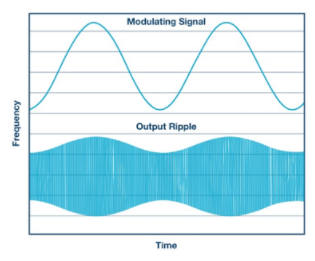

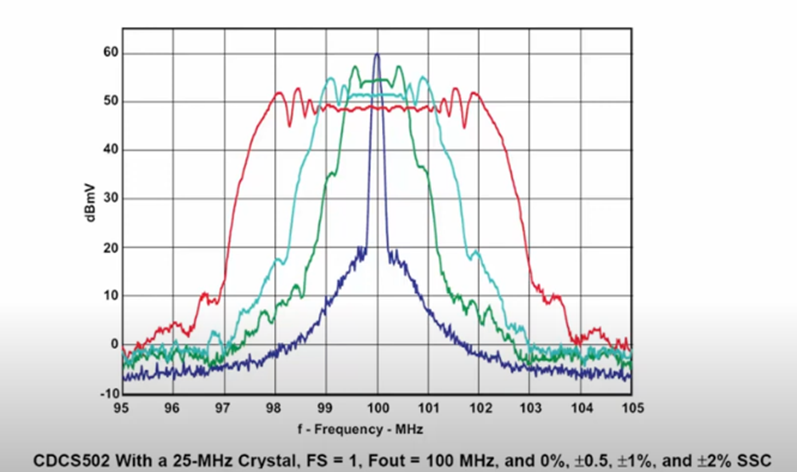

29 设计人员可以通过控制器的开关频率抖动,减少一个脉冲宽度调制(PWM)控制器的电磁干扰(EMI)分布中频谱分量的峰值幅度。时钟抖动扩频技术并非意在取代传统的EMI降低技术,但它们与传统技术的结合使用,可以减少系统中的EMI分布。它们还可以利用减少通过某些排放标准所需的屏蔽和滤波量来降低成本。

2013-02-19 14:07:10 3441

3441

的系统设计,如在某些情况下系统性能极限由系统决定时序裕量。所以对时序抖动有很好的了解在系统设计中变得非常重要。总抖动可以随机抖动和确定性抖动分离组件。我们将不讨论抖动的组件本申请说明。我们将专注于不同类型的时钟

2017-04-01 16:13:18 6

6 很多人都知道,抖动(这是时钟边沿不确定性)是不好的现象,其不仅可导致噪声增加,而且还会降低数据转换器的有效位数 (ENOB)。例如,如果系统需要 100MHz 14(最小值)位的 ENOB,我们

2017-04-08 04:51:23 1767

1767

级,从而降低成本和功耗。在欠采样接收机设计中必须要特别注意采样时钟,因为在一些高输入频率下时钟抖动会成为限制信噪比(SNR) 的主要原因。 本系列文章共有三部分,第1 部分重点介绍如何准确地估算某个时钟源的抖动,以及如何将其与AD

2017-05-18 09:47:38 1

1 采用频率抖动技术减小EMI 为抑制开关电源电磁干扰新思路

2017-09-14 14:08:01 14

14 SSCG是一种Active且低成本的解决EMI问题的方案,可以在保证时钟信号完整性的基础上应对更广频率范围内EMI问题。相比传统上使用Ferrite Beads和RF Chokes抑制EMI

2018-08-22 14:45:27 10026

10026 工业及汽车系统的低EMI电源变换器设计(六)通过频率抖动有效降低EMI

2019-04-08 06:07:00 2525

2525

优秀PCB设计练习降低PCB的EMI有许多方法可以降低PCB设计的EMI基本原理:电源和地平面提供屏蔽顶层和

2019-02-28 15:04:20 4248

4248

时钟设计人员通常会提供一个相位噪声,但不提供抖动规格。相位噪声规格可以转换为抖动,首先确定时钟噪声,然后通过小角度计算将噪声与主时钟噪声成分进行比较。相位噪声功率通过计算图9中的灰色区域积分得出。

2019-08-20 11:06:53 9314

9314

优秀PCB设计练习降低PCB的EMI有许多方法可以降低PCB设计的EMI基本原理:电源和地平面提供屏蔽顶层和

2019-08-20 09:11:38 5065

5065 时钟抖动性能主题似乎是时钟,ADC和电源的当前焦点供应厂家。理由很清楚;时钟抖动会干扰包括高速ADC在内的数字电路的性能。高速时钟可以对它们所接收的功率的“清洁度”非常敏感,尽管量化关系需要一些努力。

2019-09-14 11:24:00 9399

9399

本文针对全方位的信号路径系统中的高速全差分运放及高频宽14位模拟/数字转换器的随机及固定时钟抖动,具体分析、研究了超低噪声兼时钟抖动滤除技术。研究选用双级联PLLatinum架构,配置高性能压控振荡器(VCXO),很好地实现了降噪和时钟抖动滤除的作用。

2020-09-23 10:45:00 2

2 使用合适的去耦电容可以降低电源/地平面的噪声, 并由此来消弱来自这些平面的EMI。

2020-10-10 11:36:18 3328

3328

随着元件集成度越来越高,设备小型化,电子产品的EMI问题日渐严重。降低模块电源EMI,可以降低EMI的危害,避免传输信号质量问题,对电路或设备造成干扰甚至破坏,设备不能满足电磁兼容标准所规定的技术指标要求等问题。

2020-10-16 10:12:43 1604

1604 全局时钟资源是一种专用互连网络,它可以降低时钟歪斜、占空比失真和功耗,提高抖动容限。Xilinx的全局时钟资源设计了专用时钟缓冲与驱动结构,从而使全局时钟到达CLB、IOB和BRAM的延时最小。

2020-12-29 16:59:35 8

8 MT-200:降低ADC时钟接口抖动

2021-03-21 01:18:30 7

7 电子发烧友网为你提供相位噪声处理:时钟抖动或结束时钟抖动的最佳方法是什么?资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-04 08:49:06 26

26 电磁突破可以降低功耗,提高数字存储器的速度。克里斯蒂安·比内克(Christian Binek)说,“达到这一点是一个非常痛苦的过程。”

2021-04-14 16:40:36 2295

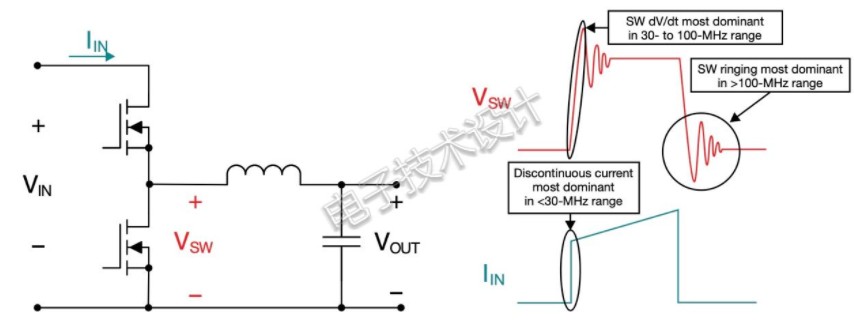

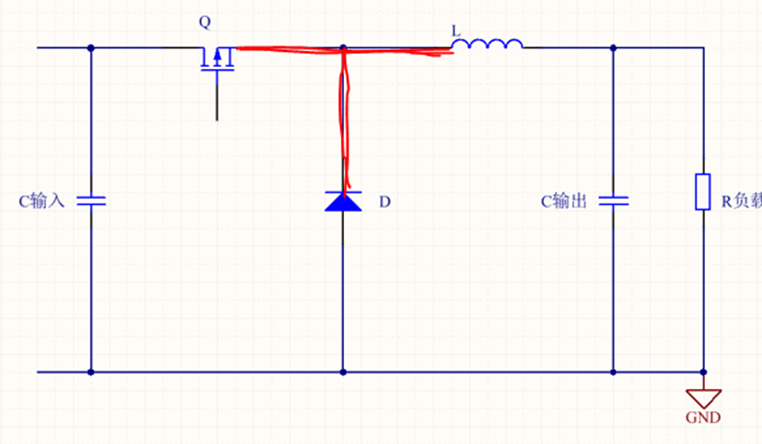

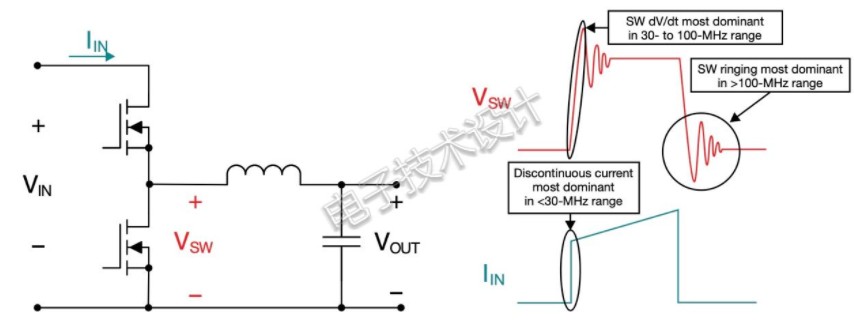

2295 图1以降压转换器拓扑为例,说明了不同频带下各个因素的影响。随着设计压力不断提升,通过提高开关频率来降低尺寸和成本,以及通过增大压摆率来提高效率,使EMI问题变得更加严重。因此,有必要采用不影响电源设计、同时具有成本效益且易于集成的EMI缓解技术。

2021-05-01 09:17:00 5020

5020

超低抖动时钟的产生与分配

2021-04-18 14:13:51 8

8 DN305双单片降压稳压器提供两个1.4A输出,带两相开关以降低EMI

2021-05-07 11:26:01 1

1 用时钟展频技术降低EMI技术探索用时钟展频技术降低EMI技术探索 汽车电子系统和工业系统变复杂且密集,因此如何降低电磁干扰(EMI)的影响成为了工程师在设计之初,就必须要考虑的因素。干扰源通过一定

2021-06-21 14:33:37 1132

1132 KOYUELEC光与电子提供技术支持,有容微电子GM50101:超低附加抖动时钟缓冲器。

2022-05-07 11:40:15 1917

1917 内部频率抖动(或调制)也有助于控制 EMI。调制开关频率时,可以降低峰值能量并将其重新分配到其他频率及其谐波。

2022-05-24 10:18:00 1946

1946

ADI 公司还有许多其他产品可以有效地使用设计技术来降低 EMI。如前所述,使用 SSFM 是一种技术。其他方法包括减慢快速内部时钟边沿和内部过滤。

2022-06-20 15:36:59 2865

2865

减少D类音频放大器中的电磁干扰(EMI)以降低材料清单(BOM)成本却不影响音频性能

2022-11-03 08:04:46 0

0 时钟抖动使随机抖动和相位噪声不再神秘

2022-11-07 08:07:29 4

4 时钟抖动解秘—高速链路时钟抖动规范基础知识

2022-11-07 08:07:30 2

2 模拟输出信号处的电磁干扰(EMI)杂散。利用相位控制架构而非传统PLL,SCG系统被证明可以将分频时钟脉冲的频谱高度降低到9.6dB。

2023-02-14 16:43:56 0

0 ,从而降低发射峰值的幅度。本应用笔记将展示DS1086如何与两个常见的微控制器(8051和PIC)连接。将讨论设计注意事项,因为随着抖动引入系统,系统设计人员应了解抖动可能对整个系统产生的影响。除了降低EMI之外,本文还讨论了使用DS1086代替晶体振荡器的其他优点。

2023-03-01 15:33:18 2412

2412

1.1.1. 抖动定义和分类 ITU-T G.701对抖动的定义为:“抖动是指数字信号在短期内相对于理想位置发生的偏移重大影响的短时变化”。 对于真实物理世界中的时钟源,比如晶振、DLL、PLL,它们的时钟输出周期都不可能是一个单点的固定值,而是随时间而变化的

2023-03-10 14:54:32 1847

1847

扩频时钟是以受控方式对系统时钟进行抖动以降低峰值能量含量的过程。SSC技术用于最小化电磁干扰(EMI)和/或通过联邦通信委员会(FCC)的要求。

2023-05-26 16:51:37 11110

11110

先来聊一聊什么是时钟抖动。时钟抖动实际上是相比于理想时钟的时钟边沿位置,实际时钟的时钟边沿的偏差,偏差越大,抖动越大。实际上,时钟源例如PLL是无法产生一个绝对干净的时钟。这就意味着时钟边沿出现在

2023-06-09 09:40:50 3109

3109

本文主要介绍了时钟偏差和时钟抖动。

2023-07-04 14:38:28 3231

3231

rfi滤波器可以降低电流谐波吗? 随着电子技术的发展,现代电子设备在使用过程中会产生大量的电源谐波,这些谐波会对电网和电气设备产生严重的影响。因此,为了降低电源谐波对电气设备的影响,人们采用了不同种

2023-09-21 16:48:58 1869

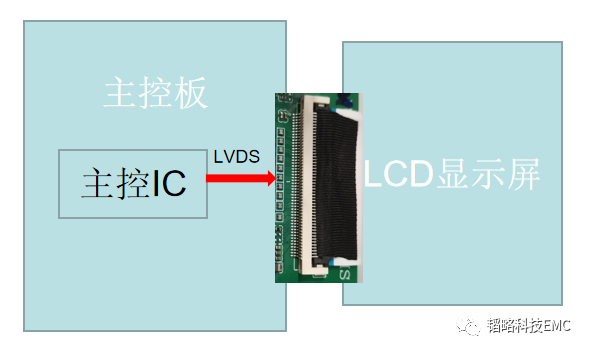

1869 随着电子技术的发展,我们的生活中充满着形形色色的电子产品,LCD显示屏便是其中之一,被广泛应用在手机,电脑,仪表等产品上,目前主流的LCD显示接口为RGB,LVDS,mipi和HDMI。今天跟大家分享的案例为某LCD仪表的LVDS时钟EMI辐射超标问题处理,一起来看看吧。

2023-10-17 16:11:52 2116

2116

有哪些方法能够降低开关电源EMI的影响呢? 降低开关电源电磁干扰(EMI)的影响是一个重要的问题,特别是在要求电子设备对EMI敏感的应用中。下面是一些可以帮助减少EMI影响的方法: 1. 使用滤波器

2023-11-07 10:35:10 1637

1637 放大器自身的电流噪声通过何种方案可以降低呢?是在前端进行抑制还是后端的过滤? 放大器自身的电流噪声是放大器设计中的一个重要问题。通过合理的设计和维护可以降低放大器自身的电流噪声。在实际应用中,通常

2023-11-09 10:02:19 1215

1215 时钟抖动(Clock Jitter)是时钟信号领域中的一个重要概念,它指的是时钟信号时间与理想事件时间的偏差。这种偏差不仅影响数字电路的时序性能,还可能对系统的稳定性和可靠性造成不利影响。以下是对时钟抖动工作原理的详细阐述,内容将围绕其定义、类型、产生原因、影响及应对措施等方面展开。

2024-08-19 17:58:11 5343

5343 在FPGA(现场可编程门阵列)设计中,消除时钟抖动是一个关键任务,因为时钟抖动会直接影响系统的时序性能、稳定性和可靠性。以下将详细阐述FPGA中消除时钟抖动的多种方法,这些方法涵盖了从硬件设计到软件优化的各个方面。

2024-08-19 17:58:54 3756

3756 时钟抖动(Jitter)和时钟偏移(Skew)是数字电路设计中两个重要的概念,它们对电路的时序性能和稳定性有着显著的影响。下面将从定义、原因、影响以及应对策略等方面详细阐述时钟抖动和时钟偏移的区别。

2024-08-19 18:11:30 3230

3230 电子发烧友网站提供《CDCE(L)949:支持SSC以降低EMI的灵活低功耗LVCMOS时钟发生器数据表.pdf》资料免费下载

2024-08-20 11:01:12 0

0 电子发烧友网站提供《EMI降低技术:双随机展频.pdf》资料免费下载

2024-08-23 09:16:53 1

1 无功补偿,也称为无功功率补偿,是指在电力系统中,通过增加无功功率来改善电能质量,提高电力系统的稳定性和效率。无功补偿可以降低电流,但并不是直接降低电流,而是通过改善电力系统的功率因数来实现的。 一

2024-08-27 15:23:42 1699

1699 一前言随着信息技术和半导体技术的快速发展,电子产品的类型和功能模块日益多样化,对此要求的传输速率也日益提高。其中时钟频率的不断提升,同时也带来了更多的EMI时钟问题。时钟EMI问题的处理还受到了很多

2025-03-11 11:34:02 1108

1108

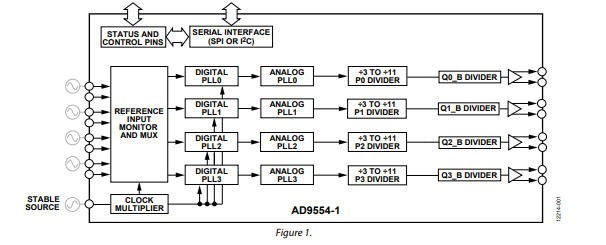

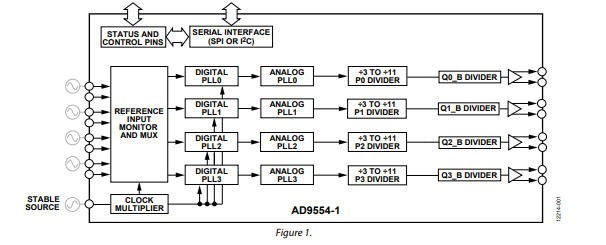

。 DPLL可以降低与外部参考时钟相关的输入时间抖动或相位噪声。 借助数字控制环路和保持电路,即使所有参考输入都失效,AD9554-1也能持续产生低抖动输出时钟。

2025-04-10 11:21:01 794

794

(DPLL)可以降低与外部参考时钟相关的输入时间抖动或相位噪声。 借助数字控制环路和保持电路,即使所有参考输入都失效,AD9554也能持续产生低抖动输出时钟。

2025-04-10 11:51:07 839

839

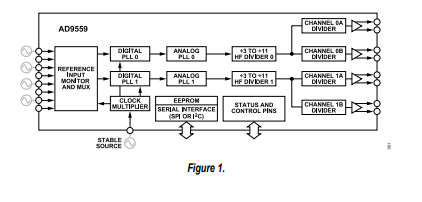

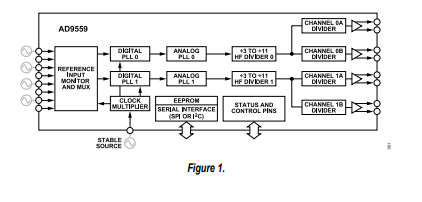

AD9559是一款低环路带宽时钟倍频器,可针对包括同步光纤网络(SONET/SDH)的许多系统提供抖动清除和同步功能。AD9559产生的输出时钟可以与多达四路外部输入参考时钟同步。DPLL可以降低

2025-04-10 14:35:01 932

932

AD9547针对许多系统提供同步功能,包括同步光纤网络(SONET/SDH)。该器件产生的输出时钟可以与两路差分或四路单端外部输入参考时钟之一同步。数字锁相环(PLL)可以降低与外部参考时钟

2025-04-11 09:37:58 758

758

该LMK05318是一款高性能网络同步器时钟器件,可提供抖动清除、时钟生成、高级时钟监控和卓越的无中断开关性能,以满足通信基础设施和工业应用的严格时序要求。该器件的超低抖动和高电源噪声抑制 (PSNR) 可降低高速串行链路中的误码率 (BER)。

2025-09-12 13:49:59 687

687

电子发烧友App

电子发烧友App

评论