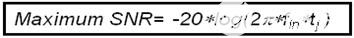

本文介绍了如何准确地估算采样时钟抖动,以及如何计算正确的上下整合边界。

2012-04-01 10:19:38 2333

2333

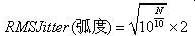

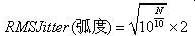

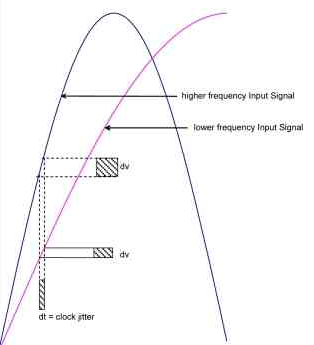

本系列文章共有三部分,第 1 部分重点介绍如何准确地估算某个时钟源的抖动,以及如何将其与 ADC 的孔径抖动组合。在第 2 部分中,该组合 抖动 将用于计算 ADC 的 SRN,然后将其与实际

2012-05-07 11:37:30 3382

3382

Analog Devices, Inc. (NASDAQ: ADI) 全球领先的高性能信号处理解决方案供应商,最近推出一款具有业界最低抖动特性的 RF 时钟 IC(射频时钟集成电路)AD9525

2012-11-02 10:16:53 4736

4736 为了正确理解时钟相关器件的抖动指标规格,同时选择抖动性能适合系统应用的时钟解决方案,本文详细介绍了如何理解两种类型时钟驱动器的抖动参数,以及从锁相环输出噪声特性理解时钟器件作为合成器、抖动滤除功能时的噪声特性。

2013-06-21 15:40:41 19925

19925

了解抖动如何抑制谐波和非谐波杂散以及两种不同类型的抖动系统:减法和非减法拓扑。

2023-02-27 14:25:08 2439

2439

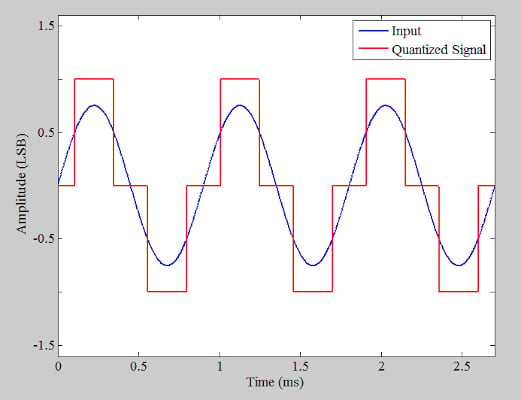

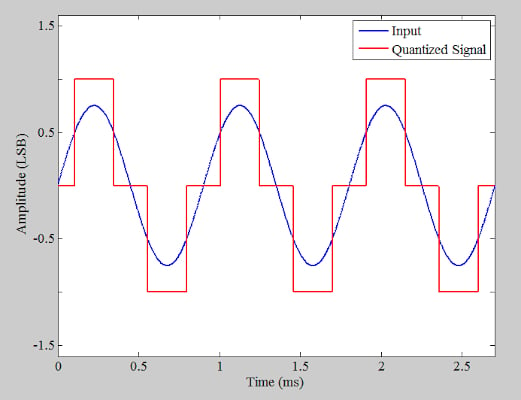

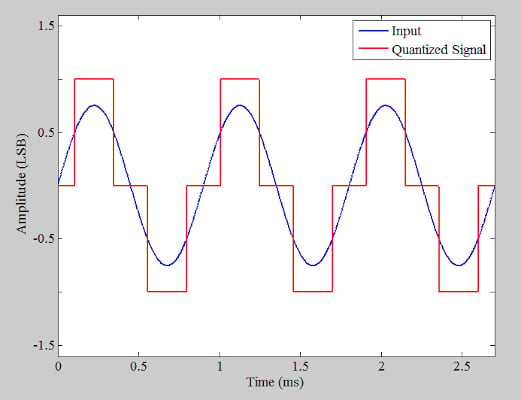

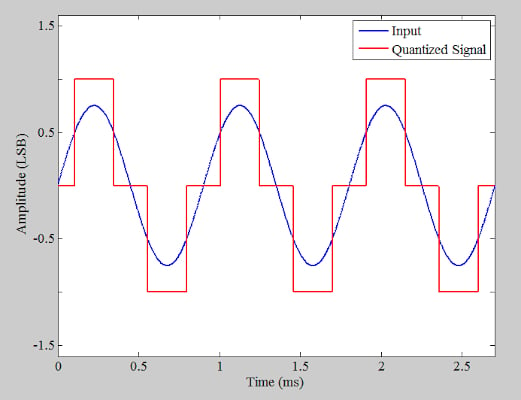

了解抖动如何抑制谐波和非谐波杂散以及两种不同类型的抖动系统:减法和非减法拓扑。 量化小幅度信号会在量化误差和输入之间产生相关性,从而导致明显的谐波分量。高频谐波可以混叠回奈奎斯特间隔,其频率可能是

2023-05-03 11:14:00 2268

2268

时钟抖动技术适合于各种周期性的脉冲信号,典型的是电力电子设备中的PWM电压和数字电路中的时钟信号。

2023-09-11 10:55:34 2596

2596

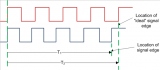

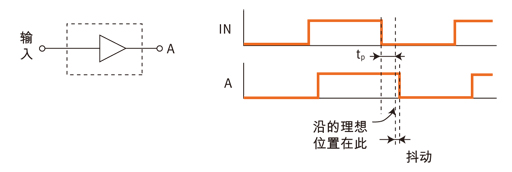

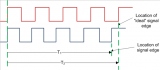

时钟抖动是相对于理想时钟沿实际时钟存在不随时间积累的、时而超前、时而滞后的偏移称为时钟抖动,简称抖动

2023-11-08 15:08:01 3278

3278

电子发烧友网报道(文/程文智)不论我们设计的电子产品是应用在云计算、无线LTE、数据中心,还是物联网、汽车、医疗保健,或者是航空航天等领域,系统内必然需要时钟产品的支持,时钟产品就如人类的脉搏一样

2021-09-06 07:18:00 9228

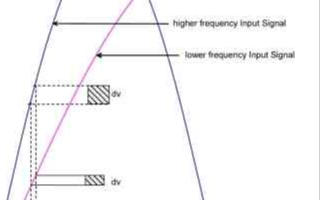

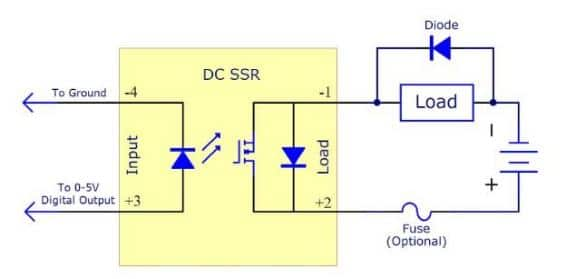

9228 在本文中,我们将讨论抖动传递及其性能,以及相位噪声测量技术的局限性。 时钟抖动和边沿速率 图1显示了由一个通用公式表述的三种波形。该公式包括相位噪声项“φ(t)”和幅度噪声项“λ(t)。对评估的三个

2022-11-23 07:59:49

转时钟抖动的理解

2016-10-05 12:08:25

什么是LoRaWAN?LoRaWAN包含哪几种不同类型的节点?

2021-06-16 08:23:31

` 本帖最后由 zilan66 于 2014-9-17 15:20 编辑

本人新手一枚,将两个簇3元素的数据组合成一个1D数组,与类型为簇3元素的数据接收端连接失败,具体为: 已连接两个不同类型的接线端。数据源的类型是1D数组,内容为簇3元素。数据接收端的类型是簇3元素。请问如何解决?`

2014-09-17 15:19:15

不同类型放大电路共有的特点

2021-03-29 08:07:19

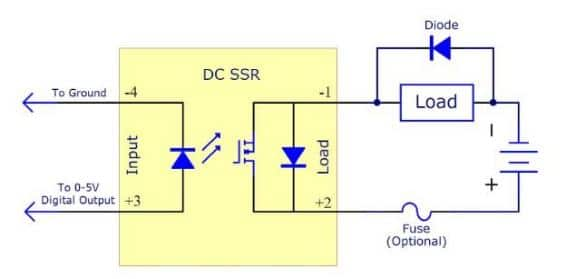

不同类型无触点开关的性能比较

2019-04-15 09:04:01

什么是抖动?抖动有哪些类型?

2021-06-24 07:23:50

,TIE 测量非常有用。如果 TIE 值比较大,则表明恢复的时钟 PLL 无法跟上信号数据速率的变化。图3:时间间隔误差测量感谢阅读《定时决定一切》!希望您现在对抖动技术规范有了更好的理解。 更多资源

2018-09-13 14:29:18

本文详细介绍了如何理解两种类型时钟驱动器的抖动参数,以及从锁相环输出噪声特性理解时钟器件作为合成器、抖动滤除功能时的噪声特性。

2021-04-07 06:30:45

如何推导ADC的SNR?如何准确地估算某个时钟源的抖动?如何将其与ADC的孔径抖动组合?

2021-05-13 06:17:20

采样时钟抖动对ADC信噪比的性能有什么影响?如何实现低抖动采样时钟电路的设计?

2021-04-14 06:49:20

。这工作正常,直到我决定董事会所做的测量不够准确(在时间轴上)。因此,我将生成的时钟使能信号(2MHz)输出到IO-Pin,并使用示波器测量频率抖动。抖动似乎具有高斯分布,标准偏差约为28ns。我还测量

2020-08-19 06:09:57

需求。作为该最新博客系列的开篇文章,我将帮助您了解如何正确测量时钟缓冲器的附加抖动。为什么抖动很重要?在当今数据通信、有线及无线基础设施以及其它高速应用等高级系统中,时钟抖动是整体系统性能的关键因素。要

2018-09-13 14:38:43

请问上面的情况如何解决呢?就是两个不同类型的连线端如何连接到一起,或者如何改变为同类型的呢?小弟初学,谢谢您的帮助!

2011-07-23 10:08:00

伺服电机的特点有哪些?伺服电机有哪几种类型?不同类型伺服电机相应的控制原理是什么?

2021-06-17 10:50:13

一块音视频处理芯片输出1080i的数据Data及其同步时钟Clk,但是时钟clk的抖动很大,我该如何处理呢?另外,抖动很大的时钟源能否在后面接入一个模拟锁相环降低时钟的抖动呢?

2018-11-12 09:12:43

时钟抖动或结束时钟抖动的最佳方法是什么?

2021-03-17 07:04:07

?疑问3:是不是使用PLL类型的时钟发生器芯片带来的抖动误差会比较大?针对14位的ADC输入差分时钟有此类型的参考吗? 模拟输入部分:疑问1:参考文档中使用AD8138差分驱动芯片,计划采用5v单电源模式

2018-11-07 09:35:54

随着数据速率的提高,时钟抖动分析的需求也在与日俱增。在高速串行数据链路中,时钟抖动会影响发射机、传输线和接收机的数据抖动。保证时钟质量的测量也在不断发展

2008-12-27 12:24:05 6

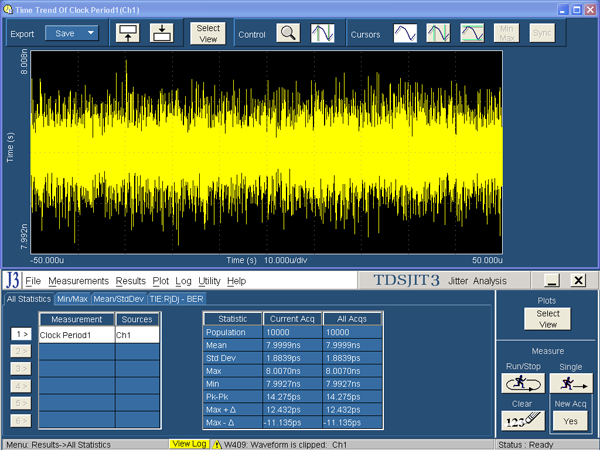

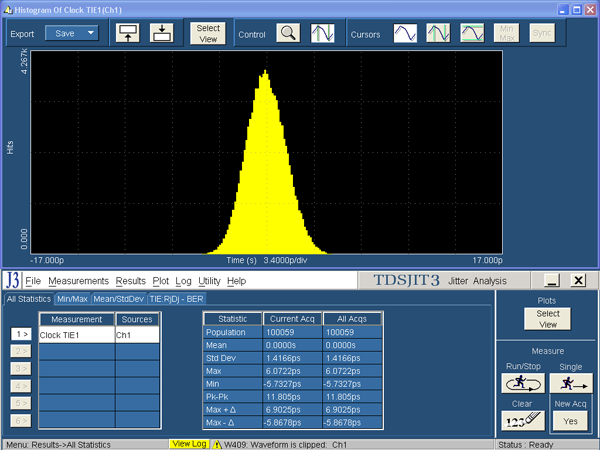

6 随着数据速率的提高,时钟抖动分析的需求也在与日俱增。在高速串行数据链路中,时钟抖动会影响发射机、传输线和接收机的数据抖动。保证时钟质量的测量也在不断发展。目前

2009-07-07 14:01:21 20

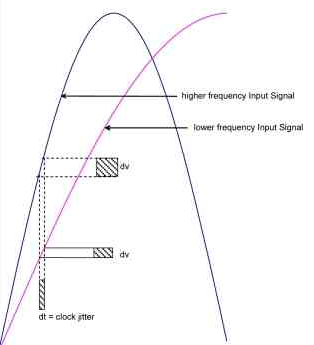

20 本文主要讨论采样时钟抖动对ADC 信噪比性能的影响以及低抖动采样时钟电路的设计。

2009-11-27 11:24:07 15

15 高速互联链路中参考时钟的抖动分析与测量

在高速互联链路中,发送器的参考工作时钟的抖动是影响整个

2010-04-15 14:01:39 19

19

抖动的概念和抖动的测量方法

在数字通信系统,特别是同步系统中,随着系统时钟频率的不断提高,时间抖动成为影响通

2008-11-27 08:28:11 5084

5084

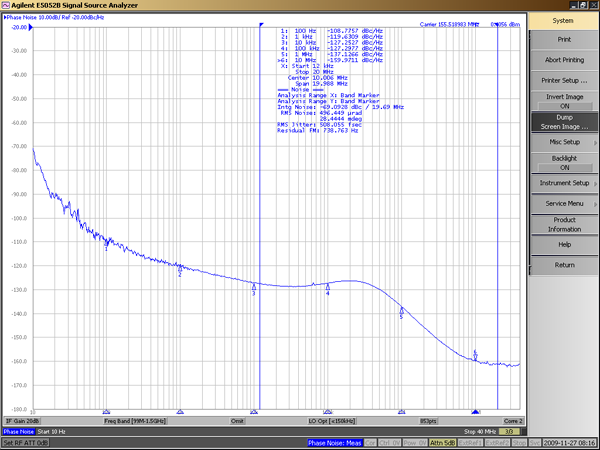

该应用笔记提出了超低抖动时钟合成器的一种设计思路,其目标是产生2GHz时钟时,边沿之间的抖动< 100fs。分析和仿真结果表明,要达到这一抖动指标,设计难度远远高于预期。关

2009-04-21 23:14:05 1036

1036

摘要:该应用笔记提出了超低抖动时钟合成器的一种设计思路,其目标是产生2GHz时钟时,边沿之间的抖动< 100fs。分析和仿真结果表明,要达到这一抖动指标,设计难度远远高于预

2009-04-22 09:35:13 410

410

摘要:这是一篇关于时钟(CLK)信号质量的应用笔记,介绍如何测量抖动和相位噪声,包括周期抖动、逐周期抖动和累加抖动。本文还描述了周期抖动和相位噪声谱之间的关系,并介绍

2009-04-22 10:16:50 4761

4761

摘要:该应用笔记提出了超低抖动时钟合成器的一种设计思路,其目标是产生2GHz时钟时,边沿之间的抖动< 100fs。分析和仿真结果表明,要达到这一抖动指标,设计难度远远高于预

2009-04-25 09:54:26 638

638

摘要:该应用笔记提出了超低抖动时钟合成器的一种设计思路,其目标是产生2GHz时钟时,边沿之间的抖动< 100fs。分析和仿真结果表明,要达到这一抖动指标,设计难度远远高于预

2009-05-08 10:19:03 566

566

用模拟时钟IC替代昂贵的高频率VCO,改善抖动性能

Analog Devices, Inc.,全球领先的高性能信号处理解决方案供应商,

2009-09-01 17:26:25 1723

1723 时钟抖动时域分析(下):

2012-05-08 15:26:25 29

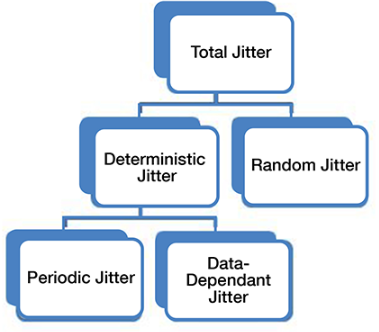

29 介绍 此应用笔记侧重于不同类型的时钟抖动。时钟抖动是从它的时钟边沿偏差理想的位置。了解时钟抖动非常重要在应用中,因为它起着关键作用,在时间预算一个系统。 随着系统数据速率的增加,定时抖动成为关键

2017-04-01 16:13:18 6

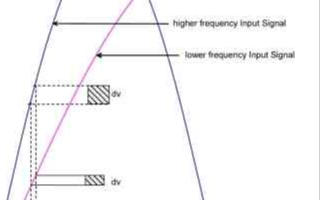

6 很多人都知道,抖动(这是时钟边沿不确定性)是不好的现象,其不仅可导致噪声增加,而且还会降低数据转换器的有效位数 (ENOB)。例如,如果系统需要 100MHz 14(最小值)位的 ENOB,我们

2017-04-08 04:51:23 1767

1767

欢迎继续关注《定时决定一切》系列文章!上次我们探讨了对 PLL 环路滤波器响应的理解。今天,我将帮助您了解如何更好地理解各种抖动技术规范。随着高速应用中的定时要求日趋严格,对各种抖动技术规范的更深入理解

2017-04-08 04:56:31 1217

1217

级,从而降低成本和功耗。在欠采样接收机设计中必须要特别注意采样时钟,因为在一些高输入频率下时钟抖动会成为限制信噪比(SNR) 的主要原因。 本系列文章共有三部分,第1 部分重点介绍如何准确地估算某个时钟源的抖动,以及如何将其与AD

2017-05-18 09:47:38 1

1 基于不同类型Flash-ROM的Bootloader设计

2017-10-26 11:41:23 11

11 时钟抖动时域分析,第 2 部分

2017-10-26 16:10:42 6

6 时钟抖动时域分析 第 3 部分

2017-10-26 16:13:28 4

4 时间域中分析的时钟抖动,第 1 部分

2017-10-26 16:16:23 4

4 不同类型单片机开发的比较

2018-07-06 05:25:00 2978

2978 ADI研讨会:高性能时钟: 解密抖动

2019-08-20 06:05:00 2532

2532 时钟配有体声波(BAW)谐振器,适用于400 Gbps链路,能帮助系统以更高的速度传输更多数据,同时提供比同类产品更高的系统抖动裕量。

2019-06-20 11:37:03 4650

4650 时钟设计人员通常会提供一个相位噪声,但不提供抖动规格。相位噪声规格可以转换为抖动,首先确定时钟噪声,然后通过小角度计算将噪声与主时钟噪声成分进行比较。相位噪声功率通过计算图9中的灰色区域积分得出。

2019-08-20 11:06:53 9314

9314

时钟抖动性能主题似乎是时钟,ADC和电源的当前焦点供应厂家。理由很清楚;时钟抖动会干扰包括高速ADC在内的数字电路的性能。高速时钟可以对它们所接收的功率的“清洁度”非常敏感,尽管量化关系需要一些努力。

2019-09-14 11:24:00 9399

9399

本文针对全方位的信号路径系统中的高速全差分运放及高频宽14位模拟/数字转换器的随机及固定时钟抖动,具体分析、研究了超低噪声兼时钟抖动滤除技术。研究选用双级联PLLatinum架构,配置高性能压控振荡器(VCXO),很好地实现了降噪和时钟抖动滤除的作用。

2020-09-23 10:45:00 2

2 对高速信号进行高分辨率的数字化处理需审慎选择时钟,才不至于使其影响模数转换器(ADC)的性能。借助本文,我们将使读者更好地理解时钟抖动问题及其对高速ADC性能的影响。

2020-08-01 11:26:11 1764

1764

对高速信号进行高分辨率的数字化处理需审慎选择时钟,才不至于使其影响模数转换器(ADC)的性能。借助本文,我们将使读者更好地理解时钟抖动问题及其对高速ADC性能的影响。

2020-08-20 14:25:16 1408

1408

印刷电路板( PCB )是由玻璃纤维,复合环氧树脂或其他层压材料制成的薄板。在各种电气和电子组件(例如蜂鸣器,收音机,雷达,计算机系统等)中都可以找到 PCB 。根据应用情况,可以使用不同类型

2020-09-18 23:35:55 2502

2502 MT-200:降低ADC时钟接口抖动

2021-03-21 01:18:30 7

7 电子发烧友网为你提供相位噪声处理:时钟抖动或结束时钟抖动的最佳方法是什么?资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-04 08:49:06 26

26 前言 :本文我们介绍下ADC采样时钟的抖动(Jitter)参数对ADC采样的影响,主要介绍以下内容: 时钟抖动的构成 时钟抖动对ADC SNR的影响 如何计算时钟抖动 如何优化时钟抖动 1.采样理论

2021-04-07 16:43:45 10607

10607

超低抖动时钟的产生与分配

2021-04-18 14:13:51 8

8 ADC时钟接口中的最小抖动

2021-05-09 12:19:40 6

6 DN1013-了解时钟抖动对高速ADC的影响

2021-05-11 18:22:19 0

0 PCIe 和网络时钟抖动测量之间的另一个显着差异在图 2 中并不明显。数字采样示波器 (DSO) 用于获取时钟周期或波形文件以计算 PCIe 时钟抖动,而不是 PNA。造成这种情况的主要原因是 PCIe 时钟支持扩频,而网络时钟不支持,而且从历史上看,PNA 一直无法使用正在扩频的时钟。

2022-05-05 15:50:44 7109

7109

描述了不同类型换挡器的各功能模块,便于了解各种类型换挡器的工作原理

2022-06-01 16:43:14 0

0 时钟采样系统最大限度减少抖动

2022-11-04 09:52:12 0

0 时钟抖动使随机抖动和相位噪声不再神秘

2022-11-07 08:07:29 4

4 时钟抖动解秘—高速链路时钟抖动规范基础知识

2022-11-07 08:07:30 2

2 对于频率成分相对较低的输入信号,例如在1MHz以下,时钟抖动变得不那么重要,但是当输入信号的频率为几百兆赫兹时,时钟上的抖动将成为误差的主要来源,并且将成为SNR的限制因素。

2023-01-03 14:35:04 2164

2164

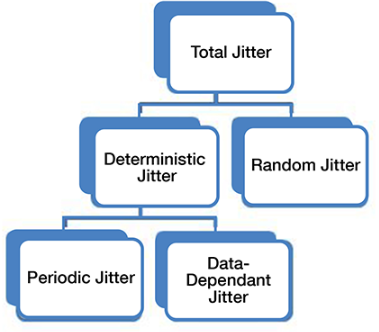

1.1.1. 抖动定义和分类 ITU-T G.701对抖动的定义为:“抖动是指数字信号在短期内相对于理想位置发生的偏移重大影响的短时变化”。 对于真实物理世界中的时钟源,比如晶振、DLL、PLL,它们的时钟输出周期都不可能是一个单点的固定值,而是随时间而变化的

2023-03-10 14:54:32 1847

1847

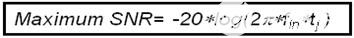

为了满足各行各业的不同需求,工程师们开发了广泛的固态继电器类型。其中包括可用于交流或直流负载电压的继电器、具有特殊功能的继电器等。本文给您介绍了不同类型的 SSR

2023-03-21 18:02:10 3827

3827

在本章中,我们将使用Arduino板(UNO)连接不同类型的电机,并向你展示如何连接电机并从电路板上驱动它。 有三种不同类型的电机:DC motor 直流电机 Servo motor 伺服电机

2023-03-30 11:08:35 0

0 系统时序设计中对时钟信号的要求是非常严格的,因为我们所有的时序计算都是以恒定的时钟信号为基准。但实际中时钟信号往往不可能总是那么完美,会出现抖动(Jitter)和偏移(Skew)问题。

2023-04-04 09:20:56 5281

5281 NIST将抖动定义为“数字信号的重要时刻从其理想位置的短期相位变化”。我们将抖动想象为波的位置变化,形成从它应该在的位置上升或下降沿(“它应该在哪里”的很多意思是导致设计人员可能必须考虑的不同类型的抖动 - 稍后会详细介绍)。

2023-05-05 10:33:24 1685

1685

首先,我们需要理解什么是时钟抖动。简而言之,时钟抖动(Jitter)反映的是时钟源在时钟边沿的不确定性(Clock Uncertainty)。

2023-06-02 09:09:06 3288

3288

先来聊一聊什么是时钟抖动。时钟抖动实际上是相比于理想时钟的时钟边沿位置,实际时钟的时钟边沿的偏差,偏差越大,抖动越大。实际上,时钟源例如PLL是无法产生一个绝对干净的时钟。这就意味着时钟边沿出现在

2023-06-09 09:40:50 3109

3109

本文主要介绍了时钟偏差和时钟抖动。

2023-07-04 14:38:28 3231

3231

目前市场上出现的碳化硅半导体包括的类型相对较多,常见的主要有二极管、金属氧化物、半导体场效应、晶体管、晶闸管、结算场、效应晶体管等等这些不同类型的碳化硅器件,单元结构和漂移区参杂以及厚度之间存在较为明显的差异。那么下文主要针对不同类型的碳化硅功率器件的相关内容进行分析。

2023-08-31 14:14:22 995

995 相噪是与哪种类型的抖动相对应?如何理解相位噪声与时间抖动的关系? 相位噪声与时间抖动是两个在信号处理领域中经常涉及的概念。在讨论相位噪声时,我们常常听到相位噪声和时间抖动的联系。因此,本文将探讨相位

2023-10-20 15:08:11 2180

2180 CW信号可以理解为一种特殊的数字码流信号,理论上只有随机抖动和周期性抖动这两种分量。随机抖动是由宽带噪声引起的,周期性抖动是由串扰引起的,从产生机制上讲,都相当于对信号进行了调频或者调相。

2023-10-29 10:53:42 2359

2359

不同类型的网线在速率上的差异主要取决于它们的类型和规格。

2023-11-16 14:58:40 2576

2576 电子发烧友网站提供《时钟抖动对ADC性能有什么影响.pdf》资料免费下载

2023-11-28 10:24:10 1

1 的PLC程序的关键。 PLC数据类型的基本理解 PLC数据类型是指用于存储和表示数据的方式,它们可以区分为不同类型的数据元素。根据数据的特性,PLC数据类型通常分为以下几种: 数字数据类型:包括整数和实数。整数数据类型用于表示整数数值,

2023-12-19 11:39:27 6492

6492 金刚石是我们都非常熟悉的超硬材料,人造金刚石晶体有多种不同的类型,大致可分为单形和聚形,每种类型都具有不同的特性和应用。本文梳理了金刚石晶体的不同类型及应用。

2024-01-02 15:47:27 4907

4907 晶振中的抖动有哪两种主要类型? 晶振中的抖动主要分为相位抖动和频率抖动。 相位抖动是指晶振输出信号相位的随机波动。这种波动可能是由于晶体本身的不完美造成的,也可能是由于外部环境的干扰引起的。相位抖动

2024-01-25 13:51:07 1679

1679 时钟抖动(Clock Jitter)是时钟信号领域中的一个重要概念,它指的是时钟信号时间与理想事件时间的偏差。这种偏差不仅影响数字电路的时序性能,还可能对系统的稳定性和可靠性造成不利影响。以下是对时钟抖动工作原理的详细阐述,内容将围绕其定义、类型、产生原因、影响及应对措施等方面展开。

2024-08-19 17:58:11 5343

5343 在FPGA(现场可编程门阵列)设计中,消除时钟抖动是一个关键任务,因为时钟抖动会直接影响系统的时序性能、稳定性和可靠性。以下将详细阐述FPGA中消除时钟抖动的多种方法,这些方法涵盖了从硬件设计到软件优化的各个方面。

2024-08-19 17:58:54 3753

3753 时钟抖动和相位噪声是数字系统和通信系统中两个至关重要的概念,它们之间存在着紧密而复杂的关系。以下是对时钟抖动和相位噪声关系的详细探讨,旨在全面解析两者之间的相互作用和影响。

2024-08-19 18:01:57 2380

2380 时钟抖动(Jitter)和时钟偏移(Skew)是数字电路设计中两个重要的概念,它们对电路的时序性能和稳定性有着显著的影响。下面将从定义、原因、影响以及应对策略等方面详细阐述时钟抖动和时钟偏移的区别。

2024-08-19 18:11:30 3230

3230 。这种偏离可能导致数据传输错误,因此,理解和控制抖动对于保证通信系统的可靠性至关重要。 抖动通常分为两种类型:确定性抖动和随机抖动。确定性抖动是由多个因素引起的,包括码间干扰、串扰、占空失真以及周期性抖动等。这些抖动的

2024-09-10 10:42:18 1547

1547 引言:时钟抖动(jitter)是现代通信和数字系统中至关重要的性能指标之一,对数据传输速率和系统同步起着关键作用。本文将深入探讨时钟抖动的定义、不同类型,详细介绍各种抖动类型的测试方法,并分析时钟

2024-10-21 16:15:04 2420

2420

通过上一期我们了解到:数字电子产品中电源轨噪声和时钟抖动是有关联的,以及测量电源轨噪声的方案,接下来我们基于实际测量,揭示电源轨噪声对系统时钟抖动的影响。

2024-11-22 16:11:22 1176

1176

电子发烧友App

电子发烧友App

评论