作者:Narasimha Babu G V L、Udit Kumar 和 Anand Shirahatti

我们中许多主要从事数字验证和设计工作的人都不受物理层细节的影响。只有少数专家密切关注这些细节。因此,对于我们其他人来说,验证和调试扩频时钟(SSC)可能是一项艰巨的任务。

这篇博文是一个快速的问答,让您快速开始了解PCI Express(PCIe)扩频时钟(SSC)技术的一些复杂性。

在这里,您可以了解有关适用于第 4 代就绪 PCIe 和 PCIe 测试套件的 Synopsys VC 验证 IP 的更多信息。

什么是扩频时钟?为什么使用它?

扩频时钟是以受控方式对系统时钟进行抖动以降低峰值能量含量的过程。SSC技术用于最小化电磁干扰(EMI)和/或通过联邦通信委员会(FCC)的要求。

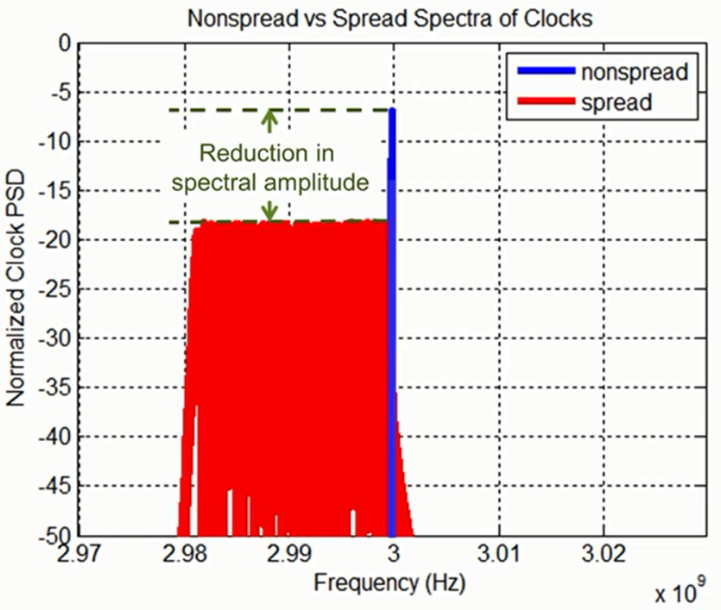

如果将时钟信号转换为频域,则会在时钟频率处发现高能量尖峰(下图3中1GHz处的非扩展蓝色尖峰)。扩频是一种将此尖峰分布在频带上以降低信号频率处的功率的方法(图1中的红色扩展)。

图 1:采用扩频时钟的 3GHz 时钟的频谱幅度降低

扩频时钟是如何实现的?

扩频时钟使用调制来实现频谱功率的扩展。载波信号通常是高频时钟信号,与低频调制器信号进行调制。虽然整体能量不变,但峰值功率降低。峰值能量色散量取决于调制带宽、扩频深度和扩频曲线。

由此产生的SSC调制载波信号最终的抖动比未调制载波信号高得多。

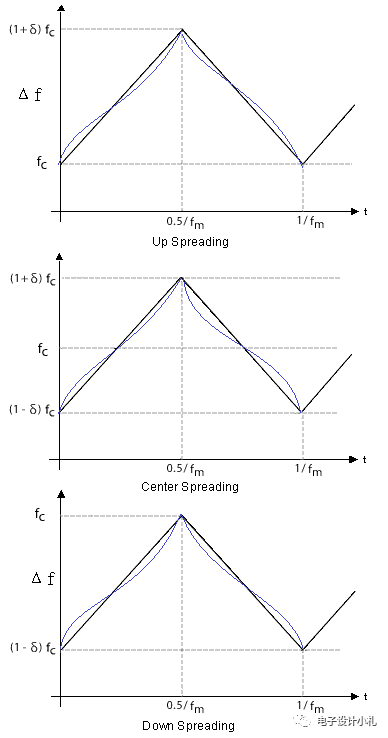

最常见的调制技术是下扩频和中心扩频:

下扩频:载波按指定的百分比调制至低于标称频率,而不是更高

中心扩展:载波按指定百分比调制高于和低于标称频率

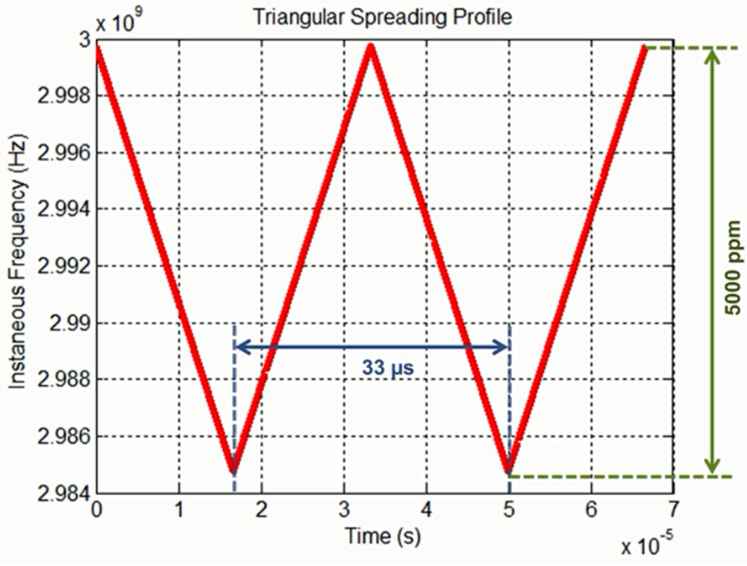

下面的图2显示了一个3Ghz载波时钟信号,使用0KHz三角波时下行扩展5.30%。在Y轴上,您可以看到载波频率的上升和下降。所有扩频载波频率值仍低于 3 GHz。

图 2:3GHZ 载波信号频率变化,下行扩展 SSC 时钟为 0.5%

PCIe 支持哪些不同的时钟架构?它们都支持 SSC 吗?

PCIe 支持三种不同类型的时钟架构:

公共参考时钟(公共参考时钟)

数据时钟

单独的参考时钟(单独的参考时钟)

通用 Refclk 是商用设备中支持最广泛的架构。但是,必须将相同的时钟源分配给每个 PCIe 设备,同时将设备之间的时钟到时钟偏斜保持在 12 ns 以下。这可能是大型电路板的问题,或者将背板连接器交叉到另一个电路板时。

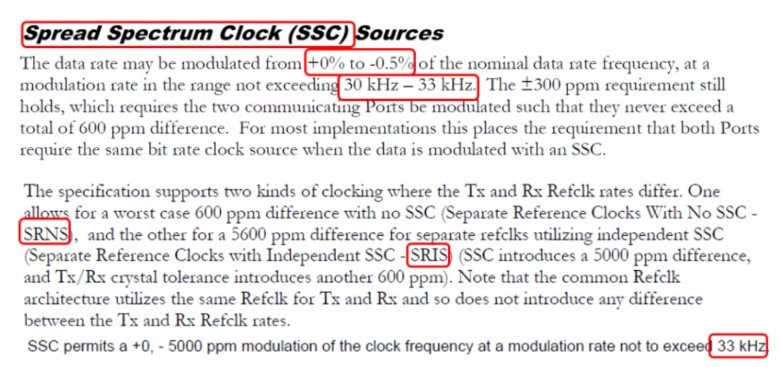

如果低偏斜配置不可行,例如在长电缆实现中,则可以使用两端具有独立时钟的独立 Refclk 架构。但是 Gen 2.0 基本规范不允许在单独的 Refclk 实现上使用 SSC。它仅在 2013 年通过 ECN:独立的 Refclk 独立 SSC (SRIS) 架构启用,该架构成为 3 年 1 月发布的 2013.<> 基本规范的一部分。

数据时钟 Refclk 架构是最简单的,因为它只需要一个时钟源,位于发射器上。接收器提取并同步到嵌入在传输数据中的时钟。数据时钟架构是在 2 年发布 PCIe 0.2007 标准时引入的。

您可以在此处了解有关时钟架构的更多信息。

要了解有关SRIS的更多信息,以下是Synopsys研究员John Stonick的另一个富有洞察力的短视频。

SSC 是否在所有速度下都受支持?

是的。所有四种速度 2.5 GT/s(第 1 代)、5 GT/s(第 2 代)、8 GT/s(第 3 代)和 16 GT/s(第 4 代)均可支持 SSC。相同的扩频时钟参数适用于所有四种速度。

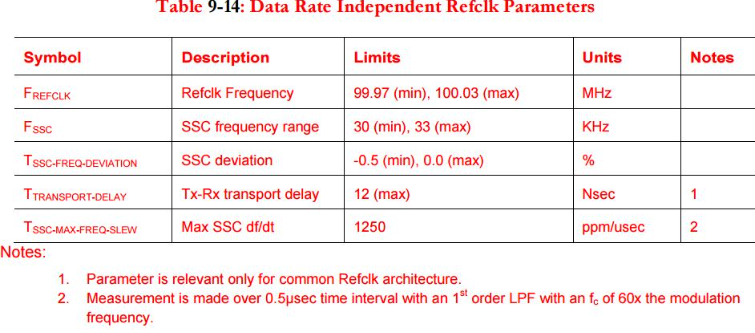

图 3:第 4 代 PCIe 基本规范中的 Refclk 参数快照(来源:PCI-SIG)

上表中我们需要注意的一些关键参数:

FREFCLK:参考频率可以有 +/-300 PPM 的变化。对于单独时钟架构,接收器必须容忍600 PPM的最坏情况抖动。

FSSC:这是调制波的频率。这通常是三角形的。

TSS-FREQ-DEVIATION: 这表示 PCIe 使用向下传播的 SSC。应用此点差可将携带频率降低 -0.5%。这意味着额外的 5000 PPM 抖动。因此,启用扩频的独立时钟的总抖动将为5600 PPM。

扩频时钟的验证提供的价值是多少?

从被测设计(DUT)的角度来看,主要价值在于验证接收器的时钟数据恢复建模,以处理抖动的巨大变化(高达5600 ppm),尤其是在SRIS模式下。

如何目视验证 SSC 是否真的发生?

有多种方法。最简单的方法是,您可以将“时钟周期信号”可视化,通常是浮点数据类型(SystemVerilog 中的实际类型),如果它可以在波形查看器中作为模拟信号访问。

如果无法访问,则通过简单的监视器收集以线速运行的Refclk或内部生成的传输位时钟的时间戳和周期,假设您使用33Khz调制,则至少为30us。在 X 轴上绘制时间戳,在 Y 轴上绘制时钟的持续时间。您应该能够看到与图 2 中所示的配置文件匹配的配置文件。

为了成功验证扩频时钟,您使用的 PCIe 验证 IP 需要支持 SSC。它应该为您提供以不同速度打开或关闭扩频的可编程性。此外,它还应支持规范定义的SSC配置文件,用于0.5%的下行传播。它还应该允许在30Khz(最小)和33Khz(最大)范围内的调制信号频率方面进行编程。Synopsys PCIe VIP 加载了所有这些功能以及更多功能。

审核编辑:郭婷

-

emi

+关注

关注

54文章

3864浏览量

134061 -

扩频时钟

+关注

关注

0文章

11浏览量

10842 -

ssc

+关注

关注

0文章

26浏览量

11753

发布评论请先 登录

扩频时钟技术分享:SSC技术是什么、SSC对测试高速总线信号的影响

FPGA算法工程师、逻辑工程师、原型验证工程师有什么区别?

如何进行PCI-Express的一致性测试和分析

招聘数字ic设计工程师/数字集成电路工程师/DFT负责人/高级DFT工程师

芯片验证工程师 杭州国芯科技

诚招“FPGA工程师、嵌入式系统开发工程师”

用于FPGA的xilinx gtx phy是否支持SSC时钟?

【华为海思成都】招聘数字IC设计/验证工程师

FPGA工程师需要具备哪些技能?

LMK3H0102 参考无源2差分或5单端输出PCIe Gen 1-7兼容可编程BAW时钟发生器总结

面向验证工程师的PCIe扩频时钟(SSC)

面向验证工程师的PCIe扩频时钟(SSC)

评论