本文介时钟频率概念及其对系统性能的影响,并在电路板级、芯片级和单元模块级分别提供了减小相位噪声和抖动的有效方法。

2012-03-10 09:55:23 5225

5225

本文介绍了如何准确地估算采样时钟抖动,以及如何计算正确的上下整合边界。

2012-04-01 10:19:38 2333

2333

为了正确理解时钟相关器件的抖动指标规格,同时选择抖动性能适合系统应用的时钟解决方案,本文详细介绍了如何理解两种类型时钟驱动器的抖动参数,以及从锁相环输出噪声特性理解时钟器件作为合成器、抖动滤除功能时的噪声特性。

2013-06-21 15:40:41 19925

19925

时钟抖动是相对于理想时钟沿实际时钟存在不随时间积累的、时而超前、时而滞后的偏移称为时钟抖动,简称抖动

2023-11-08 15:08:01 3278

3278

当DAQ信号链被隔离之后,控制采样保持开关的信号一般来自进行多通道同步采样的背板。系统设计人员选择低抖动数字隔离器至关重要,以使进入ADC的采样保持开关的控制信号具有低抖动。

2022-03-16 11:53:34 3322

3322

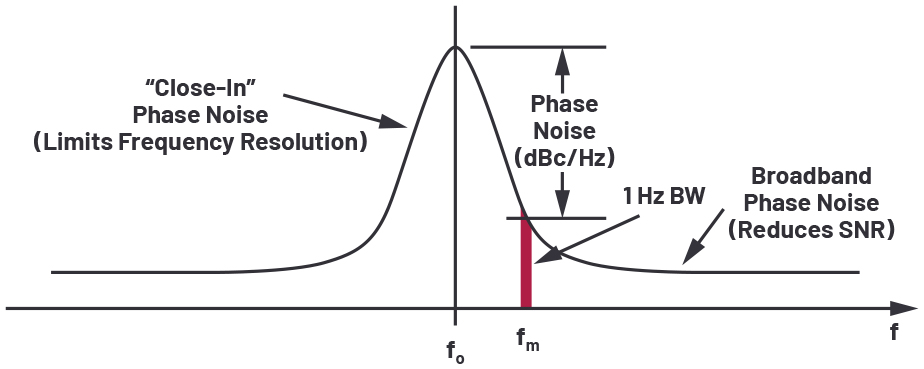

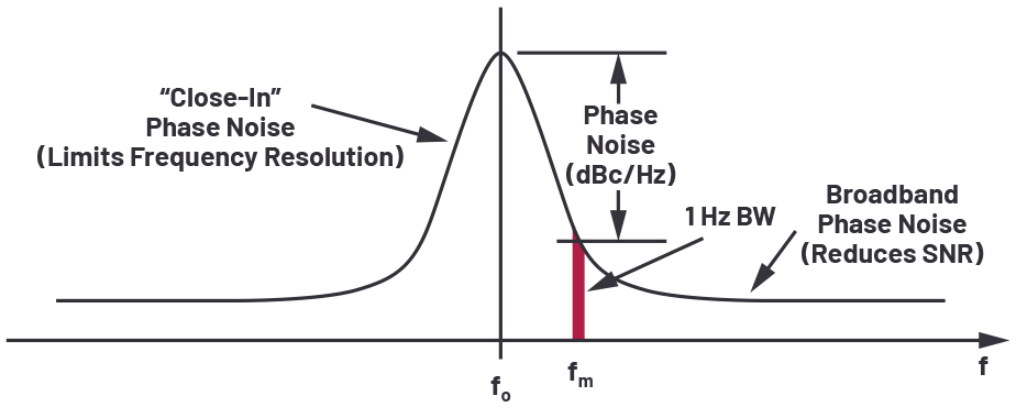

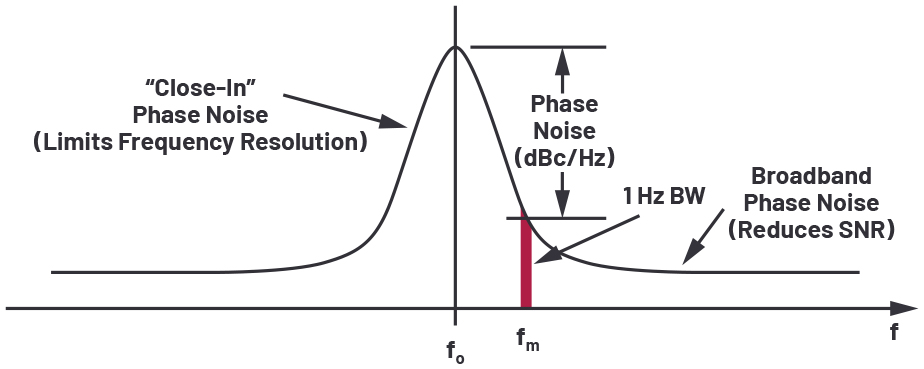

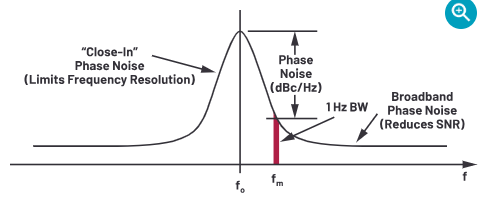

时钟频率的不断提高使相位噪声和抖动在系统时序上占据日益重要的位置。本文介其概念及其对系统性能的影响,并在电路板级、芯片级和单元模块级分别提供了减小相位噪声和抖动的有效方法。

2019-06-05 07:13:30

对高速信号进行高分辨率的数字化处理需审慎选择时钟,才不至于使其影响模数转换器(ADC)的性能。那么时钟抖动会对高速ADC的性能有什么影响呢?

2021-04-08 06:00:04

图1强调了噪声源而不是固有抖动会引起定时抖动错误。更快的边沿速率减少了时钟信号上的电压噪声对时钟抖动性能的影响。这种现象并非是仅属于时钟信号的特点。在接收时钟信号或测量抖动性能的设备内,这种机理也表现得很明显。…

2022-11-23 07:59:49

作者:John Johnson,德州仪器 本文介绍时钟抖动对高速链路性能的影响。我们将重点介绍抖动预算基础。 用于在更远距离对日益增长的海量数据进行传输的一些标准不断出现。来自各行业的工程师们组成

2018-09-19 14:23:47

本文介绍时钟抖动对高速链路性能的影响。我们将重点介绍抖动预算基础。 用于在更远距离对日益增长的海量数据进行传输的一些标准不断出现。来自各行业的工程师们组成了各种委员会和标准机构,根据其开发标准的目标

2022-11-23 06:59:24

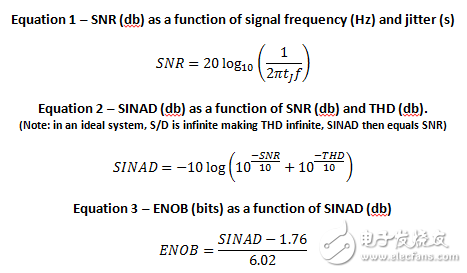

很多人都知道,抖动(这是时钟边沿不确定性)是不好的现象,其不仅可导致噪声增加,而且还会降低数据转换器的有效位数 (ENOB)。例如,如果系统需要 100MHz 14(最小值)位的 ENOB,我们

2022-11-21 07:26:27

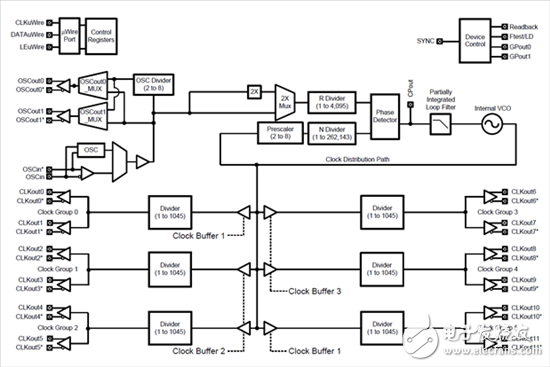

上升沿。图1 —LMK03806(具有时钟发生器、时钟分频器和驱动器)的方框图因此,您下次设计采样系统时,别忘了考虑时钟抖动性能,因为这会影响整体动态范围。其它资源:阅读我们的最新博客系列《定时决定一切

2018-09-13 14:18:06

最近做了一块INA226的采样板,在使用它采样系统电流的时候,出现采样电流随系统电压变化的情况。例如系统电压为15V,恒流300mA 采样得到电流为210mA,系统电压为5V,依然恒流300mA

2024-12-09 08:17:18

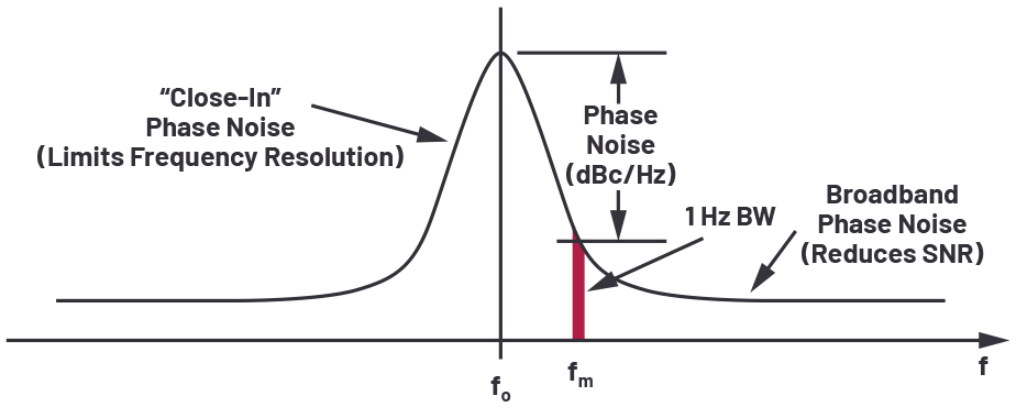

采样时钟考量在高性能采样数据系统中,应使用低相位噪声晶体振荡器产生ADC(或DAC)采样时钟,因为采样时钟抖动会调制模拟输入/输出信号,并提高噪声和失真底。采样时钟发生器应与高噪声数字电路隔离

2014-11-20 10:58:30

基于FPGA多通道采样系统设计资料

2012-08-20 11:43:23

基于STC89C52,adc0832,7279的多路数据采样系统设计汇编程序

2016-06-20 12:31:14

奈奎斯特准则对数据采样系统设计

2016-01-05 13:05:35

3GHz以上的系统中,时间抖动(jitter)会导致码间干扰(ISI),造成传输误码率上升。在此趋势下,高速数字设备的设计师们也开始更多地关注时序因素。在数字音频信号中,随着系统时钟频率的不断提高,时间抖动

2016-09-28 16:08:05

采样时钟抖动对ADC信噪比的性能有什么影响?如何实现低抖动采样时钟电路的设计?

2021-04-14 06:49:20

如何设计并实现一种高性能中频采样系统?中频采样系统系统总体设计由哪些组成?它们分别有什么作用?

2021-04-07 07:09:32

需要使用滤波器,根据系统的特性选择什么滤波器,这样的滤波器如何使用代码实现,以及实现后可能会有什么样的性能提升?”这样“一条龙”的ADC滤波设计方法。2.高精度、中低速采样系统的实际设计过程中,讨论

2016-10-14 23:08:55

摘要:在数据采样系统中,高于二分之一采样率的频率成分“混叠”(搬移)到有用频带。大多数时间,混叠是有害的副作用,所以在模/数(AD)转换级之前,将“欠采样”的较高频率简单滤除。但有时候,特意设计利

2019-07-30 06:11:02

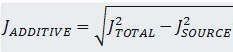

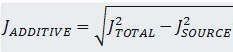

需求。作为该最新博客系列的开篇文章,我将帮助您了解如何正确测量时钟缓冲器的附加抖动。为什么抖动很重要?在当今数据通信、有线及无线基础设施以及其它高速应用等高级系统中,时钟抖动是整体系统性能的关键因素。要

2018-09-13 14:38:43

在我的应用程序中,HSPDM 触发 EVADC 同时对两个通道进行采样。

我应该如何配置 EVADC 以最大限度地减少采样抖动并最大限度地提高采样率?

在用户手册中,它提到 SSE=0,USC=0

2024-01-18 07:59:23

设计一个基于单片机的水质采样系统,可以定时对不同深度的水层进行采样。单片机的选型和使用;水泵的选型和使用;相关传感器的选型和使用;相关系统的集成;还需考虑制作安装成本问题。推荐课程:张飞软硬开源

2019-03-20 12:37:42

设计采样系统时,关于时钟抖动性能如何考虑?抖动对时钟采样系统有何影响?

2021-04-06 06:07:38

AD9444的功能和特性是什么?基于AD9444的时间交叉采样系统怎样去设计?设计时间交叉采样系统有哪些注意事项?

2021-04-23 07:07:29

,你可以实现更高的性能—最多比传统SAW示波器高9倍。 图1:SAW示波器和TI LMK03328的10G链路性能一个低相位噪声基准时钟转化为串行链路中其它关键块的更高抖动允许量分配。随着数据速率快速

2018-09-05 16:07:30

3GHz以上的系统中,时间抖动(jitter)会导致码间干扰(ISI),造成传输误码率上升。在此趋势下,高速数字设备的设计师们也开始更多地关注时序因素。在数字音频信号中,随着系统时钟频率的不断提高,时间抖动

2016-09-28 16:28:28

本文利用TMS320C5402 的高速计算功能,设计了一种新的交流采样系统,该系统利用小波变换的优越特性对采集到的电压和电流信号进行处理,克服了原来在计算无功功率过程中由于

2009-09-08 14:45:50 22

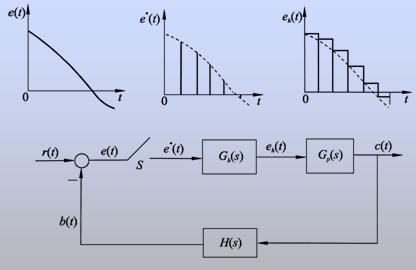

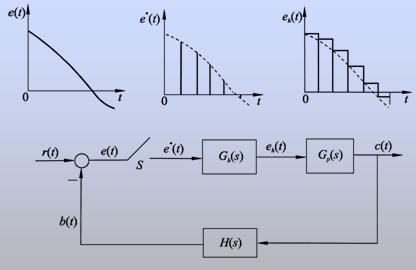

22 采样控制系统与连续控制系统的根本区别在于采样系统中既包含有连续信号,又包含有离散信号,是一个混和信号系统。分析和设计采样系统的数学工具是Z变换,采用

2009-11-24 09:35:31 0

0 本文主要讨论采样时钟抖动对ADC 信噪比性能的影响以及低抖动采样时钟电路的设计。

2009-11-27 11:24:07 15

15 本文分析了晶振的漂移对GPS 接收机的影响,从锁相环理论的角度,重点分析了采样时钟抖动对基带载波跟踪和伪码跟踪性能的影响,并给出一种环路分级降带宽的方法来消除这种

2009-12-19 13:49:58 19

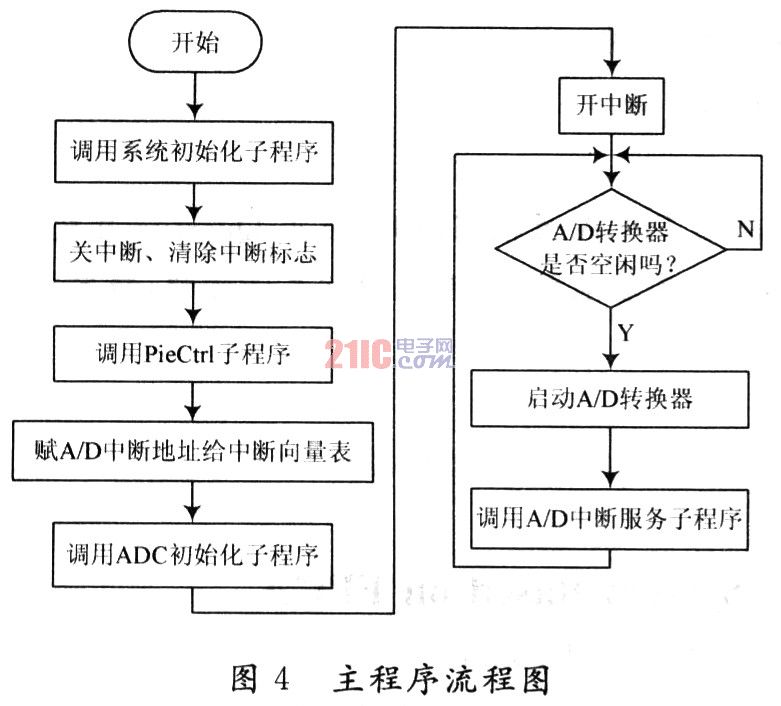

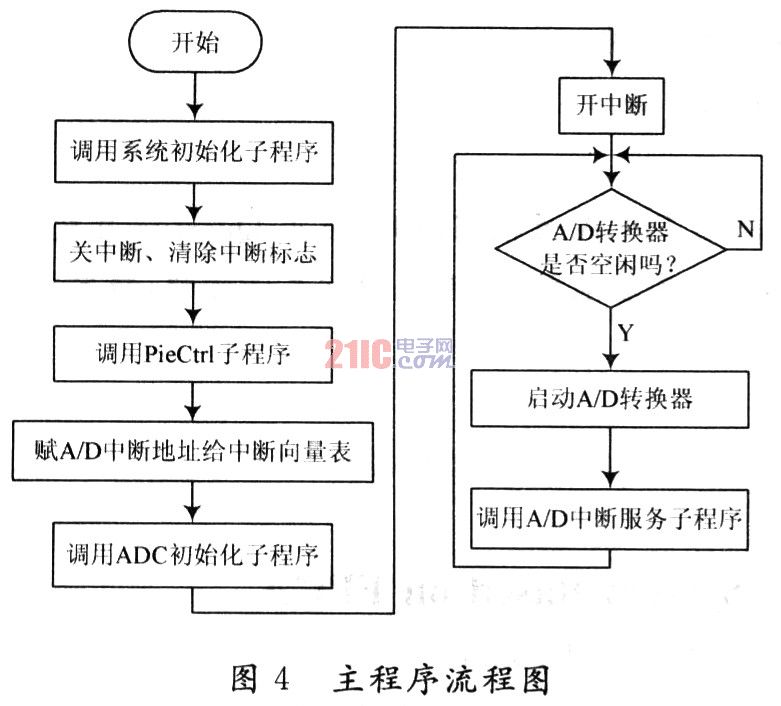

19 本文详细介绍了基于TMS320F2812的电流采样系统的设计方法。根据直流电流信号产生特点和采集技术的基本要求,选用合适的电流传感器LTS25-NP,设计电压变换电路,采用TMS320F2812型DSP

2010-07-27 16:50:08 66

66 随着支持直接IF采样的更高分辨率数据转换器的上市,系统设计师在选择低抖动时钟电路时,需要在性能/成本之间做出权衡取舍。许多用于标定时钟抖动的传统方法都不适用于数

2010-11-27 17:12:46 33

33

为提高中频采样系统性能,降低板级噪声,加大采样频率的灵活性,设计并实现一种高性能中频采样系统。该系统利用AD9518-4实现可配置的采样时钟,根据不同的采样要

2010-12-07 13:40:23 22

22 采样系统典型结构图

2009-01-08 14:19:46 1737

1737

USB接口技术在外置式采样系统中的应用

一、前言:

---- 中高速、高精度连续采样系统由

2009-02-08 10:47:06 855

855

理解不同类型的时钟抖动

抖动定义为信号距离其理想位置的偏离。本文将重点研究时钟抖动,并探讨下面几种类型的时钟抖动:相邻周期抖动、周期抖动、时间间隔误

2010-01-06 11:48:11 2094

2094

利用TMS320F2812变频电源的交流采样系统设计方案

概述:本文介绍利用HCNR200及TMS320F2812内置ADC采集交流电压和负载电流信号的系统设计。HCNR200是一款

2010-03-22 14:36:44 2415

2415

基于DDS的时钟抖动性能与DAC重构滤波器性能的关系

2011-11-25 00:01:00 36

36 如果明智地选择时钟,一份简单的抖动规范几乎是不够的。而重要的是,你要知道时钟噪声的带宽和频谱形状,才能在采样过程中适当地将它们考虑进去。很多系统设计师对数据转换器

2012-05-08 15:29:00 47

47 200MHz实时采样系统的设计与实现,下来看看。

2016-02-19 16:39:58 0

0 基于FPGA多通道采样系统设计资料,有兴趣的同学可以下载学习

2016-04-28 14:29:56 48

48 宽带雷达信号的低杂散采样系统研究_王龙

2017-01-08 10:47:21 0

0 基于FPGA的高速多通道AD采样系统的设计与实现_徐加彦

2017-01-18 20:23:58 12

12 基于TMS320F2812变频电源的交流采样系统设计_王荣海

2017-03-19 11:46:35 7

7 的系统设计,如在某些情况下系统性能极限由系统决定时序裕量。所以对时序抖动有很好的了解在系统设计中变得非常重要。总抖动可以随机抖动和确定性抖动分离组件。我们将不讨论抖动的组件本申请说明。我们将专注于不同类型的时钟

2017-04-01 16:13:18 6

6 了解高速ADC时钟抖动的影响将高速信号数字化到高分辨率要求仔细选择一个时钟,不会妥协模数转换器的采样性能(ADC)。 在这篇文章中,我们希望给读者一个更好的了解时钟抖动及其影响高速模数转换器的性能

2017-05-15 15:20:59 13

13 级,从而降低成本和功耗。在欠采样接收机设计中必须要特别注意采样时钟,因为在一些高输入频率下时钟抖动会成为限制信噪比(SNR) 的主要原因。 本系列文章共有三部分,第1 部分重点介绍如何准确地估算某个时钟源的抖动,以及如何将其与AD

2017-05-18 09:47:38 1

1 本文分析了晶振的漂移对 GPS 接收机的影响,从锁相环理论的角度,重点分析了采样时钟抖动对基带载波跟踪和伪码跟踪性能的影响,并给出一种环路分级降带宽的方法来消除这种影响。该方法在保证最终伪码跟踪精度

2017-11-27 14:45:05 12

12 本文主要讨论采样时钟抖动对 ADC 信噪比性能的影响以及低抖动采样时钟电路的设计。 ADC 是现代数字解调器和软件无线电接收机中连接模拟信号处理部分和数字信号处理部分的桥梁,其性能在很大程度上决定了

2017-11-27 14:59:20 18

18 时域采样理论与频域采样理论是数字信号处理中的重要理论,本文首先简单介绍信号处理过程中时域采样和频域采样的原理,接着基于NI LabVIEW 2015平台,设计开发了采样定理验证系统,在时域采样系统中

2018-04-09 10:49:04 14

14 仔细观察某个采样点,可以看到计时不准(时钟抖动或时钟相位噪声)是如何形成振幅变化的。由于高 Nyquist 区域(例如,f1 = 10 MHz 到 f2 = 110 MHz)欠采样带来输入频率的增加,固定数量的时钟抖动自理想采样点产生更大数量的振幅偏差(噪声)。

2018-05-14 08:51:40 3

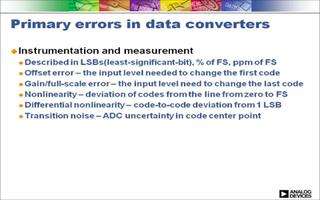

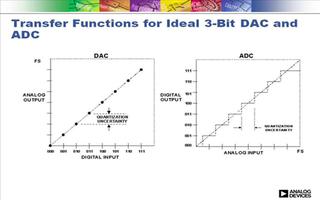

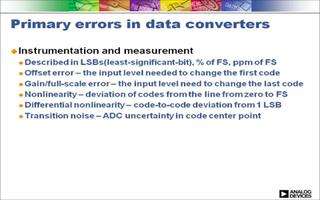

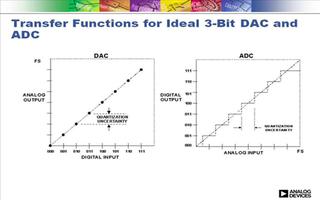

3 ADI公司推出三集系列在线研讨会来关注模拟电气信号到数字信号的转换,以便通过DSP、微控制器或其它嵌入式处理器来分析和处理,本研讨会是第一集。但在使用数据转换器之前,我们需要先了解数据采样系统的基础知识:单极性和双极性代码、传递函数、奈奎斯特原理、滤波器等等。

2018-05-24 14:50:00 5301

5301

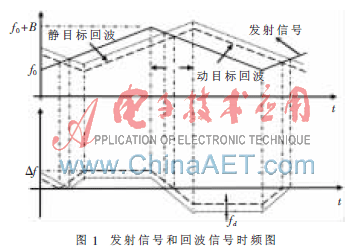

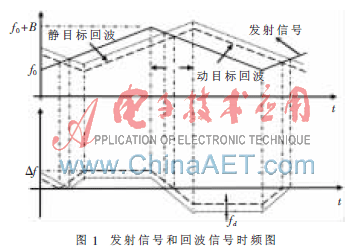

针对线性调频连续波汽车防撞雷达回波信号的特点,选用串行差分ADC,设计了一种基于DSP的SPORT口的I、Q双通道采样系统,并通过实验验证了系统的正确性。

2018-12-19 11:49:49 1528

1528

ADI研讨会:高性能时钟: 解密抖动

2019-08-20 06:05:00 2532

2532 ADI公司推出三集系列在线研讨会来关注模拟电气信号到数字信号的转换,以便通过DSP、微控制器或其它嵌入式处理器来分析和处理,本研讨会是第一集。但在使用数据转换器之前,我们需要先了解数据采样系统的基础知识:单极性和双极性代码、传递函数、奈奎斯特原理、滤波器等等。

2019-06-10 06:01:00 3857

3857

时钟抖动性能主题似乎是时钟,ADC和电源的当前焦点供应厂家。理由很清楚;时钟抖动会干扰包括高速ADC在内的数字电路的性能。高速时钟可以对它们所接收的功率的“清洁度”非常敏感,尽管量化关系需要一些努力。

2019-09-14 11:24:00 9399

9399

本文针对全方位的信号路径系统中的高速全差分运放及高频宽14位模拟/数字转换器的随机及固定时钟抖动,具体分析、研究了超低噪声兼时钟抖动滤除技术。研究选用双级联PLLatinum架构,配置高性能压控振荡器(VCXO),很好地实现了降噪和时钟抖动滤除的作用。

2020-09-23 10:45:00 2

2 ADC是现代数字解调器和软件无线电接收机中连接模拟信号处理部分和数字信号处理部分的桥梁,其性能在很大程度上决定了接收机的整体性能。在A/D转换过程中引入的噪声来源较多,主要包括热噪声、ADC电源的纹波、参考电平的纹波、采样时钟抖动引起的相位噪声以及量化错误引起的噪声等。

2020-07-24 11:02:57 1559

1559

和高性能的优势,高性能设计中使用了高速串行总线。使用串行数据连接将数据从系统中的一个点传输到另一点。时钟和数据恢复电路用于将系统中的数据从发送方准确地发送到接收方。 在接收侧对数据的准确解释主要取决于具有

2021-02-20 14:20:50 9052

9052

AN-1221: 使用ADF4002 PLL产生高速模数转换器所需的极低抖动编码(采样)时钟

2021-03-19 08:59:00 13

13 MT-002: 奈奎斯特准则对数据采样系统设计有何意义

2021-03-20 10:16:34 5

5 前言 :本文我们介绍下ADC采样时钟的抖动(Jitter)参数对ADC采样的影响,主要介绍以下内容: 时钟抖动的构成 时钟抖动对ADC SNR的影响 如何计算时钟抖动 如何优化时钟抖动 1.采样理论

2021-04-07 16:43:45 10607

10607

AN-1576:采用AD9958 500 MSPS DDS或AD9858 1 GSPS DDS和AD9515时钟分配IC的高性能ADC的低抖动采样时钟发生器

2021-04-30 09:48:42 14

14 为解决对非线性采样系统的状态空间 Hammerstein模型难以辨识的问题,提岀了基于组合信号源的辨识方法。首先用组合信号源将静态非线性环节和动态线性环节分离。其次,采用模糊神经模型拟合静态非线性

2021-05-31 14:32:54 12

12 作者: Richard Zarr

如果您在通信行业工作,那么您可能很熟悉抖动对系统性能的影响。抖动不仅会降低数据转换器的性能,而且还可在高速数字系统中产生误码。凭直觉判断,给时钟增加噪声会增大系统

2021-11-23 17:45:07 2967

2967

PCIe 和网络时钟抖动测量之间的另一个显着差异在图 2 中并不明显。数字采样示波器 (DSO) 用于获取时钟周期或波形文件以计算 PCIe 时钟抖动,而不是 PNA。造成这种情况的主要原因是 PCIe 时钟支持扩频,而网络时钟不支持,而且从历史上看,PNA 一直无法使用正在扩频的时钟。

2022-05-05 15:50:44 7109

7109

AC 和 DC 精度,而无需牺牲 DC 精度以获得更高的采样率。然而,为了实现高 AC 性能,例如信噪比 (SNR),系统设计人员需要考虑采样时钟信号或控制采样和转换的转换启动信号上的抖动引入的误差。在

2022-07-19 16:37:37 2699

2699

超低抖动时钟发生器如何优化串行链路系统性能

2022-11-04 09:50:15 0

0 时钟采样系统最大限度减少抖动

2022-11-04 09:52:12 0

0 时钟抖动使随机抖动和相位噪声不再神秘

2022-11-07 08:07:29 4

4 时钟抖动解秘—高速链路时钟抖动规范基础知识

2022-11-07 08:07:30 2

2 精度,无需牺牲直流精度来换取更高的采样速率。然而,为实现高交流性能,如信噪比(SNR),系统设计人员必须考虑采样时钟信号或控制ADC中采样保持(SH)开关的转换启动信号上的抖动所带来的误差。随着目标信号和采样速率的增加,控制采样保持开

2022-11-13 11:25:11 1481

1481 抖动和相位噪声是晶振的非常重要指标,本文主要从抖动和相位噪声定义及原理出发,阐述其在不同场景下对数字系统、高速串行接口、数据转换器和射频系统的影响。 1. 抖动和相位噪声 1.1. 抖动

2023-03-10 14:54:32 1847

1847

先来聊一聊什么是时钟抖动。时钟抖动实际上是相比于理想时钟的时钟边沿位置,实际时钟的时钟边沿的偏差,偏差越大,抖动越大。实际上,时钟源例如PLL是无法产生一个绝对干净的时钟。这就意味着时钟边沿出现在

2023-06-09 09:40:50 3109

3109

精度,无需牺牲直流精度来换取更高的采样速率。然而,为实现高交流性能,如信噪比(SNR),系统设计人员必须考虑采样时钟信号或控制ADC中采样保持(S&H)开关的转换启动信号上的抖动所带来的误差。随着目标信号和采样速率的增加,控制采样保持开关的信号抖动会成为主要误差源。

2023-06-15 16:30:12 1393

1393

本文主要介绍了时钟偏差和时钟抖动。

2023-07-04 14:38:28 3231

3231

电子发烧友网站提供《高性能中频采样系统的设计与实现.pdf》资料免费下载

2023-10-18 09:57:34 0

0 电子发烧友网站提供《时钟抖动对ADC性能有什么影响.pdf》资料免费下载

2023-11-28 10:24:10 1

1 ,通常低于 100 飞秒 (fs),以保持系统性能。这些时钟还必须长期保持低抖动规格,且不受温度和电压的影响。 某些抖动是由信号路径噪声和失真引起的,使用重复时钟和重定时技术可以在一定程度上减少抖动。不过,抖动也是由时钟源产生的,时钟源通常是振荡器。这是由于各

2024-02-13 17:47:00 2102

2102

时钟抖动(Clock Jitter)是时钟信号领域中的一个重要概念,它指的是时钟信号时间与理想事件时间的偏差。这种偏差不仅影响数字电路的时序性能,还可能对系统的稳定性和可靠性造成不利影响。以下是对时钟抖动工作原理的详细阐述,内容将围绕其定义、类型、产生原因、影响及应对措施等方面展开。

2024-08-19 17:58:11 5343

5343 在FPGA(现场可编程门阵列)设计中,消除时钟抖动是一个关键任务,因为时钟抖动会直接影响系统的时序性能、稳定性和可靠性。以下将详细阐述FPGA中消除时钟抖动的多种方法,这些方法涵盖了从硬件设计到软件优化的各个方面。

2024-08-19 17:58:54 3755

3755 时钟抖动(Jitter)和时钟偏移(Skew)是数字电路设计中两个重要的概念,它们对电路的时序性能和稳定性有着显著的影响。下面将从定义、原因、影响以及应对策略等方面详细阐述时钟抖动和时钟偏移的区别。

2024-08-19 18:11:30 3230

3230 电子发烧友网站提供《同步采样系统中的 ADS127L11应用说明.pdf》资料免费下载

2024-09-10 10:28:17 5

5 通过上一期我们了解到:数字电子产品中电源轨噪声和时钟抖动是有关联的,以及测量电源轨噪声的方案,接下来我们基于实际测量,揭示电源轨噪声对系统时钟抖动的影响。

2024-11-22 16:11:22 1176

1176

电子发烧友App

电子发烧友App

评论