AD783要求一个宽度为150 ns至250 ns的窄正采样脉冲。为使显示的波形保持稳定,无来回跳动,采样脉冲必须非常稳定,抖动很低。这一要求往往将可能的时钟选择限定于晶体振荡器。另一个

2012-04-18 11:54:39 5607

5607

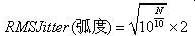

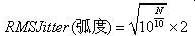

本系列文章共有三部分,第 1 部分重点介绍如何准确地估算某个时钟源的抖动,以及如何将其与 ADC 的孔径抖动组合。在第 2 部分中,该组合 抖动 将用于计算 ADC 的 SRN,然后将其与实际

2012-05-07 11:37:30 2668

2668

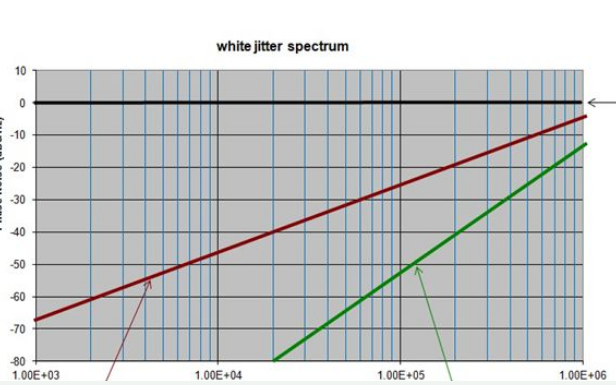

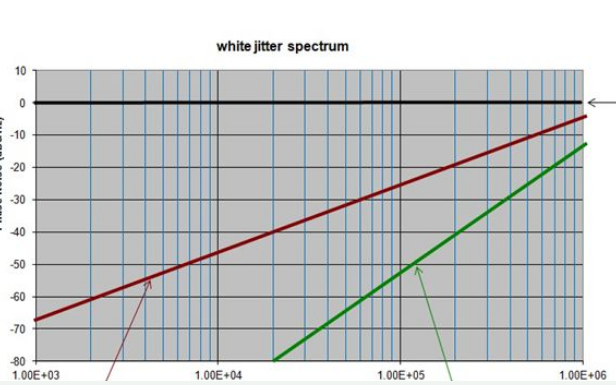

为了正确理解时钟相关器件的抖动指标规格,同时选择抖动性能适合系统应用的时钟解决方案,本文详细介绍了如何理解两种类型时钟驱动器的抖动参数,以及从锁相环输出噪声特性理解时钟器件作为合成器、抖动滤除功能时的噪声特性。

2013-06-21 15:40:41 14342

14342

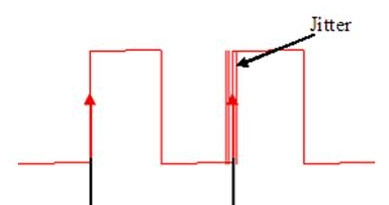

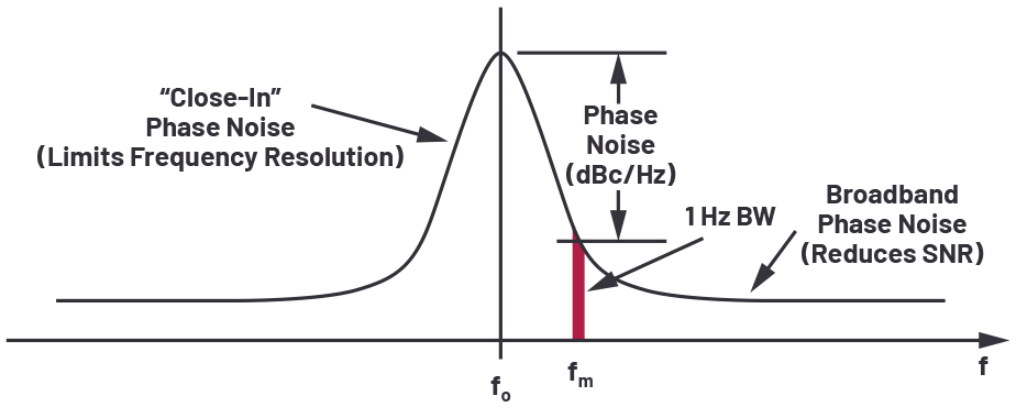

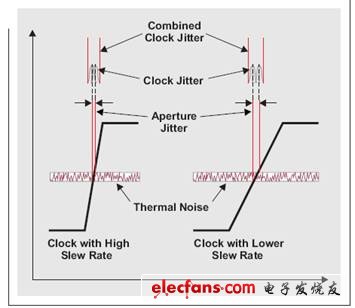

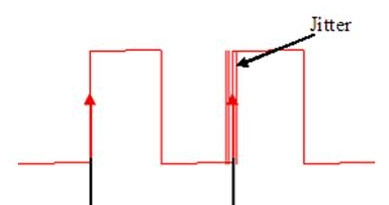

抖动一般定义为信号在某特定时刻相对于其理想位置的短期偏移。这个短期偏移在时域的表现形式为抖动(下文的抖动专指时域抖动),在频域的表现形式为相噪。本文主要探讨下时钟抖动和相噪以及其测量方法,以及两者之间的关系。

2016-01-18 10:54:11 24276

24276

-Si539x时钟提升频率灵活性和抖动性能--Si56x Ultra Series™ XO/VCXO提供最大可达3GHz的任意频率时钟-。

2018-06-26 15:19:41 7075

7075 时钟抖动技术适合于各种周期性的脉冲信号,典型的是电力电子设备中的PWM电压和数字电路中的时钟信号。

2023-09-11 10:55:34 503

503

时钟抖动是相对于理想时钟沿实际时钟存在不随时间积累的、时而超前、时而滞后的偏移称为时钟抖动,简称抖动

2023-11-08 15:08:01 892

892

当DAQ信号链被隔离之后,控制采样保持开关的信号一般来自进行多通道同步采样的背板。系统设计人员选择低抖动数字隔离器至关重要,以使进入ADC的采样保持开关的控制信号具有低抖动。

2022-03-16 11:53:34 2696

2696

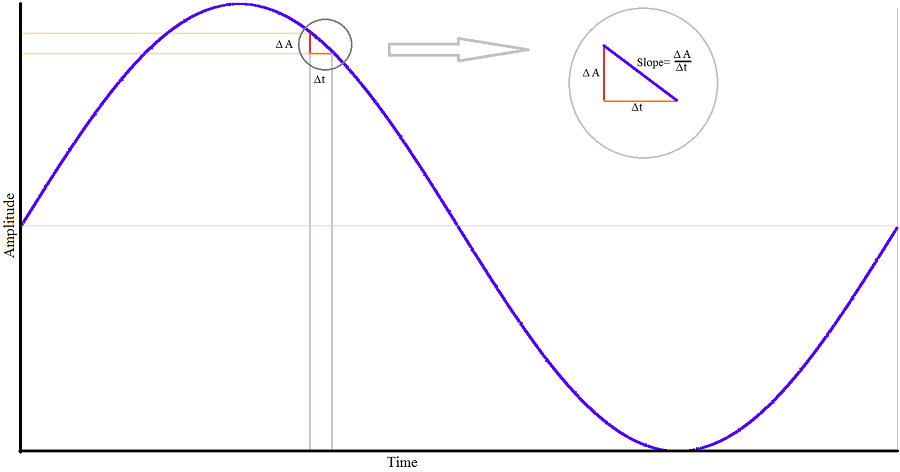

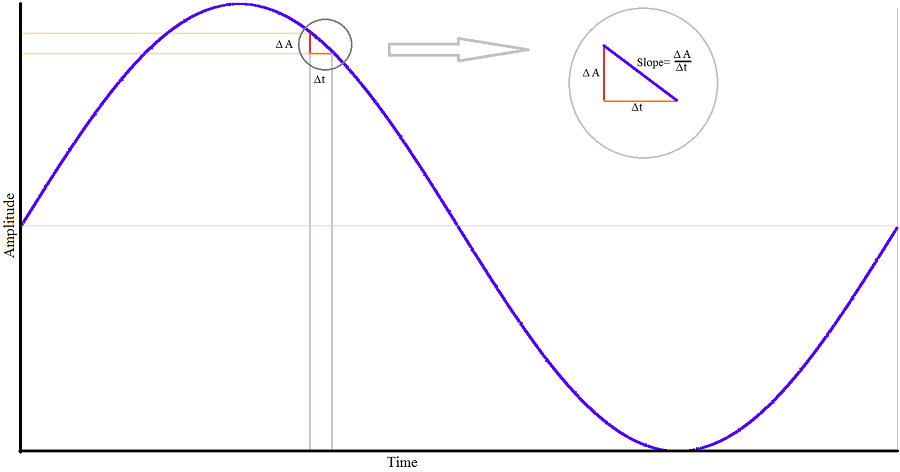

在本文中,我们将讨论抖动传递及其性能,以及相位噪声测量技术的局限性。 时钟抖动和边沿速率 图1显示了由一个通用公式表述的三种波形。该公式包括相位噪声项“φ(t)”和幅度噪声项“λ(t)。对评估的三个

2022-11-23 07:59:49

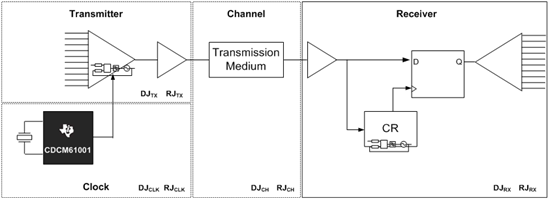

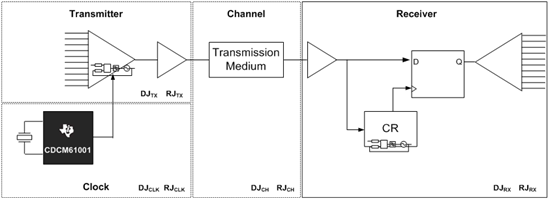

作者:John Johnson,德州仪器 本文介绍时钟抖动对高速链路性能的影响。我们将重点介绍抖动预算基础。 用于在更远距离对日益增长的海量数据进行传输的一些标准不断出现。来自各行业的工程师们组成

2018-09-19 14:23:47

本文介绍时钟抖动对高速链路性能的影响。我们将重点介绍抖动预算基础。 用于在更远距离对日益增长的海量数据进行传输的一些标准不断出现。来自各行业的工程师们组成了各种委员会和标准机构,根据其开发标准的目标

2022-11-23 06:59:24

转时钟抖动的理解

2016-10-05 12:08:25

很多人都知道,抖动(这是时钟边沿不确定性)是不好的现象,其不仅可导致噪声增加,而且还会降低数据转换器的有效位数 (ENOB)。例如,如果系统需要 100MHz 14(最小值)位的 ENOB,我们

2022-11-21 07:26:27

上升沿。图1 —LMK03806(具有时钟发生器、时钟分频器和驱动器)的方框图因此,您下次设计采样系统时,别忘了考虑时钟抖动性能,因为这会影响整体动态范围。其它资源:阅读我们的最新博客系列《定时决定一切

2018-09-13 14:18:06

采样时钟考量在高性能采样数据系统中,应使用低相位噪声晶体振荡器产生ADC(或DAC)采样时钟,因为采样时钟抖动会调制模拟输入/输出信号,并提高噪声和失真底。采样时钟发生器应与高噪声数字电路隔离

2014-11-20 10:58:30

DN1013- 了解时钟抖动对高速ADC的影响

2019-07-17 06:41:39

变形。在图5中,您可以看到时钟信号电平的切换距离是不均匀的;这就是时钟的抖动。 尽管上图抖动较为夸张,但是它说明了抖动的时钟会导致采样在不均匀的时间间隔上触发。 这种不均匀导致要记录和复制的波形发生

2019-06-12 08:00:00

如何推导ADC的SNR?如何准确地估算某个时钟源的抖动?如何将其与ADC的孔径抖动组合?

2021-05-13 06:17:20

采样时钟抖动对ADC信噪比的性能有什么影响?如何实现低抖动采样时钟电路的设计?

2021-04-14 06:49:20

你知道RMS周期抖动? RMS周期抖动经验法则是什么? 实验室测量例子有没有可以进行参考? 如何知晓估算RMS周期间抖动经验法则?

2021-03-11 06:58:41

。这工作正常,直到我决定董事会所做的测量不够准确(在时间轴上)。因此,我将生成的时钟使能信号(2MHz)输出到IO-Pin,并使用示波器测量频率抖动。抖动似乎具有高斯分布,标准偏差约为28ns。我还测量

2020-08-19 06:09:57

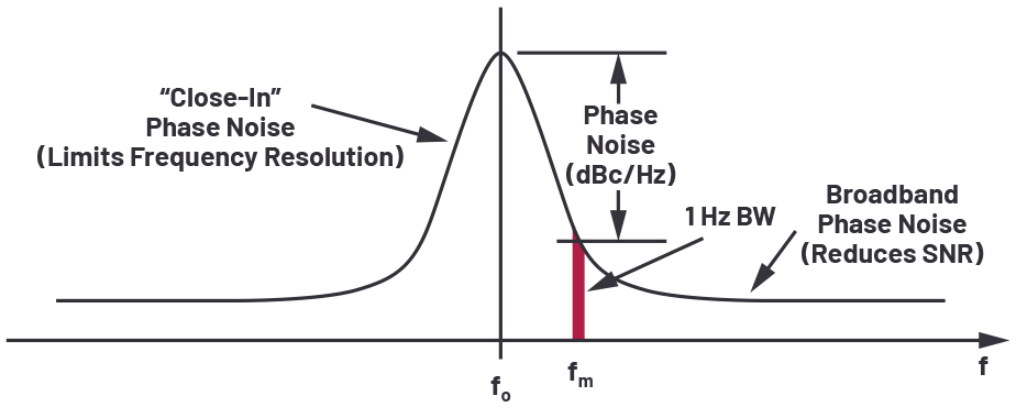

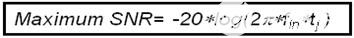

高信噪比=低ADC孔径抖动吗?在设计中,为了避免降低ADC的性能,工程师一般会采用抖动极低的采样时钟。然而,用于产生采样时钟的振荡器常常用相位噪声而非时间抖动来描述特性。那么,有木有方法将振荡器相位噪声转换为时间抖动呢?

2019-08-13 06:27:54

变形。在图5中,您可以看到时钟信号电平的切换距离是不均匀的;这就是时钟的抖动。 尽管上图抖动较为夸张,但是它说明了抖动的时钟会导致采样在不均匀的时间间隔上触发。 这种不均匀导致要记录和复制的波形发生

2016-01-18 15:31:09

需求。作为该最新博客系列的开篇文章,我将帮助您了解如何正确测量时钟缓冲器的附加抖动。为什么抖动很重要?在当今数据通信、有线及无线基础设施以及其它高速应用等高级系统中,时钟抖动是整体系统性能的关键因素。要

2018-09-13 14:38:43

设计采样系统时,关于时钟抖动性能如何考虑?抖动对时钟采样系统有何影响?

2021-04-06 06:07:38

一块音视频处理芯片输出1080i的数据Data及其同步时钟Clk,但是时钟clk的抖动很大,我该如何处理呢?另外,抖动很大的时钟源能否在后面接入一个模拟锁相环降低时钟的抖动呢?

2018-11-12 09:12:43

时钟抖动或结束时钟抖动的最佳方法是什么?

2021-03-17 07:04:07

随着数据速率的提高,时钟抖动分析的需求也在与日俱增。在高速串行数据链路中,时钟抖动会影响发射机、传输线和接收机的数据抖动。保证时钟质量的测量也在不断发展

2008-12-27 12:24:05 6

6 随着数据速率的提高,时钟抖动分析的需求也在与日俱增。在高速串行数据链路中,时钟抖动会影响发射机、传输线和接收机的数据抖动。保证时钟质量的测量也在不断发展。目前

2009-07-07 14:01:21 20

20 本文主要讨论采样时钟抖动对ADC 信噪比性能的影响以及低抖动采样时钟电路的设计。

2009-11-27 11:24:07 15

15 本文分析了晶振的漂移对GPS 接收机的影响,从锁相环理论的角度,重点分析了采样时钟抖动对基带载波跟踪和伪码跟踪性能的影响,并给出一种环路分级降带宽的方法来消除这种

2009-12-19 13:49:58 19

19 高速互联链路中参考时钟的抖动分析与测量

在高速互联链路中,发送器的参考工作时钟的抖动是影响整个

2010-04-15 14:01:39 19

19 随着支持直接IF采样的更高分辨率数据转换器的上市,系统设计师在选择低抖动时钟电路时,需要在性能/成本之间做出权衡取舍。许多用于标定时钟抖动的传统方法都不适用于数

2010-11-27 17:12:46 32

32

抖动的概念和抖动的测量方法

在数字通信系统,特别是同步系统中,随着系统时钟频率的不断提高,时间抖动成为影响通

2008-11-27 08:28:11 4050

4050

该应用笔记提出了超低抖动时钟合成器的一种设计思路,其目标是产生2GHz时钟时,边沿之间的抖动< 100fs。分析和仿真结果表明,要达到这一抖动指标,设计难度远远高于预期。关

2009-04-21 23:14:05 723

723

摘要:该应用笔记提出了超低抖动时钟合成器的一种设计思路,其目标是产生2GHz时钟时,边沿之间的抖动< 100fs。分析和仿真结果表明,要达到这一抖动指标,设计难度远远高于预

2009-04-22 09:35:13 296

296

摘要:这是一篇关于时钟(CLK)信号质量的应用笔记,介绍如何测量抖动和相位噪声,包括周期抖动、逐周期抖动和累加抖动。本文还描述了周期抖动和相位噪声谱之间的关系,并介绍

2009-04-22 10:16:50 3736

3736

摘要:该应用笔记提出了超低抖动时钟合成器的一种设计思路,其目标是产生2GHz时钟时,边沿之间的抖动< 100fs。分析和仿真结果表明,要达到这一抖动指标,设计难度远远高于预

2009-04-25 09:54:26 482

482

摘要:该应用笔记提出了超低抖动时钟合成器的一种设计思路,其目标是产生2GHz时钟时,边沿之间的抖动< 100fs。分析和仿真结果表明,要达到这一抖动指标,设计难度远远高于预

2009-05-08 10:19:03 431

431

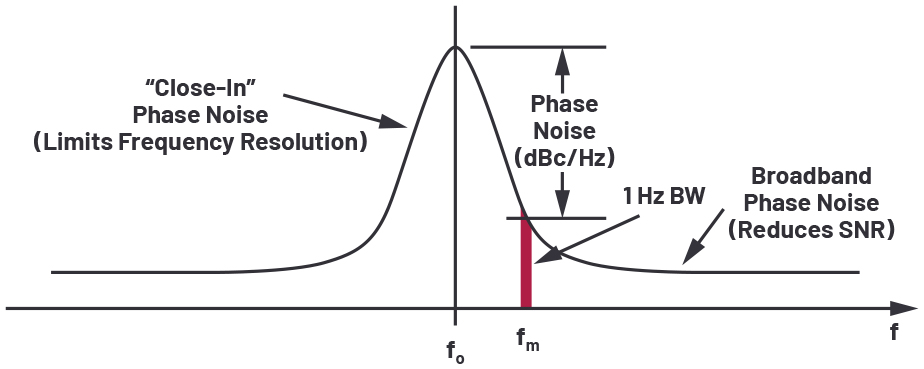

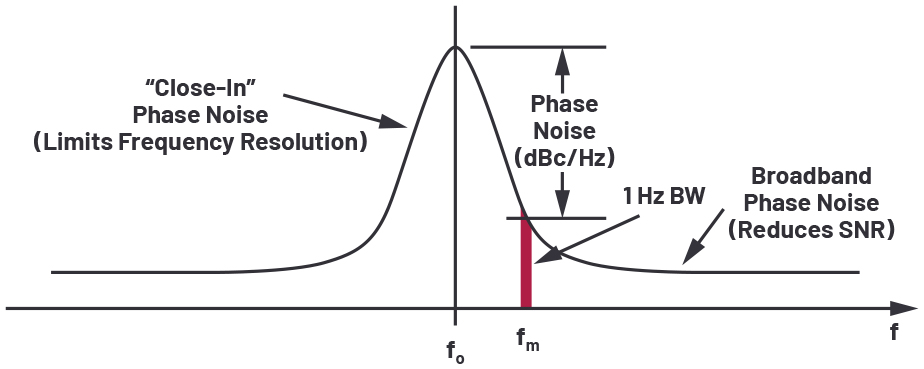

相位噪声和抖动的概念及其估算方法

时钟频率的不断提高使相位噪声和抖动在系统时序上占据日益重要的位置。本文介其概念及其对系统性能的影

2009-12-27 13:30:21 2173

2173

理解不同类型的时钟抖动

抖动定义为信号距离其理想位置的偏离。本文将重点研究时钟抖动,并探讨下面几种类型的时钟抖动:相邻周期抖动、周期抖动、时间间隔误

2010-01-06 11:48:11 1608

1608

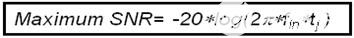

模数和数模转换器采样时钟内的抖动会对可实现的最大信噪比造成限制(参见参考文献部分van de Plassche著《集成模数和数模转换器》)。本应用笔记阐述了相位噪声和抖动的定义,绘制

2011-11-24 14:31:55 75

75 时钟抖动时域分析(下):

2012-05-08 15:26:25 29

29 如果明智地选择时钟,一份简单的抖动规范几乎是不够的。而重要的是,你要知道时钟噪声的带宽和频谱形状,才能在采样过程中适当地将它们考虑进去。很多系统设计师对数据转换器

2012-05-08 15:29:00 47

47 介绍 此应用笔记侧重于不同类型的时钟抖动。时钟抖动是从它的时钟边沿偏差理想的位置。了解时钟抖动非常重要在应用中,因为它起着关键作用,在时间预算一个系统。 随着系统数据速率的增加,定时抖动成为关键

2017-04-01 16:13:18 6

6 很多人都知道,抖动(这是时钟边沿不确定性)是不好的现象,其不仅可导致噪声增加,而且还会降低数据转换器的有效位数 (ENOB)。例如,如果系统需要 100MHz 14(最小值)位的 ENOB,我们

2017-04-08 04:51:23 1266

1266

了解高速ADC时钟抖动的影响将高速信号数字化到高分辨率要求仔细选择一个时钟,不会妥协模数转换器的采样性能(ADC)。 在这篇文章中,我们希望给读者一个更好的了解时钟抖动及其影响高速模数转换器的性能

2017-05-15 15:20:59 13

13 级,从而降低成本和功耗。在欠采样接收机设计中必须要特别注意采样时钟,因为在一些高输入频率下时钟抖动会成为限制信噪比(SNR) 的主要原因。 本系列文章共有三部分,第1 部分重点介绍如何准确地估算某个时钟源的抖动,以及如何将其与AD

2017-05-18 09:47:38 1

1 采样时钟抖动可对高性能ADCs信噪比性能的灾难。虽然信噪比和抖动之间的关系是众所周知的,但是大多数振荡器都是根据相位噪声来指定的。

2017-08-03 10:57:33 13

13 时钟抖动时域分析,第 2 部分

2017-10-26 16:10:42 6

6 时钟抖动时域分析 第 3 部分

2017-10-26 16:13:28 4

4 时间域中分析的时钟抖动,第 1 部分

2017-10-26 16:16:23 4

4 时钟产生抖动(jitter)会使发生抖动的时钟信号与未发生抖动的时钟信号在时域上存在偏差,从而使模数转换器的采样频率发生紊乱,最终导致模数转换器采样的不稳定性,使输出信号存在频谱毛刺,导致误码率上升

2017-11-11 18:22:26 9

9 本文分析了晶振的漂移对 GPS 接收机的影响,从锁相环理论的角度,重点分析了采样时钟抖动对基带载波跟踪和伪码跟踪性能的影响,并给出一种环路分级降带宽的方法来消除这种影响。该方法在保证最终伪码跟踪精度

2017-11-27 14:45:05 8

8 本文主要讨论采样时钟抖动对 ADC 信噪比性能的影响以及低抖动采样时钟电路的设计。 ADC 是现代数字解调器和软件无线电接收机中连接模拟信号处理部分和数字信号处理部分的桥梁,其性能在很大程度上决定

2017-11-27 14:59:20 17

17 时钟接口阈值区间附近的抖动会破坏ADC的时序。例如,抖动会导致确定性抖动由干扰引起,会通过某些方式使阈值发生偏移,通常受器件本身特性限制。查看时钟信号噪声通常有三种途径:时域、频域、相位域。

2018-03-12 13:39:33 21583

21583 仔细观察某个采样点,可以看到计时不准(时钟抖动或时钟相位噪声)是如何形成振幅变化的。由于高 Nyquist 区域(例如,f1 = 10 MHz 到 f2 = 110 MHz)欠采样带来输入频率的增加,固定数量的时钟抖动自理想采样点产生更大数量的振幅偏差(噪声)。

2018-05-14 08:51:40 3

3 该法则很简单。如果周期抖动分布是高斯或正态分布,则周期间抖动可以根据周期抖动估算如下

2018-07-12 09:10:07 13939

13939

ADI研讨会:高性能时钟: 解密抖动

2019-08-20 06:05:00 1656

1656 时钟设计人员通常会提供一个相位噪声,但不提供抖动规格。相位噪声规格可以转换为抖动,首先确定时钟噪声,然后通过小角度计算将噪声与主时钟噪声成分进行比较。相位噪声功率通过计算图9中的灰色区域积分得出。

2019-08-20 11:06:53 7787

7787

时钟抖动性能主题似乎是时钟,ADC和电源的当前焦点供应厂家。理由很清楚;时钟抖动会干扰包括高速ADC在内的数字电路的性能。高速时钟可以对它们所接收的功率的“清洁度”非常敏感,尽管量化关系需要一些努力。

2019-09-14 11:24:00 7712

7712

本文针对全方位的信号路径系统中的高速全差分运放及高频宽14位模拟/数字转换器的随机及固定时钟抖动,具体分析、研究了超低噪声兼时钟抖动滤除技术。研究选用双级联PLLatinum架构,配置高性能压控振荡器(VCXO),很好地实现了降噪和时钟抖动滤除的作用。

2020-09-23 10:45:00 2

2 AD9524:带6路差分或13路LVCMOS输出的抖动净化器和时钟发

2021-03-19 07:03:02 10

10 AN-1221: 使用ADF4002 PLL产生高速模数转换器所需的极低抖动编码(采样)时钟

2021-03-19 08:59:00 13

13 MT-200:降低ADC时钟接口抖动

2021-03-21 01:18:30 7

7 AD9525: 8路LVPECL输出低抖动时钟发生器

2021-03-21 15:00:20 0

0 电子发烧友网为你提供相位噪声处理:时钟抖动或结束时钟抖动的最佳方法是什么?资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-04 08:49:06 26

26 前言 :本文我们介绍下ADC采样时钟的抖动(Jitter)参数对ADC采样的影响,主要介绍以下内容: 时钟抖动的构成 时钟抖动对ADC SNR的影响 如何计算时钟抖动 如何优化时钟抖动 1.采样理论

2021-04-07 16:43:45 7378

7378

超低抖动时钟的产生与分配

2021-04-18 14:13:51 8

8 AN-1576:采用AD9958 500 MSPS DDS或AD9858 1 GSPS DDS和AD9515时钟分配IC的高性能ADC的低抖动采样时钟发生器

2021-04-30 09:48:42 13

13 ADC时钟接口中的最小抖动

2021-05-09 12:19:40 6

6 DN1013-了解时钟抖动对高速ADC的影响

2021-05-11 18:22:19 0

0 作者:John Johnson,德州仪器

本文介绍时钟抖动对高速链路性能的影响。我们将重点介绍抖动预算基础。

用于在更远距离对日益增长的海量数据进行传输的一些标准不断出现。来自

2021-11-22 15:52:21 1284

1284

MSP430或STM32,在使用内部ADC出现的采样数据异常抖动问题采样设计:用于检测供电线路电流及电压。产品运行在两种模式下,1、低功耗静态模式(仓储态),2、全功能全速运行模式(工作态)。在仓储

2021-12-08 09:06:10 12

12 PCIe 和网络时钟抖动测量之间的另一个显着差异在图 2 中并不明显。数字采样示波器 (DSO) 用于获取时钟周期或波形文件以计算 PCIe 时钟抖动,而不是 PNA。造成这种情况的主要原因是 PCIe 时钟支持扩频,而网络时钟不支持,而且从历史上看,PNA 一直无法使用正在扩频的时钟。

2022-05-05 15:50:44 4513

4513

高 AC 和 DC 精度,而无需牺牲 DC 精度以获得更高的采样率。然而,为了实现高 AC 性能,例如信噪比 (SNR),系统设计人员需要考虑采样时钟信号或控制采样和转换的转换启动信号上的抖动引入的误差

2022-07-19 16:37:37 1518

1518

时钟抖动、采样率和量化噪声是影响 ADC 中 SNR 和 SFDR 的最关键因素

2022-08-11 14:26:08 2684

2684

时钟采样系统最大限度减少抖动

2022-11-04 09:52:12 0

0 时钟抖动使随机抖动和相位噪声不再神秘

2022-11-07 08:07:29 4

4 时钟抖动解秘—高速链路时钟抖动规范基础知识

2022-11-07 08:07:30 1

1 精度,无需牺牲直流精度来换取更高的采样速率。然而,为实现高交流性能,如信噪比(SNR),系统设计人员必须考虑采样时钟信号或控制ADC中采样保持(SH)开关的转换启动信号上的抖动所带来的误差。随着目标信号和采样速率的增加,控制采样保持开

2022-11-13 11:25:11 473

473 对于频率成分相对较低的输入信号,例如在1MHz以下,时钟抖动变得不那么重要,但是当输入信号的频率为几百兆赫兹时,时钟上的抖动将成为误差的主要来源,并且将成为SNR的限制因素。

2023-01-03 14:35:04 823

823

1.1.1. 抖动定义和分类 ITU-T G.701对抖动的定义为:“抖动是指数字信号在短期内相对于理想位置发生的偏移重大影响的短时变化”。 对于真实物理世界中的时钟源,比如晶振、DLL、PLL,它们的时钟输出周期都不可能是一个单点的固定值,而是随时间而变化的

2023-03-10 14:54:32 657

657

系统时序设计中对时钟信号的要求是非常严格的,因为我们所有的时序计算都是以恒定的时钟信号为基准。但实际中时钟信号往往不可能总是那么完美,会出现抖动(Jitter)和偏移(Skew)问题。

2023-04-04 09:20:56 1637

1637 首先,我们需要理解什么是时钟抖动。简而言之,时钟抖动(Jitter)反映的是时钟源在时钟边沿的不确定性(Clock Uncertainty)。

2023-06-02 09:09:06 1026

1026

先来聊一聊什么是时钟抖动。时钟抖动实际上是相比于理想时钟的时钟边沿位置,实际时钟的时钟边沿的偏差,偏差越大,抖动越大。实际上,时钟源例如PLL是无法产生一个绝对干净的时钟。这就意味着时钟边沿出现在

2023-06-09 09:40:50 1128

1128

精度,无需牺牲直流精度来换取更高的采样速率。然而,为实现高交流性能,如信噪比(SNR),系统设计人员必须考虑采样时钟信号或控制ADC中采样保持(S&H)开关的转换启动信号上的抖动所带来的误差。随着目标信号和采样速率的增加,控制采样保持开关的信号抖动会成为主要误差源。

2023-06-15 16:30:12 381

381

本文主要介绍了时钟偏差和时钟抖动。

2023-07-04 14:38:28 960

960

电子发烧友网站提供《时钟抖动对ADC性能有什么影响.pdf》资料免费下载

2023-11-28 10:24:10 1

1 抖动是相位抖动的主要原因之一。在通信系统中,时钟扮演着非常重要的角色,它确定了信号的采样时间和传输速率。然而,由于各种原因,包括晶体振荡器的温度变化、电力供应的不稳定、电磁干扰等,时钟信号会产生偏移和抖动,导

2024-01-25 15:29:28 171

171

电子发烧友App

电子发烧友App

评论