有许多方法可以降低PCB设计的EMI

基本原理:

电源和地平面提供屏蔽

顶层和底层的地平面至少可以把多层板设计中的辐射降低10dB

PCB中器件的摆放-将模拟系统和数字系统离得尽可能远

使用合适的去耦电容可以降低电源/地平面的噪声, 并由此来消弱来自这些平面的EMI

保持信号走线远离PCB的边缘

避免在PCB走线中使用直角

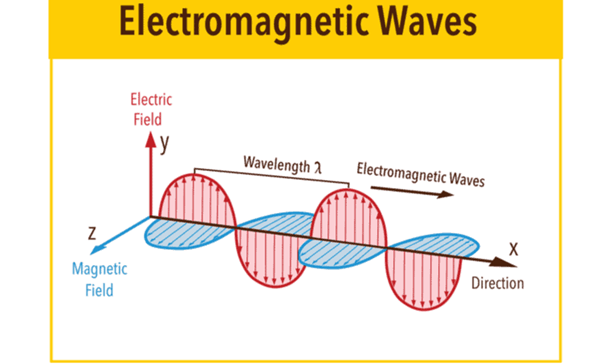

PCB走线会由于反射在基频和数倍谐波内引起谐振

在PCB设计获得最好的性能

随着放大器与转换器的提升,在PCB设计中获得所需要的性能是一种挑战

在设计之前进行布线指导和设计要点的培训会节取很多调试的时间

混合信号的布线技术

小信号的布线技术

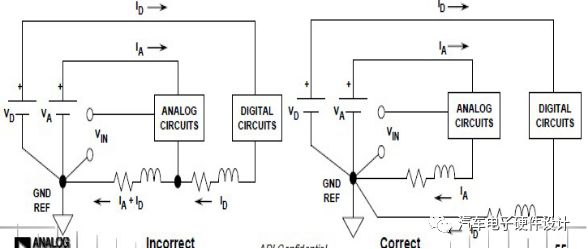

数字电流通过模拟回路的返回路径会导致错误的电压

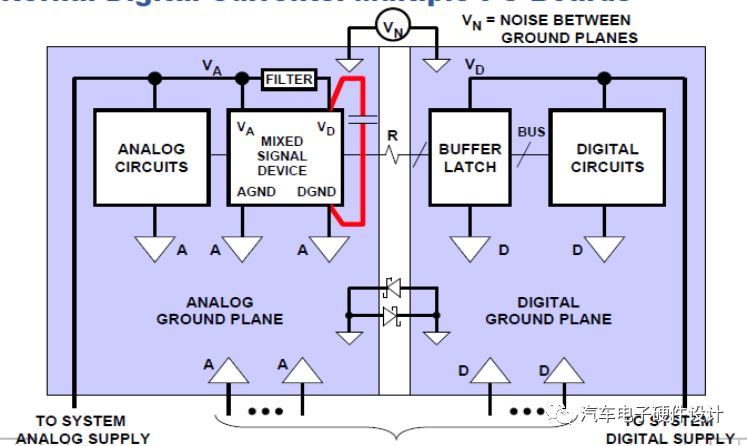

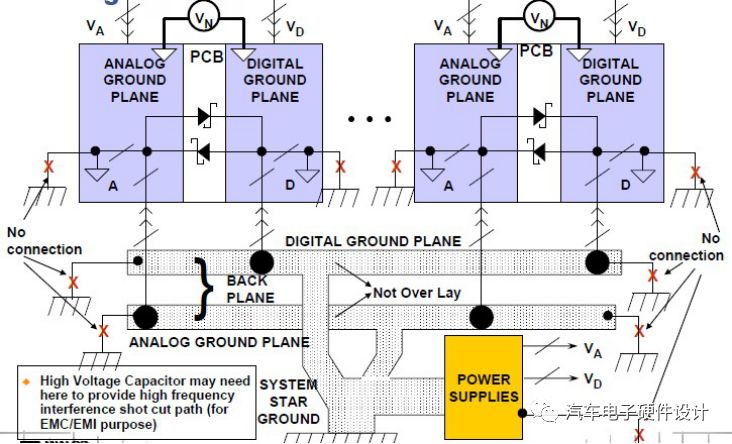

混合信号IC(较低的数字电流)的的接地:多板设计

星形接地-分离的模拟和数字地平面

地平面的特征

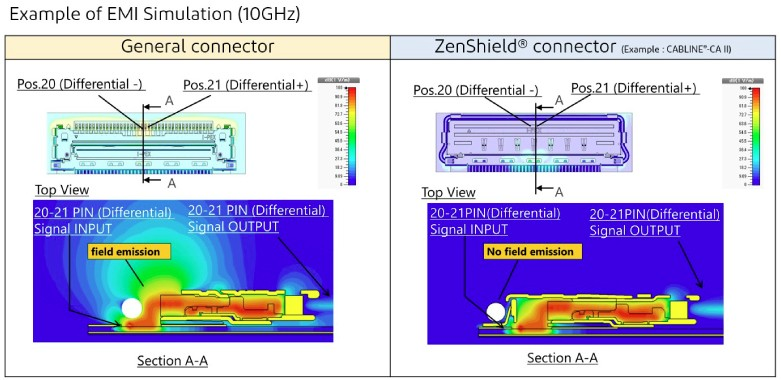

在同一块板子上,无线数字信号经常会有较高的数字逻辑,例如高增益的RF电路

屏蔽和接地对于接收端的设计是非常有效的

辐射在源端就应该被屏蔽掉

地平面电流应该回到源端

电源电流会通过最小电阻和电感路径回到源端

至少有一层完整的地平面

一个完整的PCB层是一个连续的地导体

提供最小的电阻和电感,但它不并不能解决所有的地平面问题

地平面的割裂会提高或者降低回路的性能-这里没有通用的规则

消除可能的接地回路

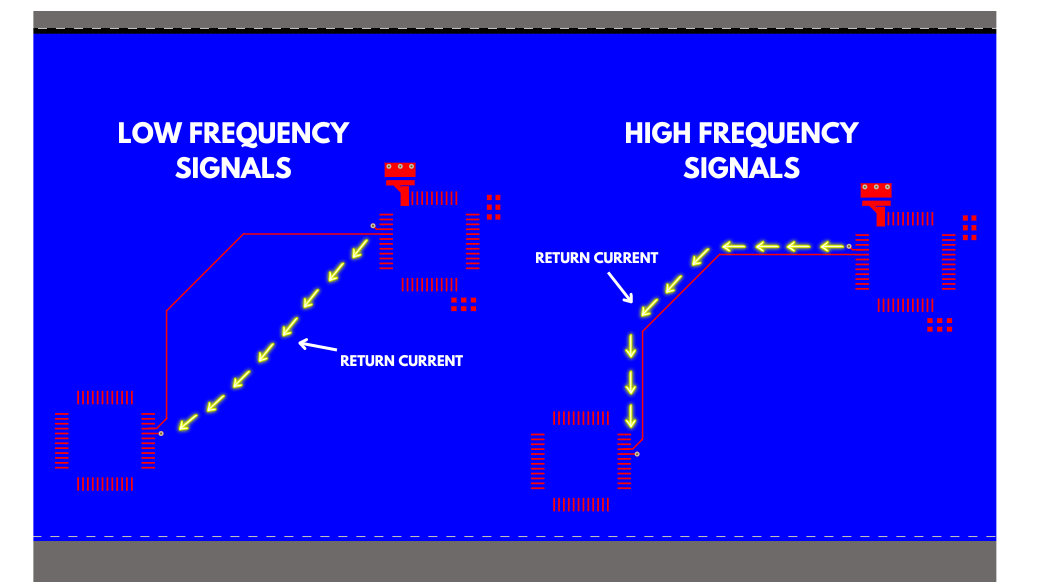

布线中特别需要关心的是数字返回电流不要通过板子中的模拟区域

怎样充分利用你的地平面

提供尽可能多的地平面

尤其是在高频走线的下面

尽可能使用较厚的金属板

降低电阻并提高散热

帮助降低由趋肤效应引起的损耗

安装上升时间较快或高频的器件时应尽可能的贴近板子

尽量不要使用加铅的器件

尽量找出对于地平面来说是最危险的器件以降低压降

将模拟电路圈禁在一个区域内,然后将数字电路放在另外一个区域内

避免将数字回路与模拟回路离得较近,这样有助于避免数字噪声耦合到模拟线上

完整地平面接地举例

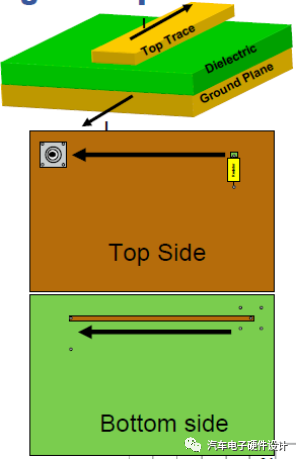

高速转换器PCB板的单个

GND层

顶层与底层的空地方用

GND覆盖,不要变成无连接的孤立铜区

尽可能的利用via连接2个或多个GND层,但不要将平面切碎

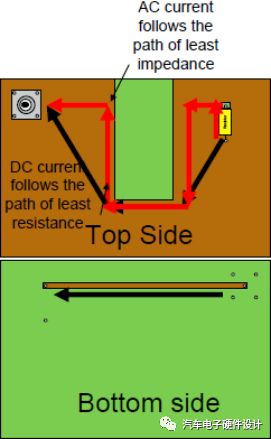

例子

顶层是完整的地平面

底层有一条走线通过RF连

接器边到负载

返回电流从负载流回接收端, 位于走线的正上方

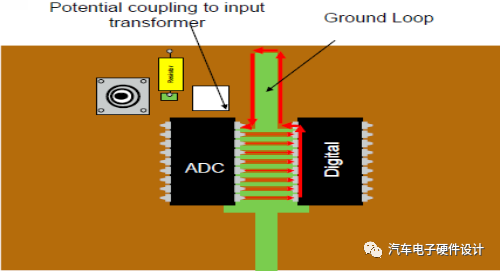

分割地平面举例

接地回路由两个分割开的地平面引入

例如一个数字线路以1v/ns开关,10pf的负载将会产生10mA的瞬态电流

如果6条线路同时开关,回路上将会有160mA的开关电流

单一地平面和分割地平面

对于高速转换器布线(>10Mhz)

使用单点GND层,没有AGND与

DGND的区别

分开的AGND和DGND连接到同一点一般只在低速设计中使用

(低于1Mhz)

一些分割线能够切开不同的区域, 但连接关系线必须宽于于器件(>10mmwidth),并且不能有别的信号线跨越他

如果要考虑所有的频率范围(比如从DC至50Mhz),那地平面的设计就需要就实际情况来研究

例子

在一个破裂的地平面上,返回电流总是顺着最小阻抗路径返回

在DC,电流顺着最小电阻路径返回,随着频率的升高,电流顺着最小电感路径返回

因为会有回路电感的存在,可能会引起EMI/RFI的问题

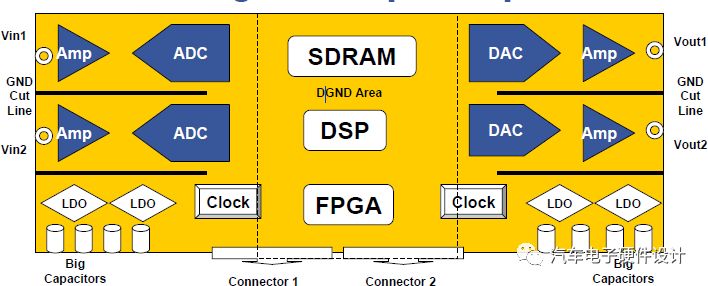

优秀的器件摆放与切割线

将模拟区域,混合信号区域和数字区域分割开

输入与输出没有交叉

时钟区域是一个单独的区域

供电电源是一个单独的区域,尤其是DC-DC区域

DC-DC在一个角落,最好在另外一块PCB板上

DC-DC必须使用分割线

大电容最好放置在角落,或靠近PCB的边缘

供电系统的优先规则

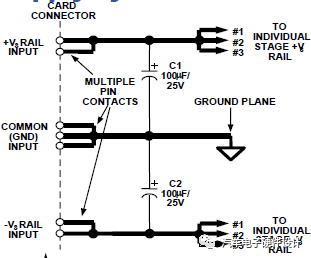

一个Card-entry的滤波器对于模拟系统中的中低频段噪声滤除是非常有好处的。

高性能的模拟电源系统使用线性调节器,其优先级如下:

AC linepower

DC-DC power conversionsystems

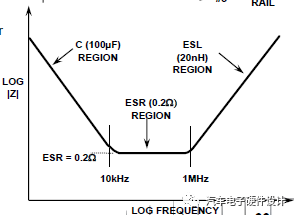

记住电解电容器阻抗随频率变化而变化

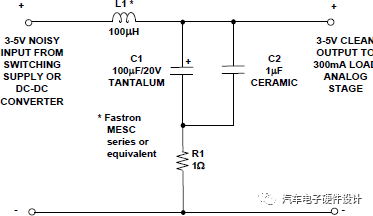

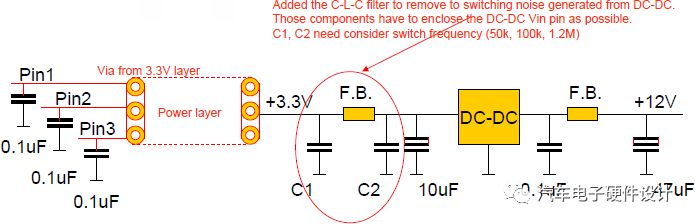

DC-DC 电源滤波

开关调节器应该尽量避免,如果不行…

控制噪声

提高布线和铺地的质量

考虑EMI

不建议DC-DC供电系统和模拟供电系统一样,至少要增加LDO

DC-DC供电可以和数字供电的ADC或 MCV(ADuC702x)一样

DC-DC应该远离ADC(OrADuc702x)

C-L-C婆婆器应靠近DC-DC

在电源平面铺一个较大的3.3v平面有很大帮助

-

pcb

+关注

关注

4417文章

23967浏览量

426189 -

emi

+关注

关注

54文章

3909浏览量

135933

原文标题:优秀PCB设计之降低PCB的EMI

文章出处:【微信号:QCDZYJ,微信公众号:汽车电子工程知识体系】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

怎样让变频器降低对DCS的信号干扰

EMI或EMC测试是屏蔽引起的吗?

如何管理线束到 PCB 接口的 EMI

结构对EMI噪声的影响

Spread Spectrum XO在医疗设备EMI控制中的关键应用

为了降低 EMI,厂商有多努力

新品EMI滤波器模块 高效滤除电路干扰

技术资讯 I 如何在 PCB 中降低 EMI 并优化 EMC?

怎样降低PCB的EMI

怎样降低PCB的EMI

评论