FPGA/ASIC技术

电子发烧友本栏目为FPGA/ASIC技术专栏,内容有fpga培圳资料、FPGA开发板、FPGA CPLD知识以及FPGA/ASIC技术的其它应用等;是您学习FPGA/ASIC技术的好栏目。FPGA的快速入门经验谈(part1)

有很多年轻人,被割裂了历史,被荒废了未来,迷茫, 迷茫到几乎绝望,不过,他们还年轻,青春尚存,还有创造力,还有奋斗的资本,其中不乏不甘心被抛弃,被覆盖之人。...

2017-02-11 1866

片上网络概述与FPGA研究(连载1)

片上网络Network-on-chip (NoC) 是一种应用于大规模集成电路(VLSI)系统中的,一种新的片上系统(System-on-chip)的设计方法。...

2017-02-11 2012

Chipworks拆解基于台积电28nm HPL工艺的赛灵思Kintex

Chipworks制程分析室的研究人员对使用台积电28nm HPL制程工艺(基于gatelast HKMG技术)制作的赛灵思Kintex-7 FPGA芯片进行了工艺 解剖,这是分析报告。...

2017-02-11 3925

Atlys开发板FPGA Design Flow LAB3的KPSM3程序

最近在使用Atlys开发板,简单地过了一下板子光盘上的程序。因为例子用到了PicoBlaze,而在这之前并没有接触过PicoBlaze的东西,所以一开始有畏难情绪。...

2017-02-11 1185

编写具有100%可靠性代码的几个技巧

您编写的代码是不是虽然在仿真器中表现正常,但是在现场却断断续续出错?要不然就是有可能在您使用更高版本的工具链进行编译时,它开始出错。您检查自己的测试平台,并确认测试已经做...

2017-02-11 1474

赛灵思(Xilinx)FPGA用户约束文件的分类和语法说明

FPGA设计中的约束文件有3类:用户设计文件(.UCF文件)、网表约束文件(.NCF文件)以及物理约束文件(.PCF文件),可以完成时序约束、管脚约束以及区域约束。...

2017-02-11 2105

Xilinx可编程逻辑器件设计与开发(基础篇)连载45:Spartan

本节将简单介绍在PlanAhead工具中如何应用ChipScope核和分析工具进行逻辑调试与验证。先通过一个向导将ChipScope核插入设计中,选择待测试的网线,并进行例化、连接和综合,最后,导入布局和时...

2017-02-11 1115

Xilinx可编程逻辑器件设计与开发(基础篇)连载44:Spartan

FloorPlanning 工具是PlanAhead 的一个组成部分,用它可以对FPGA 设计进行分析,首先找到设计中的时序问题或者拥塞的问题,然后再通过使用PloorPlanning 约束,以指导实现工具产生更优的结果。...

2017-02-11 1008

基于高速FPGA 的PCB 设计技巧

如果高速PCB 设计能够像连接原理图节点那样简单,以及像在计算机显示器上所看到的那样优美的话,那将是一件多么美好的事情。然而,除非设计师初入PCB 设计,或者是极度的幸运,实际的...

2017-02-11 942

Xilinx可编程逻辑器件设计与开发(基础篇)连载43:Spartan

在ISE 中可以进行时序分析,在PlanAhead 中同样也可以进行时序分析。下面介绍用PlanAhead 进行时序分析的步骤。...

2017-02-11 957

Xilinx可编程逻辑器件设计与开发(基础篇)连载42:Spartan

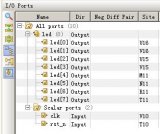

可以将综合后网表文件导入PlanAhead,然后在PlanAhead 中完成关键时钟,以及相关联的I/O 端口的分配。...

2017-02-11 986

Xilinx可编程逻辑器件设计与开发(基础篇)连载46:Spartan

我们知道,PicoBlaze微控制器只提供一个中断输入口,如果设计中需要多个中断,可以在FPGA中用逻辑实现。...

2017-02-11 722

FPGA开发技巧之同步复位与异步复位的理解

前两天和师兄讨论了一下design rule其中提到了同步异步复位的比较这个常见问题,据说也是IC公司经常问到的一面试题。...

2017-02-11 2629

Xilinx FPGA 嵌入式系统程序引导和启动的流程

这篇blog想弄清楚FPGA上电配置后程序引导和启动的整个流程是怎么样的,不是谈论如何编写bootloader。...

2017-02-11 2890

详细图解在NetFPGA上创建一个OpenFlow Switch的网络

Author: KiKiCompany:Digilent ChinaEmail : Date: 2012.02.14 目的 如 图所示,我们会创建一个基于OpenFlow Switch的网络。...

2017-02-11 2670

Xilinx可编程逻辑器件设计与开发(基础篇)连载50:Spartan

1. PICOBLAZE 嵌入式系统,包括1 个8 位的方波输出口,一个驱动两位7 段LED 的输出口,一个时钟输入和一个中断输入。...

2017-02-11 1011

Xilinx可编程逻辑器件设计与开发(基础篇)连载49:Spartan

通常情况下,如果对性能要求不是太高,最好是让PicoBlaze在低频下工作,因为它所处理的外设一般为低速设备,例如,串行通信,按键等。另外,低频工作也会减少等待周期,降低系统功耗。...

2017-02-11 1085

Xilinx可编程逻辑器件设计与开发(基础篇)连载47:Spartan

PicoBlaze微控制器支持最大256个输入口和256 个输出口,PicoBlaze与输入和输出有关的信号在“PicoBlaze微控制器接口信号”部分有详细说明,包括PORT_ID[7:0]、IN_PORT[7:0]、OUT_PORT[7:0]、READ_STROBE WRITE_STR...

2017-02-11 673

XPS中的时钟模块和复位模块

CLKIN为外部输入时钟,如果是外部差分时钟信号,在MHS文件的PORT行指定*_p、*_n管脚均为同样的Net,如dcm_clk_s,差分极性分别指定正负即可。...

2017-02-11 2992

Virtex6 GTX设计总结:预加重、均衡、输出振幅的值

在Xilinx的Virtex6 FPGA中,GTX作为一种低功耗的吉比特收发器,配置灵活,功能强大,并与FPGA内部的其他逻辑资源紧密联系,可用于实现多种高速接口(如XAUI、PCIE等)。...

2017-02-11 4361

Nexys3学习手记6:ClockingWizard探秘

这一节,我们首先会来了解下Nexys3上的主角儿XC6SLX16(Spartan-6家族)的时钟资源,当然不会照搬ug382.pdf(建议大家去浏览一遍)的内容凑篇幅,但身为“菜鸟”的特权同学也只能够蜻蜓点水般和...

2017-02-11 4205

Nexys3学习手记5:流水灯在线运行

在进行第一个工程实例前,顺便提一下设计工具相关资源的获取。从特权同学接触的几家FPGA开发工具来看,Xilinx在这方面做得应该算是最人性化的了,其设计资源可谓唾手可得。...

2017-02-11 1837

Nexys3学习手记2:建立自己的开发环境

接过Nexys3时,本以为能够提供一张资料光盘,结果大失所望,除了静电袋里一块精致的电路板,就只有一条用于供电和下载的USB连接线和两张活页。...

2017-02-11 1747

PowerPC平台Linux的移植(三)

如果你想使用ram disk,那么用以下命令进行编译:make zImage.initrd否则用以下命令:make以前编译2.4内核的时候之前都要用make dep 命令保证编译内核时所有的依赖,例如头文件,都存在。...

2017-02-11 981

PowerPC平台Linux的移植(二)

处理并编译内核源代码Linux内核的配置系统由三个部分组成,分别是:1. Makefile:分布在 Linux 内核源代码中的 Makefile,定义 Linux 内核的编译规则...

2017-02-11 1509

PowerPC平台Linux的移植(一)

PowerPC是早期Motorola和IBM联合为Apple的MAC机开发的CPU芯片,商标权同时属于IBM和Motorola,并成为他们的主导成品.IBM主要的PowerPC产品有PowerPC604s(深蓝内部的CPU), PowerPC750,PowerPCG3(1.1GHz).Motorola主要有MC和...

2017-02-11 2052

编辑推荐厂商产品技术软件/工具OS/语言教程专题

| 电机控制 | DSP | 氮化镓 | 功率放大器 | ChatGPT | 自动驾驶 | TI | 瑞萨电子 |

| BLDC | PLC | 碳化硅 | 二极管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 无刷电机 | FOC | IGBT | 逆变器 | 文心一言 | 5G | 英飞凌 | 罗姆 |

| 直流电机 | PID | MOSFET | 传感器 | 人工智能 | 物联网 | NXP | 赛灵思 |

| 步进电机 | SPWM | 充电桩 | IPM | 机器视觉 | 无人机 | 三菱电机 | ST |

| 伺服电机 | SVPWM | 光伏发电 | UPS | AR | 智能电网 | 国民技术 | Microchip |

| 开关电源 | 步进电机 | 无线充电 | LabVIEW | EMC | PLC | OLED | 单片机 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 蓝牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太网 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 语音识别 | 万用表 | CPLD | 耦合 | 电路仿真 | 电容滤波 | 保护电路 | 看门狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 阈值电压 | UART | 机器学习 | TensorFlow |

| Arduino | BeagleBone | 树莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 华秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |