练习九.利用状态机的嵌套实现层次结构化设计目的:1.运用主状态机与子状态机产生层次化的逻辑设计;

2.在结构化设计中灵活使用任务(task)结构。

在上一节,我们学习了如何使用状态机的实例。实际上,单个有限状态机控制整个逻辑电路的运转在实际设计中是不多见,往往是状态机套用状态机,从而形成树状的控制核心。这一点也与我们提倡的层次化、结构化的自顶而下的设计方法相符,下面我们就将提供一个这样的示例以供大家学习。

该例是一个简化的EPROM的串行写入器。事实上,它是一个EPROM读写器设计中实现写功能的部分经删节得到的,去除了EPROM的启动、结束和EPROM控制字的写入等功能,只具备这样一个雏形。工作的步骤是:1.地址的串行写入;2.数据的串行写入;3.给信号源应答,信号源给出下一个操作对象;4.结束写操作。通过移位令并行数据得以一位一位输出。

模块源代码:

module writing(reset,clk,address,data,sda,ack);

input reset,clk;

input[7:0] data,address;

output sda,ack; //sda负责串行数据输出;

//ack是一个对象操作完毕后,模块给出的应答信号。

reg link_write; //link_write 决定何时输出。

reg[3:0] state; //主状态机的状态字。

reg[4:0] sh8out_state; //从状态机的状态字。

reg[7:0] sh8out_buf; //输入数据缓冲。

reg finish_F; //用以判断是否处理完一个操作对象。

reg ack;

parameter

idle=0,addr_write=1,data_write=2,stop_ack=3;

parameter

bit0=1,bit1=2,bit2=3,bit3=4,bit4=5,bit5=6,bit6=7,bit7=8;

assign sda = link_write? sh8out_buf[7] : 1'bz;

always @(posedge clk)

begin

if(!reset) //复位。

begin

link_write<= 0;

state <= idle;

finish_F <= 0;

sh8out_state<=idle;

ack<= 0;

sh8out_buf<=0;

end

else

case(state)

idle:

begin

link_write <= 0;

state <= idle;

finish_F <= 0;

sh8out_state<=idle;

ack<= 0;

sh8out_buf<=address;

state <= addr_write;

end

addr_write: //地址的输入。

begin

if(finish_F==0)

begin shift8_out; end

else

begin

sh8out_state <= idle;

sh8out_buf <= data;

state <= data_write;

finish_F <= 0;

end

end

data_write: //数据的写入。

begin

if(finish_F==0)

begin shift8_out; end

else

begin

link_write <= 0;

state <= stop_ack;

finish_F <= 0;

ack <= 1;

end

end

stop_ack: //完成应答。

begin

ack <= 0;

state <= idle;

end

endcase

end

task shift8_out; //串行写入。

begin

case(sh8out_state)

idle:

begin

link_write <= 1;

sh8out_state <= bit0;

end

bit0:

begin

link_write <= 1;

sh8out_state <= bit1;

sh8out_buf <= sh8out_buf<<1;

end

bit1:

begin

sh8out_state<=bit2;

sh8out_buf<=sh8out_buf<<1;

end

bit2:

begin

sh8out_state<=bit3;

sh8out_buf<=sh8out_buf<<1;

end

bit3:

begin

sh8out_state<=bit4;

sh8out_buf<=sh8out_buf<<1;

end

bit4:

begin

sh8out_state<=bit5;

sh8out_buf<=sh8out_buf<<1;

end

bit5:

begin

sh8out_state<=bit6;

sh8out_buf<=sh8out_buf<<1;

end

bit6:

begin

sh8out_state<=bit7;

sh8out_buf<=sh8out_buf<<1;

end

bit7:

begin

link_write<= 0;

finish_F<=finish_F+1;

end

endcase

end

endtask

endmodule

测试模块源代码:

`timescale 1ns/100ps

`define clk_cycle 50

module writingTop;

reg reset,clk;

reg[7:0] data,address;

wire ack,sda;

always #`clk_cycle clk = ~clk;

initial

begin

clk=0;

reset=1;

data=0;

address=0;

#(2*`clk_cycle) reset=0;

#(2*`clk_cycle) reset=1;

#(100*`clk_cycle) $stop;

end

always @(posedge ack) //接收到应答信号后,给出下一个处理对象。

begin

data=data+1;

address=address+1;

end

writing writing(.reset(reset),.clk(clk),.data(data),

.address(address),.ack(ack),.sda(sda));

endmodule

仿真波形:[[wysiwyg_imageupload:252:height=174,width=496]]

练习:仿照上例,编写一个实现EPROM内数据串行读取的模块。编写测试模块,给出仿真波形。

利用状态机的状态机实现层次结构化设计

- 状态机(27117)

- FGPA(15865)

相关推荐

状态机编程实例-状态表法

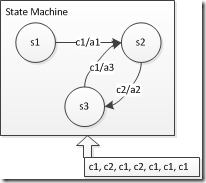

上篇文章,使用嵌套switch-case法的状态机编程,实现了一个炸弹拆除小游戏。本篇,继续介绍状态机编程的第二种方法:状态表法,来实现炸弹拆除小游戏的状态机编程。

2023-06-20 09:05:05 1190

1190

1190

1190

Spring状态机的实现原理和使用方法

说起 Spring 状态机,大家很容易联想到这个状态机和设计模式中状态模式的区别是啥呢?没错,Spring 状态机就是状态模式的一种实现,在介绍 Spring 状态机之前,让我们来看看设计模式中的状态模式。

2023-12-26 09:39:02 664

664

664

664

Verilog状态机+设计实例

在verilog中状态机的一种很常用的逻辑结构,学习和理解状态机的运行规律能够帮助我们更好地书写代码,同时作为一种思想方法,在别的代码设计中也会有所帮助。 一、简介 在使用过程中我们常说

2024-02-12 19:07:39 1818

1818

1818

1818

状态机

控制状态机控制状态机的初始化和状态转换的最佳方法是使用枚丽型输入控件。一般使用自定义类型的枚丽变量。使用子定义类型的枚丽变量可以是控件和实例乊间存在关联,使得添加或删除状态时所有的枚丽型输入控件副本自动更新。

2014-02-13 12:39:31

状态机如何暂停

程序一运行 就开始自动运行程序 状态机各种各种状态开始执行 我这里是布尔变量 每一秒点亮一个布尔按钮。我现在想在界面增加一个暂停按钮 当点暂停时候 此时暂停按钮文字成为继续 如果 状态机执行第二步

2018-04-09 09:23:30

状态机是什么意思

刚开始学fpga,读资料,有些名词不太理解,比如状态机,我只知道fpga就是由查找表和触发器构成的,状态机这个概念是怎么提出来的,干什么使得,求大神讲解,什么情况下用到

2013-04-25 18:35:55

状态机的相关资料下载

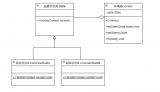

share,作者:亚索老哥)),原来状态机还可以这么简单地玩~~亚索老哥提出的状态机六步法(1)、定义状态接口(2)、定义系统当前状态指针(3)、定义具体状态,根据状态迁移图来实现具体功能和状态切换(4)、定义主程序上下文操作接口(6)、主程序通过上下文操作接口来控制系统当前状态的变化亚索老哥的状态机例程

2022-02-15 06:01:46

状态机编程

等待一段时间后,光标的位置就会右移,表示对最后输入字符的确认。因此,按键输入接口设计和实现的核心,更多的体现在软件接口处理程序的设计中。下面将以此为例,介绍有限状态机的分析设计原理,以及基于状态机思想

2008-07-10 18:00:24

状态机跳跃错误的解决办法?

大家好,我对状态机有疑问。我写了一个状态机来实现一些功能,设备是virtex-ii。机器中有26个状态,其中4个是A,B,C,D,E;输入信号为rdy_i和smp_rdy_i,输出信号为p_o

2020-07-08 10:51:29

FPGA/CPLD状态机稳定性研究

而言,状态机更加稳定,运行模式类似于CPU,易于实现顺序控制等.用VHDL语言描述状态机属于一种高层次建模,结果经常出现一些出乎设计者意外的情况:在两个状态转换时,出现过渡状态.在运行过程中,进入非法

2012-01-12 10:48:26

JKI状态机如何中止后面的状态

如题,JKI状态机中假如我点确定按钮,有一个状态序列开始执行。但是中途我点击个停止按钮,以后的状态不再执行,回到等待状态。请问用JKI状态机能实现吗?

2018-12-13 08:30:57

LabVIEW事件状态机

后右键的复制方式创建每个新分支,少出现连线的差错,同时也可以在每条线上备注用于区分。这种用到事件状态机比较合适用于传输每次状态下共享的或者改变的事件,数据以流的形式在每个状态传递。控制每个状态的标签

2019-07-06 14:31:33

LabVIEW程序设计模式研究和探讨(四)—状态机和事件结构结合

本帖最后由 zhihuizhou 于 2011-12-27 11:04 编辑

本节将介绍如何将状态机与事件结构结合起来形成一种新的、稳定的模式。这样可以同时避免基本状态机的第(1~5)个

2011-12-27 11:01:31

Labview状态机

本帖最后由 afnuaa 于 2017-5-24 11:22 编辑

状态机是一种普遍而有效的架构,我们可以利用状态机设计模式来实现状态图或流程图的算法。State Machines

2017-05-23 17:11:34

MCU裸机编程状态机的定义与注意事项是什么

MCU裸机编程的状态机框架--第一部分1 状态机的概念1.1 状态机的要素1.2 状态迁移表1.3 状态机思路实现一个时钟程序1.4 状态机应用的注意事项1.5 更复杂的状态机FSM编程是裸机编程

2022-02-14 06:02:46

Verilog实验,交通灯的状态机和非状态机实现

本帖最后由 御宇1995 于 2015-6-6 15:06 编辑

实验课要用FPGA(Altera的cycloneIV)实现交通灯,有用状态机和非状态机两种方法,以下是代码状态机实现(一个数

2015-06-06 15:03:52

labVIEW状态机在实战中的应用(基础)

问题:1.一个While循环+事件结构 组成的状态机(最简单的)2.一个Whie循环+用户事件+事件结构3.队列消息+while循环+事件结构 组成的状态机(较复杂)4.队列消息+while循环+用户

2018-12-25 16:53:35

labview状态机基本类型顺序结构

前文介绍了LV编程的重要概念---状态机,状态机是个基本概念或者说理论,其具体表现形式多种过样,很难具体分类,我根据个人在编程实践中的体会,归纳几种常见类型.一、顺序结构LV本身是有顺序结构的,而且

2011-11-29 16:55:53

不同形式的状态机占用资源问题

最近在CPLD里面做了一个4通道的模块,每个模块内都有一个状态机,开始我是用的一段式状态机写发,资源不够,然后我将状态机的写法改为3段式,(将状态转换一段,输出一段)发现资源降低了很多,问下,一段和三段式的状态机为什么对占用资源会有影响?或者谈谈一段和三段的综合情况?

2015-01-21 14:07:40

什么是状态机

一. 什么是状态机我们以生活中的小区的停车系统为例:停车杆一般没车的是不动的(初态),有车来的时候需要抬杆(状态1),车通过需要放杆(状态2),如果在放杆的过程中突然有车,又需要抬杆(状态3

2022-01-06 08:01:00

什么是状态机

目录1 前言2 状态机2.1 什么是状态机2.2 状态机的概念2.3 使用状态机写键盘的思路3 代码实例3.1 使用软件3.2 protues电路图3.2 状态机部分程序3.3 Keil工程文件

2022-01-24 06:23:02

什么是状态机?状态机的三种实现方法

文章目录1、什么是状态机?2、状态机编程的优点(1)提高CPU使用效率(2) 逻辑完备性(3)程序结构清晰3、状态机的三种实现方法switch—case 法表格驱动法函数指针法小节摘要:不知道大家

2021-12-22 06:51:58

什么是有限状态机呢

在嵌入式,机器人领域,由于多的复杂逻辑状态,我们编写程序的时候不得不考虑很多种情况,容易造成功能间的冲突。有限状态机(finite-state machine),简称状态机,是一种表示有限个状态以及状态间转移等行为的数学模型。状态机简单来说

2021-12-20 06:51:26

关于状态机结构

`老板交代一个任务,需要做一个测试机,完成IC的基本测试。本人白板一个,看了一些书籍和一些电子资料,做出了如下构想。考虑到一个IC有很多测试项,所以决定使用状态机结构。如图,我把IC的各个测试项做成

2013-08-07 11:16:10

单片机状态机按键长按和短按实现

本文只介绍主要代码段,完整代码可参考我的“蓝桥杯单片机状态机按键按下和松开实现不同功能”蓝桥杯单片机状态机按键长按和短按实现不同功能定义变量key_time 按键计时时长key_time_flag按键计时标志位实现长按和短按不同功能的代码段每过1ms,key_time自增1...

2022-01-06 08:26:45

取款机状态机汇总

根据CLD的课程写的取款机的逻辑。一边看一边改,从最简单的状态机,到事件驱动,生产者消费者模型,队列状态机,最后到AMC。实现的功能基本相同,但结构各有不同。取款机的逻辑非常简单,前面板也没有美化,只是实现了逻辑。附件提供给大家,希望和大家一起讨论学习。

2017-08-01 16:25:25

如何利用状态机进行编程呢

很多上升沿或下降沿,会引起误判。这里我们使用状态机的方式去处理,使用状态机还有一个好处就是可以很方便的去判断长按,短按,双击等状态。当触摸屏有触点按下时,PENIRQ 引脚会输出低电平,直到没有触摸...

2022-01-13 07:18:49

如何利用STM32去实现一种按键有限状态机呢

STM32实现按键有限状态机(超详细,易移植)一、状态机简而言之,状态机是使不同状态之间的改变以及状态时产生的相应动作的一种机制。1.1状态机的四要素现态:状态机当前状态。触发条件:改变当前状态

2022-02-16 06:58:52

如何写好状态机

一篇经典文献,详细讲解了一段、两段、三段式状态机的实现,效率、优缺点。看完后相信会对状态机有一个详细的了解。 状态机是逻辑设计的重要内容,状态机的设计水平直接反应工程师的逻辑功底,所以许 多公司

2011-10-24 11:43:11

如何用状态机消抖法实现单片机矩阵键盘的控制

键盘不习惯,于是干脆解决这个问题,用状态机消抖法实现矩阵键盘。代码下载地址:https://gitee.com/zhang-yanping/singlechip.git下面是代码/*功能:利用状态机消

2022-02-17 07:47:36

问个关于状态机的问题

问个关于状态机的问题,书上说的三段式状态机的第三段,同步时序的状态输出部分的状态到底是当前态还是次态啊?有的书写的是次态,case(next_state),有的写的是case(cur_state)。

2014-09-22 20:42:17

如何写好状态机

如何写好状态机:状态机是逻辑设计的重要内容,状态机的设计水平直接反应工程师的逻辑功底,所以许多公司的硬件和逻辑工程师面试中,状态机设计几乎是必选题目。本章在引入

2009-06-14 19:24:49 96

96

96

96状态机举例

状态机举例

你可以指定状态寄存器和状态机的状态。以下是一个有四种状态的普通状态机。 // These are the symbolic names for states// 定义状态的符号名称parameter [1

2009-03-28 15:18:28 893

893

893

893利用74LS161实现复杂状态机

本文主要介绍了是如何利用74LS161实现复杂状态机的。时序逻辑电路的数学模型是有限状态机。有限状态机它把复杂的控制逻辑分解成有限个稳定状态,在每个状态上判断事件,变连续处理为离散数字处理,符合计算机的工作特点。本文主要讨论使用MSI同步计数器74LS161进行复杂状态机的设计。

2018-01-18 09:00:02 8299

8299

8299

8299

什么是状态机 状态机的描述三种方法

状态机 1、状态机是许多数字系统的核心部件,是一类重要的时序逻辑电路。通常包括三个部分:一是下一个状态的逻辑电路,二是存储状态机当前状态的时序逻辑电路,三是输出组合逻辑电路。 2、根据状态机的输出

2020-11-16 17:39:00 24811

24811

24811

24811FPGA:状态机简述

本文目录 前言 状态机简介 状态机分类 Mealy 型状态机 Moore 型状态机 状态机描述 一段式状态机 二段式状态机 三段式状态机 状态机优缺点 总结 扩展-四段式状态机 01. 前言 状态机

2020-11-05 17:58:47 6145

6145

6145

6145

什么是状态机?状态机5要素

玩单片机还可以,各个外设也都会驱动,但是如果让你完整的写一套代码时,却无逻辑与框架可言。这说明编程还处于比较低的水平,你需要学会一种好的编程框架或者一种编程思想!比如模块化编程、状态机编程、分层思想

2021-07-27 11:23:22 19223

19223

19223

19223

利用状态机实现对tlc5620dac控制的实验

利用状态机实现对tlc5620dac控制的实验(肇庆理士电源技术有限公司图片)-利用状态机实现对tlc5620dac控制的实验,适合新手学习参考

2021-09-16 12:02:11 9

9

9

9利用状态机实现对tlc5620dac控制的项目设计

利用状态机实现对tlc5620dac控制的项目设计(开关电源技术趋势)-利用状态机实现对tlc5620dac控制的项目设计,适合感兴趣的学习者学习.

2021-09-16 12:12:26 9

9

9

9利用状态机实现对tlc5620dac控制.

利用状态机实现对tlc5620dac控制.(西工大现代电源技术答案)-利用状态机实现对tlc5620dac控制.适合感兴趣的学习者学习.

2021-09-16 12:21:46 11

11

11

11状态模式(状态机)

share,作者:亚索老哥)),原来状态机还可以这么简单地玩~~亚索老哥提出的状态机六步法(1)、定义状态接口(2)、定义系统当前状态指针(3)、定义具体状态,根据状态迁移图来实现具体功能和状态切换(4)、定义主程序上下文操作接口(6)、主程序通过上下文操作接口来控制系统当前状态的变化亚索老哥的状态机例程

2021-12-16 16:53:04 7

7

7

7状态机要实现哪些内容

状态机模式是一种行为模式,通过多态实现不同状态的调转行为的确是一种很好的方法,只可惜在嵌入式环境下,有时只能写纯C代码,并且还需要考虑代码的重入和多任务请求跳转等情形,因此实现起来着实需要一番考虑

2023-06-22 14:26:00 411

411

411

411

如何在FPGA中实现状态机

状态机往往是FPGA 开发的主力。选择合适的架构和实现方法将确保您获得一款最佳解决方案。 FPGA 常常用于执行基于序列和控制的行动, 比如实现一个简单的通信协议。对于设计人员来说,满足这些行动

2023-07-18 16:05:01 499

499

499

499

如何生成状态机框架

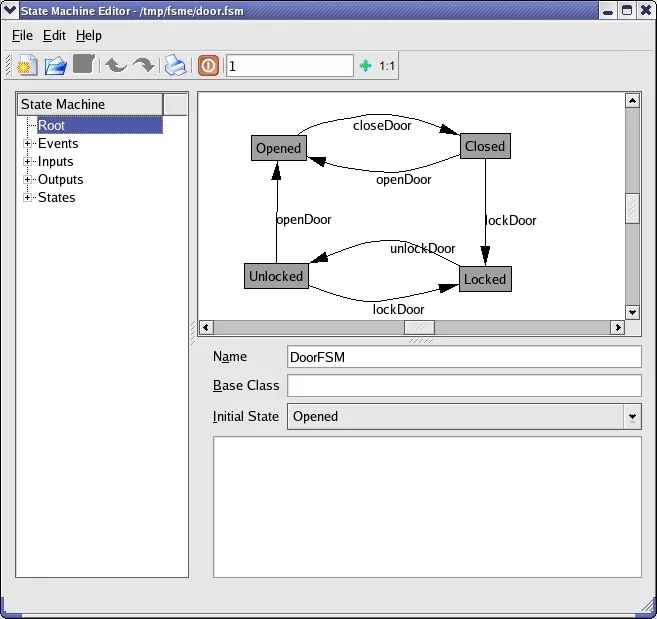

生成状态机框架 使用FSME不仅能够进行可视化的状态机建模,更重要的是它还可以根据得到的模型自动生成用C++或者Python实现的状态机框架。首先在FSME界面左边的树形列表中选择"Root

2023-09-13 16:54:15 618

618

618

618

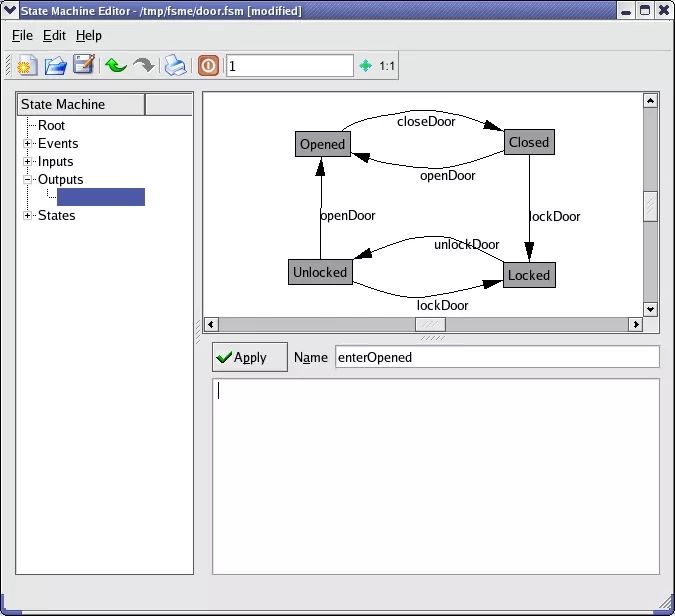

如何使用FSME来定制状态机

定制状态机 目前得到的状态机已经能够响应来自外部的各种事件,并适当地调整自己当前所处的状态,也就是说已经实现了状态机引擎的功能,接下来要做的就是根据应用的具体需求来进行定制,为状态机加入与软件系统

2023-09-13 16:57:37 821

821

821

821

什么是状态机?状态机的种类与实现

状态机,又称有限状态机(Finite State Machine,FSM)或米利状态机(Mealy Machine),是一种描述系统状态变化的模型。在芯片设计中,状态机被广泛应用于各种场景,如CPU指令集、内存控制器、总线控制器等。

2023-10-19 10:27:55 3405

3405

3405

3405 电子发烧友App

电子发烧友App

评论