FPGA/ASIC技术

电子发烧友本栏目为FPGA/ASIC技术专栏,内容有fpga培圳资料、FPGA开发板、FPGA CPLD知识以及FPGA/ASIC技术的其它应用等;是您学习FPGA/ASIC技术的好栏目。7 50T 入门级FPGA评估套件上手评测

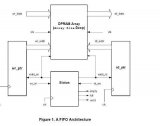

FPGA即现场可编程门阵列,属于可编程逻辑器件的一种。随着工艺的进步和EDA设计工具的不断发展,FPGA的门槛(学习成本和价格成本)也越来越低,目前已经成为实现数字系统的主流平台之一。...

2017-02-11 1281

带反激直流电源的双通道模拟输入/模拟输出

高级制造、定制生产和成本压力持续推动工厂向更高速性能和更高灵活性方向发展。为满足“不妥协”工厂环境的要求,MAXREFDES32#子系统参考设计提供两路高速、高精度、400ksps、16位模拟输入通...

2017-02-11 1493

实例讲解系统散热解决方案

在系统设计的初期我们不仅要考虑要实现的功能,性能,可操作性等方面,还有一方面便是实地的使用环境,如高温,高湿等恶劣的条件给系统设计提出了新的要求...

2017-02-11 4643

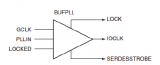

Xilinx可编程逻辑器件设计与开发(基础篇)连载40:Spartan

最大化【Package Pins】,如图10-45 所示, 和按钮配合,完成对器件引脚的排序,如图中我们将所有VREF 引脚排在一起,选中所有VREF 引脚,右键功能选择【Set Prohibit】,禁止所有VREF 引脚的分配。...

2017-02-11 1080

Xilinx可编程逻辑器件设计与开发(基础篇)连载38:Spartan

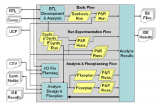

PlanAhead允许导入多种不同类型的源文件,包括HDL和NGC核。在RTL编辑器中可以打开、编辑、开发RTL源文件。下面我们介绍【Sources】源文件视图和RTL编辑器的使用。...

2017-02-11 1545

Xilinx可编程逻辑器件设计与开发(基础篇)连载37:Spartan

这里介绍如何用PlanAhead进行RTL代码开发与分析。需要说明一点,本章所用的所有实例都可以在PlanAhead的安装目录E:\Xilinx\11.1\PlanAhead\testcases\PlanAhead_Tutorial下找到,本节使用的是source文件夹中的文...

2017-02-11 1082

Xilinx可编程逻辑器件设计与开发(基础篇)连载36:Spartan

PlanAhead工具是Xilinx提供的一个集成的、可视化的FPGA设计工具,它可以被应用于FPGA设计过程中的不同阶段,常见的应用包括用PlanAhead进行RTL源代码的开发、I/O引脚规划、RTL网表分析、布局布线结...

2017-02-11 2384

Xilinx可编程逻辑器件设计与开发(基础篇)连载34:Spartan

ChipScope Pro内核插入器的文件后缀名为cdc。在ISE工程中可以创建一个新的cdc程序,也可以在实现流程中激活内核插入器。...

2017-02-11 1473

Xilinx可编程逻辑器件设计与开发(基础篇)连载35:Spartan

ChipScope Pro 分析工具(Analyzer tool)直接与ICON、ILA、IBA、VIO及IBERT核相连,用户可以实时地创建或修改触发条件。...

2017-02-11 2126

Xilinx可编程逻辑器件设计与开发(基础篇)连载33:Spartan

下面通过一个简单8位计数器的例子,了解如何在工程中添加ChipScope Pro内核生成器的各个IP核,对FPGA内部节点和逻辑进行观测。在该实例中,我们将调用一个ICON、一个ILA和一个VIO。...

2017-02-11 1164

Xilinx可编程逻辑器件设计与开发(基础篇)连载32:Spartan

双击【Xilinx Core Generator】,打开现有的IP核工程项目或者创建一个新的IP核工程。...

2017-02-11 1099

Xilinx可编程逻辑器件设计与开发(基础篇)连载31:Spartan

双击【Xilinx Core Generator】,打开现有的IP核工程项目或者创建一个新的IP核工程。【View by function】→【Debug & Verification】→【ChipScope Pro】...

2017-02-11 893

Xilinx可编程逻辑器件设计与开发(基础篇)连载30:Spartan

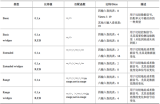

Xilinx针对不同类型的调试IP核,提供了不同的核生成器。本节重点介绍Xilinx Core Generator Tool(Xilinx IP核生成器)所支持的ChipScope Pro调试IP核ICON、ILA、VIO和ATC2及其属性...

2017-02-11 1193

Xilinx可编程逻辑器件设计与开发(基础篇)连载29:Spartan

ChipScope Pro 提供了多种不同功能的调试内核,通常分成三类:逻辑调试内核、误比特率测试核和集成总线分析核。用户根据系统的调试要求,应用不同的调试内核,方便快速地找到设计中存在的...

2017-02-11 1052

Xilinx可编程逻辑器件设计与开发(基础篇)连载28:Spartan

FPGA和PCB设计人员保留一定数量FPGA引脚作为测试引脚,FPGA设计者在编写FPGA代码时,将需要观察的FPGA内部信号定义为模块的输出,在综合实现时再把这些信号锁定到保留的测试引脚上,最后连接...

2017-02-11 1033

Adam Tayloy玩转MicroZed系列59:Zynq与PicoBlaze第4章

在以前发布的玩转MicroZed系列博客中,我们建立了一个基于Zynq的系统,通过使用双端口RAMS和BRAM(块RAM)控制器将两个PicoBlaze处理器核连接到Zynq的PS部分,现在我们将学习一下怎样实现更新存储...

2017-02-11 1420

Adam Taylor玩转MicroZed系列之58:Zynq和PicoBlaze第3部分

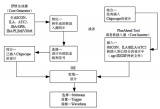

Zynq SoC的处理系统提供额外功能让我们可以建立一个更加灵活的Zynq 程序下载系统以适应更多工作。...

2017-02-11 1531

Adam Taylor玩转MicroZed系列之57:Zynq和PicoBlaze第二部分

到现在为止,我们知道如何在基于Zynq SoC的系统中例化PicoBlaze 软核处理器。在这篇博客,我们将继续探索更多关于如何生成PicoBlaze 程序以及如何使用JTAG接口更新程序而不是重新编译整个设计。...

2017-02-11 1282

Xilinx可编程逻辑器件设计与开发(基础篇)连载41:Spartan

设计者可以在【Clock Regions】窗口、【I/O Ports】窗口或者【Package Pins】窗口选择一个或多个对象,或者单击按钮取消所有选择,再运行【Tools】→【Clear Placement Constraints】命令...

2017-02-11 917

赛灵思 FPGA的配置与JTAG(一)

最近自己做了一块FPGA板子,不慎将PROM的两根引脚连错,导致在配置时无法正确识别PROM的型号,颠三倒四地排除了一个星期问题最终幸运解决。之后感叹自己实在是不小心,导致如此低级错误,...

2017-02-11 3766

针对赛灵思ISE工具的verilog编程经验小结

用了半个多月的ISE,几乎全是自学起来的,碰到了很多很多让人DT好久的小问题,百度也百不到,后来还是都解决了,为了尽量方便以后的刚学ISE的童鞋不再因为一些小问题而纠结,把这几天的...

2017-02-11 4160

赛灵思公司提供的Verilog(FPGA/CPLD)设计小技巧

这是一个在设计中常犯的错误列表这些错误常使得你的设计不可靠或速度较慢为了提高你的设计性能和提高速度的可靠性你必须确定你的设计通过所有的这些检查 。...

2017-02-11 595

编辑推荐厂商产品技术软件/工具OS/语言教程专题

| 电机控制 | DSP | 氮化镓 | 功率放大器 | ChatGPT | 自动驾驶 | TI | 瑞萨电子 |

| BLDC | PLC | 碳化硅 | 二极管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 无刷电机 | FOC | IGBT | 逆变器 | 文心一言 | 5G | 英飞凌 | 罗姆 |

| 直流电机 | PID | MOSFET | 传感器 | 人工智能 | 物联网 | NXP | 赛灵思 |

| 步进电机 | SPWM | 充电桩 | IPM | 机器视觉 | 无人机 | 三菱电机 | ST |

| 伺服电机 | SVPWM | 光伏发电 | UPS | AR | 智能电网 | 国民技术 | Microchip |

| 开关电源 | 步进电机 | 无线充电 | LabVIEW | EMC | PLC | OLED | 单片机 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 蓝牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太网 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 语音识别 | 万用表 | CPLD | 耦合 | 电路仿真 | 电容滤波 | 保护电路 | 看门狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 阈值电压 | UART | 机器学习 | TensorFlow |

| Arduino | BeagleBone | 树莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 华秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |