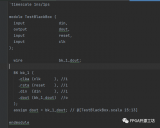

Clock Generator模块:

端口说明:CLKIN为外部输入时钟,如果是外部差分时钟信号,在MHS文件的PORT行指定*_p、*_n管脚均为同样的Net,如dcm_clk_s,差分极性分别指定正负即可。CLKFBIN为DCM的CLKFB输入端口,如果选择使用,即DCM使用外部反馈方式,此时CLKFBOUT输出口也应该使用,且CLKFBOUT连接到CLK0输出口,而CLKFBIN连接到CLKFBOUT经过时钟分配网络后的信号,用于调节时钟信号延迟。如果不使用CLKFBIN,则CLKFBOUT也不使用,在DCM内部把CLK0的输出经过BUFG缓冲后,一路送到CLK0端口,一路送给CLKFBIN。

参数说明:

C_CLKFBIN_FREQ、C_CLKFBOUT_FREQ分别设置CLKFBIN和CLKFBOUT的频率,设置0指不使用,两者必须设置相同。C_CLKOUTi_FREQ设置CLKOUTi的输出频率,0指CLKOUTi不使用。C_CLKOUTi_GROUP用于设置组号,可以把多个输出设置为相同的组,这样同组时钟通过同一个DCM或PLL输出,减少时钟间的相位偏移(skew)。C_CLKOUTi_BUF如果设TRUE,则相应的CLKOUTi插入BUFG,一般设TRUE,但输出给某些DDR颗粒的时钟信号不设TRUE。

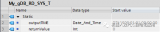

Processor System Reset Module模块:

端口说明:Slowest_sync_clk为系统中最慢的时钟,一般为PLB总线时钟。Ext_Reset_In为外部输入复位信号,Aux_Reset_In为辅助的第二个外部输入复位信号,一般不用。MB_Debug_Sys_Rst为调试用,和Ext_Reset_In功能相同,但总是高有效。Dcm_locked为模块输入信号,如果系统没有用DCM,则接高,如果使用一个DCM产生系统时钟,则连接此DCM的Locked信号,如果系统使用多个DCM产生系统时钟,则连接最后一个Locked的DCM。MB_Reset为输出的MB的复位信号。Bus_Struct_Reset和Peripheral_Reset为输出的总线和外设复位信号,其个数可根据C_NUM_BUS_RST、C_NUM_PERP_RST定制。

注:DCM的Locked信号为高指所有输出时钟均已稳定。

参数说明:C_EXT_RST_WIDTH、C_AUX_RST_WIDTH定义外部输入复位信号(端口Ext_Reset_In)的宽度。Slowest_sync_clk为PLB总线时钟,Ext_Reset_In宽度为C_EXT_RST_WIDTH所设置的时钟周期再加上1到2周期(考虑到电路中的时钟延迟)。Ext_Reset_In变为0时,经过C_EXT_RST_WIDTH个周期,电路退出复位状态。

C_EXT_RESET_HIGH、C_AUX_RESET_HIGH定义外部输入复位信号高有效还是低有效。一般设高有效,即1。MB_Debug_Sys_Rst总是高有效。

C_NUM_BUS_RST、C_NUM_PERP_RST定义总线和外设所需要的复位信号个数,如有一个PLB总线和两个OPB总线,C_NUM_BUS_RST可设为3,某些情况下可能利于驱动和布线。一般为1即可,三个总线可用同一个总线复位信号驱动。C_NUM_PERP_RST类似。

控制方式:上电时会自动产生复位脉冲序列;外部Ext_Reset_In、Aux_Reset_In满足复位条件时模块产生复位脉冲序列;MB_Debug_Sys_Rst满足复位条件时模块产生复位脉冲序列。

文章来源:seadoncas的专栏

XPS中的时钟模块和复位模块

- XPS(11833)

- 时钟模块(14235)

- 复位模块(2297)

相关推荐

基于MCU的高级时钟控制模块设计方案

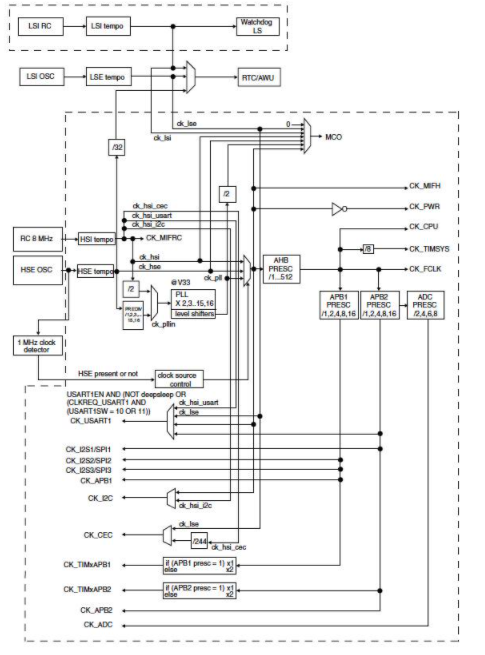

在使用 PLL 或 FLL 调整源时钟(如果需要)后,时钟分配网络将负责为每个关键 MCU 模块提供单独的时钟。CPU 及其相关的内存系统将需要自己的时钟,但通常各种外围设备也将拥有自己的时钟。

2022-08-05 12:44:57 1829

1829

1829

1829

ATK-7寸V2 TFTLCD模块

ATK-7寸V2 TFTLCD模块 MODULE_100X180MM 8/9/12/16 bit 80 Parallel por

2023-03-28 13:05:53

FPGA全局复位及局部复位设计分享

线将会是一个和时钟一样多扇出的网络,如此多的扇出,时钟信号是采用全局时钟网络的,那么复位如何处理?有人提出用全局时钟网络来传递复位信号,但是在FPGA设计中,这种方法还是有其弊端。一是无法解决复位结束

2019-05-17 08:00:00

S32G399如何配置时钟模块?

。

我们希望所有这些实例都可以独立运行,因此它们都配置了时钟模块。而且它们独立运行时没有问题。但是当我们使用Bootloader来加载和运行所有这些实例时,有些功能就无法工作,甚至会出现系统复位的情况。

以上案例如何配置时钟模块,所有实例一起工作时都需要配置时钟且不冲突。

2023-05-30 08:12:04

STM32F2的复位和时钟控制介绍

复位源

系统复位

电源复位

备份域复位

时钟模块

时钟树

各时钟信号及其特性

PLL的配置以及扩频技术(新增)

时钟测量

时钟信号的输出

STM32F1和STM32F2时钟特性比较

2023-09-13 07:16:16

STM32的复位和时钟控制(RCC)

1.1 复位参考1.2 stm32的时钟系统1.2.1 stm32时钟树 stm32有以下四种时钟源(内部时钟源起振较快,刚上电时默认使用内部时钟源,外部时钟源叫稳定精确):高速外部时钟(HSE

2015-02-12 15:41:46

STM32系列芯片的I2C模块作为主时,是否有产生9个时钟功能协助从设备复位?

STM32系列芯片的I2C模块作为主时,是否有产生9个时钟功能协助从设备复位?以及作为slave时,是否在收到9个时钟后,模块复位?

2024-03-12 08:25:48

什么是复位?什么又是时钟

我写启动文件涉及到,其实,每个功能的实现都涉及到时钟。我们首先说明一下RCCRCC:复位和时钟控制什么是复位,什么又是时钟?在STM32参考手册中文版我们可以看到注意“除了时钟控制器的RCC_CSR寄存器中的复位标志位和备份区域中的寄存器(见图4)以外,系统复位将复位所有寄存器至它们的复位状态。”这

2022-02-15 06:28:29

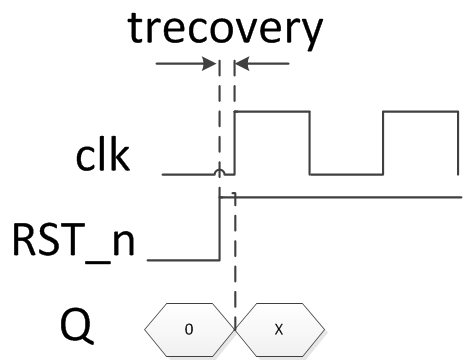

全局时钟--复位设计

所谓亚稳态,是指“trecovery(recovery time)指的是原本有效的异步复位信号释放(对低电平有效的复位来说就是上跳沿)与紧跟其后的第一个时钟有效沿之间所必须的最小

2012-01-12 10:45:12

最大时钟速度ISR模块如何?

大家好请告知最大时钟速度ISR模块如何?用时钟模块测试ISR模块中断,最大频率为APROX。3-4千赫。如何使用较大频率的ISR?感谢信息卡米尔 以上来自于百度翻译 以下为原文Hi all

2019-05-31 09:25:55

电源模块与复位模块及其时钟模块解析

电压,有的则不可以承受5V电压。复位模块——上电复位:打开电源的时候,复位一次——可编程的电压检测器:当单片机工作电压低于某一个电压值的时候,复位一次,保证单片机的稳定工作。时钟模块(重点)...

2021-12-27 06:51:16

深入讨论HCS08的内部时钟源模块

本文档将深入介绍内部时钟源模块(Internal ClockSource, ICS),该模块可以在部分HCS08 系列微控制器中找到。对HCS08 MCU 来说, ICS 模块不但是一个非常灵活的时钟源,而且对于该系列

2009-04-17 22:08:11 13

13

13

13高保持小型时钟模块

高保持小型时钟模块是一款尺寸为36.2*27.2*15mm的小体积、保持能力优于±1.5us/24h(△T=±5℃)的时钟模块产品。产品特点:· 小体积,36.2*27.2*15mm的封装尺寸

2023-12-20 16:06:00

国产时钟模块实时高精度

高保持小型时钟模块是一款尺寸为36.2*27.2*15mm的小体积、保持能力优于±1.5us/24h(△T=±5℃)的时钟模块产品。产品特点:· 小体积,36.2*27.2*15mm的封装尺寸

2024-01-24 10:35:32

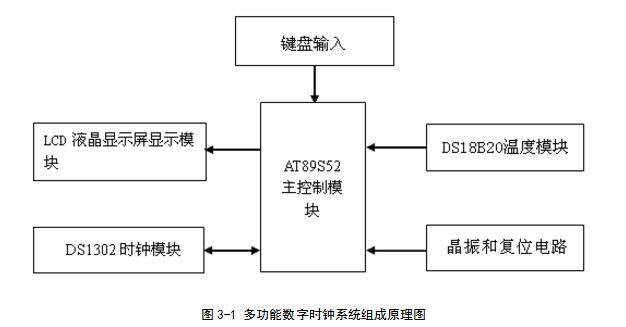

89C52单片机模块

模块结构框图和功能描述

模块结构框图如图:采用8位单片机89C52,时钟电路使用片内时钟振荡器,具有上电复位和手动按键复位功能,外接WDG复位电路。通过并行总线外扩

2010-12-17 21:55:09 245

245

245

245DS1904 实时时钟模块

DS1904 RTC的iButton ®是一个坚固的实时时钟模块,可以以最小的硬件访问。串行传输的数据由1 - Wire ®协议,只需一根数据线和一条地线

2011-04-28 10:25:41 2132

2132

2132

2132PIC单片机复位系统模块介绍

PIC16F87X系列单片机的复位功能设计得比较完善,根据引起 单片机 内部复位的条件和原因,可以将PIC单片机复位系统分为五个模块进行介绍: 1.上电复位 每次单片机加电时,上电复位

2011-06-23 11:12:54 2200

2200

2200

2200如何在XPS中调用HDL语言编写的模块

一直说要研究官方的例子XAP792,也确实在断断续续地学习着,现在硬件基本搞明白了,在公司也已经做出了测试画面。在搭建硬件平台的时候碰到了一些问题,本文要探讨的是这些问题当中比较重要的一个:如何在XPS中调用HDL语言编写的模块。

2017-02-09 09:31:07 1759

1759

1759

1759

基于MSP430F2的基础时钟模块

基础时钟模块支持低系统消耗和超低功耗。采用三种片内时钟信号,用户可以选择合适的性能和低功耗。基础时钟模块只需一个外部电阻、一个或两个外部晶体、或者用振荡器,通过软件控制。

2017-09-21 15:42:57 5

5

5

5msp430如何设置时钟及ad模块学习

我们在程序里对寄存器的设置,也就是对三个振荡器进行设置,时钟振荡器设置好了,还要对时钟模块进行设置,也就是让三个时钟模块MCLK SMCLK ACLK选择相应的时钟振荡器以得到不同频率的时钟。

2017-11-17 08:52:50 5656

5656

5656

5656

STM32F103的复位及时钟控制模块头文件

在处理器正常工作前,肯定要做一些初始化工作,其中最主要的一个就是初始化各种时钟。通过对STM32F103的复位及时钟控制(RCC)模块分析之后,自己写了一个RCC的头文件,这样使用起来更方便。头文件

2017-12-04 14:55:01 501

501

501

501单片机多功能数字时钟设计电路大全(五款单片机多功能数字时钟设计电路)

本文主要介绍了五款单片机多功能数字时钟设计电路。多功能数字时钟主要由显示模块、时钟模块、晶振和复位电路、键盘输入与温度模块组成。

2018-01-26 15:45:02 20147

20147

20147

20147

PIC单片机的复位系统模块与中断模块介绍

每次单片机加电时,上电复位电路都要对电源电压VDD的上升过程进行检测,当VDD值上升到规定值1.6~1.8V时,就产生一个有效的复位信号,需经过72ms加1024个时钟周期的延时,才会使单片机复位。

2019-10-16 16:41:41 2284

2284

2284

2284Spartan-6 FPGA芯片的时钟管理模块的介绍与使用说明

同步时序电路设计中最关键的是时钟设计, 随着电路规模与速度的提高, 对时钟的周期、占空比、延时和抖动等方面的要求也越来越高。为了顺应这需求, Spartan-6 系统器件在原有的DCM模块基础引入

2020-01-08 15:54:43 19

19

19

19K60微控制器系统时钟与其他功能模块

时钟产生模块将选定的时钟源分频,产生多种不同的时钟频率供多个模块使用。例如:总线时钟、FlexBus时钟等。多功能时钟发生器MCG模块为MCU提供了多种时钟源选择,内部包含了一个锁频环和一个锁相环,分别对内部参考时钟信号和外部时钟参考信号进行倍频。

2020-11-12 16:59:41 12

12

12

12【AutoSAR】【MCAL】MCU模块

一、MCU功能MCU(微控制器单元)驱动模块主要负责对微控制器的时钟控制,电源管理,复位,唤醒等进行控制。这些功能通常涉及整个MCU。The MCU driver提供如下服务:初始化MCU的时钟

2021-10-25 20:21:02 22

22

22

22MSP430单片机:时钟系统(UCS 模块)

UCS 模块支持低功耗UCS 软件配置后,只需要一两个晶振或者电阻,而不需要使用外部振荡器。UCS 模块最多含有 5 个时钟源: XT1CLKVLOCLKREFOCLKDCOCLKXT2CLKUCS 模块有三个时钟信号可以使用:ACLKMCLKSMCLKucs what?...

2021-11-19 15:36:07 10

10

10

10DS1302时钟模块使用讲解附带完整程序

后保证时钟正常运行)x1,x2外接32.768KHZ晶振GND接地RST复位引脚(低电平有效)I/O数据输入/输出引脚SCLK串行时钟输入引脚参考电路:如果是直接买的时钟模块的话,会直接引出VCC,GND,CLK,DAT,RST

2021-12-23 19:29:41 5

5

5

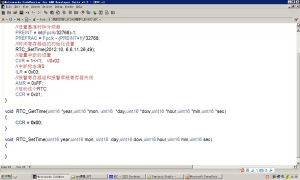

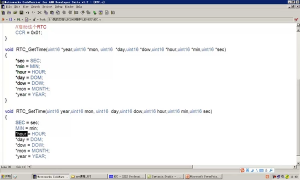

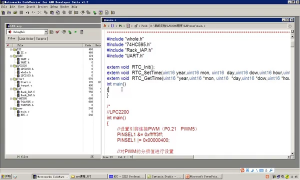

5基于STM8的IIC协议--实例篇--时钟模块(DS3231)读取

1. 综述 由上篇博客可知道IIC协议如何用代码实现,本篇博客就不涉及协议内容,只讲解如何使用。 本次的实验传感为:DS3231(时钟模块),对于时钟模块的具体信息我也就不多介绍,大家可以自行

2021-12-27 18:39:52 15

15

15

15STM32电源管理、复位、时钟

第二篇文章——STM32电源、复位、时钟电源管理电源电压调节器可编程电压监测器(PVD: Programmable voltage detector )低功耗模式复位Cortex-M3的复位信号

2022-01-05 14:25:10 10

10

10

10STM32学习100步之第五步——时钟、复位和电源管理

电压,有的则不可以承受5V电压。复位模块——上电复位:打开电源的时候,复位一次——可编程的电压检测器:当单片机工作电压低于某一个电压值的时候,复位一次,保证单片机的稳定工作。时钟模块(重点)...

2022-01-05 14:40:06 1

1

1

1STM32 时钟 复位和电源管理

电源管理-2.0 ~ 3.6V 供电和I/O引脚,引脚带FT标的兼容5V。复位上电/断电复位(POR/PDR),可编程电压监测器(PVD)(设定一个电压值,低于此电压时,单片机复位,保证系统工作稳定

2022-01-17 12:47:55 4

4

4

4ESP32使用PCF8563时钟模块进行网络校时

ESP32使用PCF8563时钟模块获取网络校时关于PCF8563时钟模块的介绍接线下载Arduino的PCF8563库关于PCF8563时钟模块的介绍最近在做基于 esp32的点阵时钟,于是对模块

2022-01-18 09:55:13 13

13

13

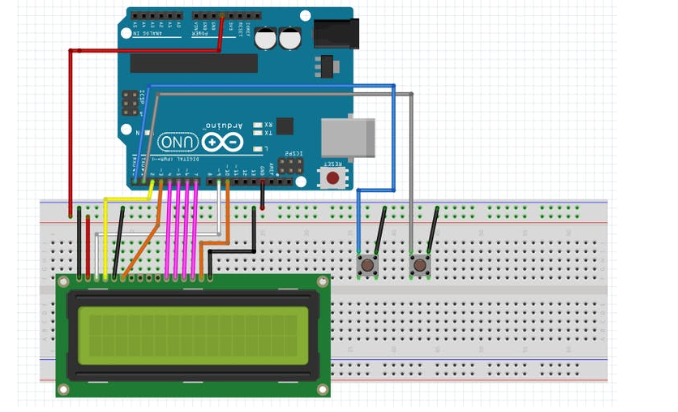

13如何利用Arduino UNO设计无RTC模块简单时钟

它只是一个由Arduino控制的简单数字时钟,无需使用任何RTC模块(实时时钟)。每次打开此时钟时,您都必须将其设置为当前时间,就像家庭中的模拟时钟一样。

2022-05-14 15:16:50 3403

3403

3403

3403

振弦采集模块复位( 重启)及恢复出厂设置

振弦采集模块复位( 重启)及恢复出厂设置 以下几种情况(或操作)可使模块产生复位动作,重新启动。 ( 1) 在模块正常工作期间,向寄存器 SYS_FUN 发送软复位指令 0x01; ( 2) 内核

2022-11-11 09:22:29 533

533

533

533

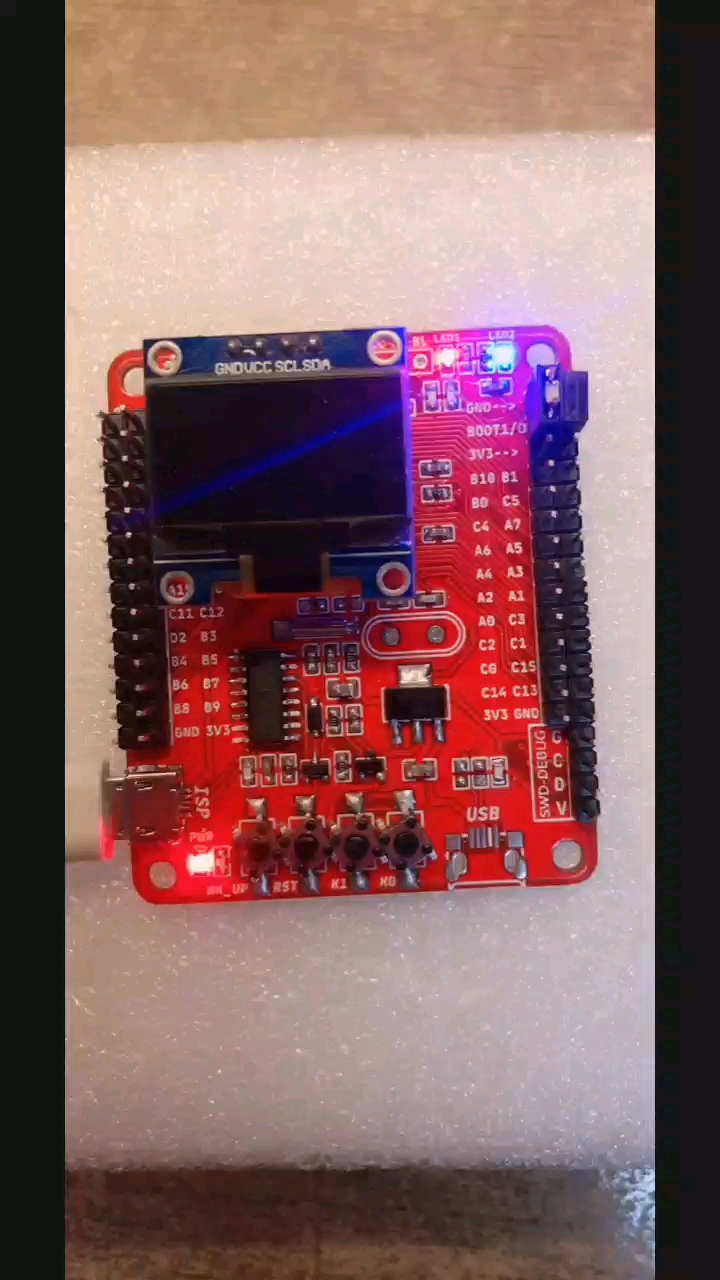

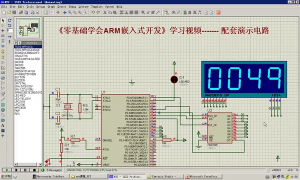

基于RTC模块的4位时钟

方案介绍我有一个带备用电池的DS1302实时时钟模块,我很想制作一个数字时钟。由于我还拥有7段4位数字显示屏,因此我正在寻找制作该时钟的最佳方法。但是我总是不愿意使用这种类型的显示器,因为它需要大量

2022-12-30 14:35:18 0

0

0

0PCF8563时钟模块

1.实时时钟模块,时钟芯片:PCF85632. 3.3V-5V电源3.绿色LED发光二极管电源指示灯4. IIC接口5.电路板尺寸:22mm×40mm6.型号:TR-11

2023-01-04 17:21:12 2

2

2

2一文简析TC3xx Rest/Clock/Watch模块

在时钟系统部分主要介绍时钟源选择,PLL倍频配置,时钟分发等内容。在看门狗模块部分主要介绍了开门狗复位的触发路径,看门狗模块的工作原理,CPU EndInit/Safe EndInit的实现原理等内容。

2023-02-21 13:46:58 5786

5786

5786

5786SpinalHDL BlackBox时钟与复位

在SpinalHDL中使用之前已有的Verilog等代码的时候需要将这些代码包在一个BlackBox里面,但是如果这些代码里面有时钟和复位,我们需要怎么将时钟和复位端口和SpinalHDL中已有的时钟域连接起来呢?

2023-05-04 11:13:14 489

489

489

489

xilinx FPGA复位方法讲解

能不复位尽量不用复位,如何判断呢?如果某个模块只需要上电的时候复位一次,工作中不需要再有复位操作,那么这个模块可以不用复位,用上电初始化所有寄存器默认值

2023-06-28 14:44:46 526

526

526

526

基于模块时间计算 CPU 时钟的本地时间

说明 可以使用该指令读取 CPU 时钟的当前日期和当前时间(模块时间)。 在此指令的 OUT 输出参数中输出读取的日期。得出的值不包含有关本地时区或夏令时的信息。 说明 CPU 时钟的模块时间

2023-06-28 16:18:01 508

508

508

508

全新C8系列实时时钟模块现已发布

近日,Micro Crystal 瑞士微晶公司推出了全新的 C8 系列超小型实时时钟模块,这款模块的设计初衷是致力于满足极小尺寸和轻量级设计的需求。 新发布的 C8 系列首批两款实时时钟模块为电子

2023-08-04 09:26:29 480

480

480

480lora Pro系列数传模块及各版本数传模块选型比

数传电台LoRa Pro模块是思为无线推出的一系列升级版mesh组网无线通讯数传模块。本系列模块有AES数据加密及上电复位自检功能。可通过配置与我司之前LoRa 数传模块兼容互通。其中lora611Pro数传模块已获得KC认证,思为无线也提供其它数传模块的认证服务及产品定制化服务。

2023-11-14 17:28:43 234

234

234

234

RX-8731LC (内置EEPROM,ID-ROM I2C-Bus接口实时时钟模块)

RX-8731LC 时钟模块是EPSON/爱普生的一款额定频率32.768KHz,接口为I2C-Bus,月偏差为±60 s的实时时钟模块,VSOJ-12脚封装实时时钟模块,12脚贴片,具有小尺寸

2024-01-30 15:57:55 0

0

0

0RX-4571LC、NB、SA实时时钟模块

RX-4571LC实时时钟模块是EPSON推出的一求款额定频率32.768KHz,接口为SPI(3-wire),月偏差为±60 s的实时时钟模块,12脚贴片,具有小尺寸,高稳定性。该款实时时钟模块

2024-01-31 11:46:22 0

0

0

0 电子发烧友App

电子发烧友App

评论