FPGA/ASIC技术

电子发烧友本栏目为FPGA/ASIC技术专栏,内容有fpga培圳资料、FPGA开发板、FPGA CPLD知识以及FPGA/ASIC技术的其它应用等;是您学习FPGA/ASIC技术的好栏目。Nexys3学习手记8:FT232之高速UART

继续上一节的工程,这里要接着在XPS上扩展一个UART外设,配合板载的USB2UART芯片FT232R做个高速串口传输测试。 ...

2017-02-11 5276

FPGA verilog实现的1602时钟计数器

网上很少用人公开这一类代码,一搜FPGA 1602,都是写一个静态的显示,在实际应用中,是没有用的,因此这个简单的例子,给大家抛砖引玉了!...

2017-02-11 2146

如何使用PlanAhead/Adept加速管脚排布

在排布FPGA管脚生成ucf文件的过程中,当FPGA管脚较多的时候,手工排布管脚不仅效率低,而且很容易出错。借助PlanAhead和Adept等工具,可以很方便快速的实现管脚排布。...

2017-02-11 2169

QII中的几个Warning的解决方法

前几天看网上一个人说在仿经典基础程序按键消抖实验的时候0 error、0 warning,正好我也在仿这个实验,就想说看看我能不能也出现这样爽的结果,没想到最后出了6个warning,于是施展搜索大法,...

2017-02-11 2313

verilog语言实现任意分频

原文出自:分频器是指使输出信号频率为输入信号频率整数分之一的电子电路。在许多电子设备中如电子钟、频率合成器等,需要各种不同频率的信号协同工作,常用的方法是以稳定度高的晶体...

2017-02-11 14798

组合逻辑设计中的毛刺现象

和所有的数字电路一样,毛刺也是FPGA电路中的棘手问题,它的出现会影响电路工作的稳定性,可靠性,严重时会导致整个数字系统的误动作和逻辑紊乱。...

2017-02-11 2421

Linux2.4.26内核在Virtex II Pro开发板上的移植

下载Crosstoolcrosstool-在网上可以很容易找到,#tar zxvf crosstool-0.43.tar.gz#cd crosstool-0.43#vim demo-powerpc-405.sh 修改脚本TARBALLS_DIR=/home/yaoq/crosstool-0.43...

2017-02-11 898

FPGA管脚分配时需注意的一些事项

设计过FPGA的原理图,看FPGA的手册,说管脚的分配问题,如时钟管脚要用GC类管脚,而且单端时钟输入时要用P类型的管脚,不能用N类型管脚等等。...

2017-02-11 12725

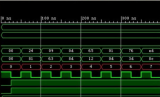

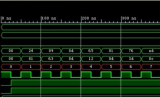

深入分析verilog阻塞和非阻塞赋值

学verilog 一个月了,在开发板上面写了很多代码,但是始终对一些问题理解的不够透彻,这里我们来写几个例子仿真出阻塞和非阻塞的区别...

2017-02-11 1818

FPGA设计全流程:ModelsimSynplify.ProISE

介绍如何编译HDL必须的Xilinx库和结构仿真。创建将被编译库的目录在编译库之前,最好先建立一个目录(事实上必须建立一个目录),步骤如下...

2017-02-11 1610

基于Xilinx FPGA的通用信号采集器

上一篇写了基于Xilinx FPGA的通用信号发生器的案例,反响比较好,很多朋友和我探讨相关的技术,其中就涉及到信号的采集,为了使该文更有血有肉,我在写一篇基于Xilinx FPGA的通用信号采集器...

2017-02-11 2191

基于System Generator的FPGA开发总结

前一阵一直在忙,所以没有来得及写博文。弄完杂七杂八的事情,又继续FPGA的研究。使用Verilog HDL语言和原理图输入来完成FPGA设计的方法都试验过了,更高级的还有基于System Generator和基于EDK...

2017-02-11 8771

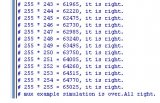

8位无符号数乘法运算HDL设计实例

加减乘除是运算的基础,也是我们在小学课堂里的重点必修课。乘除运算虽然对于我们今天来说还是小菜一碟,让计算机做起来也是九牛一毛不足挂齿,但是要真探究一下计算机是如何完乘除运...

2017-02-11 9574

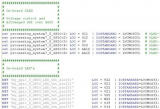

cordic算法verilog实现(复杂版)

module cordic (clk,rst_n,ena,phase_in,sin_out,cos_out,eps); parameter DATA_WIDTH=8; parameter PIPELINE=8; ...

2017-02-11 4943

cordic算法verilog实现(简单版)

cordic算法verilog实现(简单版)(转载)module cordic(clk, phi, cos, sin); parameter W = 13, W_Z = 14; input clk; input [W_Z-1:0] phi; output[W-1:0] ...

2017-02-11 3618

7 FPGA SATA3.0 6Gbps Host IP通过UNH

IntelliProp的SATA 6Gb/s Host IP核刚刚在新罕布什尔大学互通测试实验室(UNH-IOL)通过认证测试。...

2017-02-11 3516

借助Intel i7 处理器和 Xilinx FPGA实现的开放式毫米波测试平台

美国国家仪器公司(NI)和德国德累斯顿工业大学开展合作,通过世界上第一台开放式毫米波测试平台来拓展德累斯顿5G实验室(D5GL),该测试平台能实时处理超过2GHz的RF(射频)信号,可以作...

2017-02-11 1322

ZedBoard学习手记(四)为使用Linux系统做准备

裸机控制外设是非常简单的,与普通的单片机并无二异,但仅仅有裸奔代码还远远无法发挥Cortex-A9硬核的作用,毕竟Zynq芯片集成了一颗最高能跑到1GHz的双核CPU(ZedBoard上的XC7Z020只能到800MHz)。...

2017-02-11 2517

ZedBoard学习手记(三)为自定义外设编写裸奔控制软件

由于Xilinx已经为我们做了大部分的铺垫工作,因此裸奔控制外设这一步就显得十分简单了,如果不用Linux和图形界面显示,大概我的作品早早的就完成了吧。...

2017-02-11 1280

ZedBoard学习手记(二) 开发自定义AXI总线外设IP核

想要发挥ZYNQ芯片的特长,让整个系统协同工作起来,就需要将PS与PL两部分结合在一起,在Cortex-A9核和FPGA逻辑资源之间建立通信的通道,这条通道就是AXI总线。...

2017-02-11 4478

Xilinx DDR3控制器接口带宽利用率测试(四

描述:在此项测试中,发起四次读写访问,其中读写操作分别间隔开,四次读写操作访问的地址都是同一个,由此观察读写切换引入的带宽开销。...

2017-02-11 6236

Xilinx DDR3控制器接口带宽利用率测试(三)

描述:在此项测试中,每个Bank只访问一次,接着依次访问其它Bank。DDR3有限制在一定时间内可以输入的Bank打开指令个数,即在一定时间内只允许输入最多4个Bank打开命令。...

2017-02-11 4778

Xilinx DDR3控制器接口带宽利用率测试(二)

描述:单Bank内行切换时,每次打开一个Row,进行一次写操作以后,必须重新打开另外一个Row,才能进行该Row的写操作。两个Row打开操作有时间间隙要求,打开Row到写操作也有时间间隙要求。...

2017-02-11 3245

ZedBoard学习手记(十) 图形界面控制ZedBoard硬件

今天所讨论的内容就是通过QT开发的GUI软件来控制ZedBoard板上的硬件外设,完整的信号链如下:QT GUI → Linux Driver → AXI Bus → My_GPIO Peripheral → LED & Switch首先在QT Creator中建立一个QT GUI工程,命名...

2017-02-11 3024

ZedBoard学习手记(九) 在ZedBoard上运行QT图形软件

在Zynq平台上运行QT其实与PC无异,都需要相应的执行环境,只不过PC上的QT Lib可以使用QT SDK自动安装配置,而Zynq平台上的QT Lib则需要手动安装。...

2017-02-11 1762

ZedBoard学习手记(八) 更大的目标!

在Linux下做GUI,比较简单的方法是使用QT。QT一直被用于跨平台的应用程序开发,之前属于Nokia,现在被卖给了Digia,开源版本的主页是。...

2017-02-11 1351

编辑推荐厂商产品技术软件/工具OS/语言教程专题

| 电机控制 | DSP | 氮化镓 | 功率放大器 | ChatGPT | 自动驾驶 | TI | 瑞萨电子 |

| BLDC | PLC | 碳化硅 | 二极管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 无刷电机 | FOC | IGBT | 逆变器 | 文心一言 | 5G | 英飞凌 | 罗姆 |

| 直流电机 | PID | MOSFET | 传感器 | 人工智能 | 物联网 | NXP | 赛灵思 |

| 步进电机 | SPWM | 充电桩 | IPM | 机器视觉 | 无人机 | 三菱电机 | ST |

| 伺服电机 | SVPWM | 光伏发电 | UPS | AR | 智能电网 | 国民技术 | Microchip |

| 开关电源 | 步进电机 | 无线充电 | LabVIEW | EMC | PLC | OLED | 单片机 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 蓝牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太网 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 语音识别 | 万用表 | CPLD | 耦合 | 电路仿真 | 电容滤波 | 保护电路 | 看门狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 阈值电压 | UART | 机器学习 | TensorFlow |

| Arduino | BeagleBone | 树莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 华秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |