针对不同类型的器件,Xilinx公司提供的全局时钟网络在数量、性能等方面略有区别,下面以Virtex-4系列芯片为例,简单介绍FPGA全局时钟网络结构。

2013-11-28 18:49:00 14294

14294

时钟网络反映了时钟从时钟引脚进入FPGA后在FPGA内部的传播路径。

2019-09-10 15:12:31 7150

7150

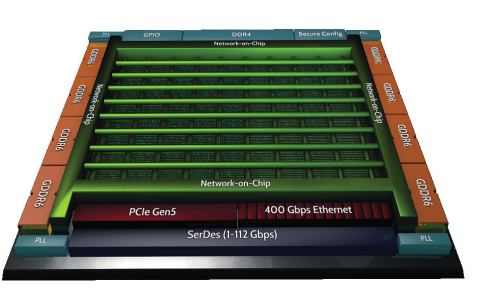

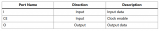

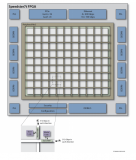

Achronix 最新基于台积电(TSMC)的7nm FinFET工艺的Speedster7t FPGA器件包含了革命性的新型二维片上网络(2D NoC)。

2020-02-27 17:08:41 2288

2288 在多时钟设计中可能需要进行时钟的切换。由于时钟之间可能存在相位、频率等差异,直接切换时钟可能导致产生glitch。

2020-09-24 11:20:38 6410

6410

01、如何决定FPGA中需要什么样的时钟速率 设计中最快的时钟将确定 FPGA 必须能处理的时钟速率。最快时钟速率由设计中两个触发器之间一个信号的传输时间 P 来决定,如果 P 大于时钟周期 T,则

2020-11-23 13:08:24 4644

4644

EFX_GBUFCE既可以让GPIO走全局时钟网络也可以用于为时钟添加使能控制,当并不是随时需要该时钟时可以把时钟禁止以节省功耗。

2023-05-12 09:53:38 1407

1407

本文主要介绍Xilinx FPGA的GTx的参考时钟。下面就从参考时钟的模式、参考时钟的选择等方面进行介绍。

2023-09-15 09:14:26 5117

5117

有一个有趣的现象,众多数字设计特别是与FPGA设计相关的教科书都特别强调整个设计最好采用唯一的时钟域。

2023-12-22 09:04:46 2675

2675

生成时钟包括自动生成时钟(又称为自动衍生时钟)和用户生成时钟。自动生成时钟通常由PLL或MMCM生成,也可以由具有分频功能的时钟缓冲器生成如7系列FPGA中的BUFR、UltraScale系列

2024-01-11 09:50:09 3808

3808

与HBM DRAM堆叠裸片之间对高带宽连接的需求。本文将深入探讨UCIe支持的不同接口,以实现片上网络(NoC)互连。

2025-08-04 15:17:24 2452

2452 2D NoC如同在FPGA可编程逻辑结构上运行的高速公路网络一样,为FPGA外部高速接口和内部可编程逻辑的数据传输提供了超高带宽。

2021-11-11 14:20:14 3561

3561

FPGA 时钟分配网络设计技术

2012-08-20 17:15:27

本帖最后由 lee_st 于 2017-10-31 08:58 编辑

FPGA多时钟设计

2017-10-21 20:28:45

大型设计中FPGA 的多时钟设计策略Tim Behne 软件与信号处理部经理 Microwave Networks 公司Email: timothyb@microwavenetworks.com利用

2012-10-26 17:26:43

利用FPGA实现大型设计时,可能需要FPGA具有以多个时钟运行的多重数据通路,这种多时钟FPGA设计必须特别小心,需要注意最大时钟速率、抖动、最大时钟数、异步时钟设计和时钟/数据关系。设计过程中最重要的一步是确定要用多少个不同的时钟,以及如何进行布线?

2019-08-30 08:31:41

FPGA的多时钟系统设计 Multiple Clock System Design Clk1and Clk2are the clock which running at different frequency[/hide]

2009-12-17 15:46:09

,拜托大家了!

FPGA系统设计中,如果用两个FPGA工作,应该如何设计两片之间的通信?从片的配置和时钟输入与主片有何不同

2023-04-23 11:31:45

FPGA系统设计中,如果用两个FPGA工作,应该如何设计两片之间的通信?从片的配置和时钟输入与主片有何不同?一个做主片用于数据处理和控制,一个做从片用于IO扩展。硬件和软件上应该如何设计两片之间

2023-05-08 17:18:25

采用FPGA来设计一款广泛应用于计算机、Modem、数据终端以及许多其他数字设备之间的数据传输的专用异步并行通信接口芯片,实现了某一时钟域(如66 MHz)的8位并行数据到另一低时钟域(如40 MHz)16

2011-09-07 09:16:40

片上网络的研究才刚刚起步,还没有在商业产品中广泛应用。片上网络的标准化可以增加组件的互连性,但会造成性能的损失,而对特定的片上系统,性能是片上系统的一个关键因素。

2019-09-19 09:10:34

网络基础集(解决上网常见问题)

2009-06-11 15:37:25

利用 FPGA 实现大型设计时,可能需要FPGA 具有以多个时钟运行的多重数据通路,这种多时钟 FPGA 设计必须特别小心,需要注意最大时钟速率、抖动、最大时钟数、异步时钟设计和时钟/数据关系

2012-03-05 14:42:09

跨越时钟域FPGA设计中可以使用多个时钟。每个时钟形成一个FPGA内部时钟域“,如果需要在另一个时钟域的时钟域产生一个信号,需要特别小心。隧道四部分第1部分:过路处。第2部分:道口标志第3部分:穿越

2012-03-19 15:16:20

求关于片上网络各个ip核之间的热阻和功耗对io核温度的影响,最好具体到公式表达

2017-04-30 00:16:32

在FPGA 上设计一个高性能、灵活的、面积小的通信体系结构是一项巨大的挑战。大多数基于FPGA 的片上网络都是运行在一个单一时钟下。随着FPGA 技术的发展,Xilinx 公司推出了Virtex-4

2019-08-21 06:47:43

【作者】:李晓辉;曹阳;王力纬;陈晨;【来源】:《华中科技大学学报(自然科学版)》2010年03期【摘要】:针对虚通道技术导致片上网络(NoC)面积增加的问题,提出了一种基于遗传算法的NoC虚通道

2010-04-22 11:34:25

本帖最后由 mingzhezhang 于 2012-5-23 20:05 编辑

大型设计中FPGA的多时钟设计策略 利用FPGA实现大型设计时,可能需要FPGA具有以多个时钟运行的多重

2012-05-23 19:59:34

利用FPGA实现大型设计时,可能需要FPGA具有以多个时钟运行的多重数据通路,这种多时钟FPGA设计必须特别小心,需要注意最大时钟速率、抖动、最大时钟数、异步时钟设计和时钟/数据关系。设计过程中

2015-05-22 17:19:26

NoC为FPGA设计提供了哪些优势?NoC在FPGA内部逻辑互连中发挥的作用是什么?如何利用片上高速网络创新地实现FPGA内部超高带宽逻辑互连?

2021-06-17 11:35:28

对多时钟系统的同步问题进行了讨论å提出了亚稳态的概念及其产生机理和危害;叙述了控制信号和数据通路在多时钟域之间的传递õ讨论了控制信号的输出次序对同步技术的不同要求,重点论述了常用的数据通路同步技术----用FIFO实现同步的原理及其实现思路

2012-05-23 19:54:32

AD怎么让走线带上网络呢?

2019-09-11 05:36:36

采用片上网络(NoC)的新型FPGA数据架构赋能5G网络和数据中心智能网卡(SmartNIC)设计方案

2021-02-22 08:01:25

大型设计中FPGA的多时钟设计策略利用FPGA实现大型设计时,可能需要FPGA具有以多个时钟运行的多重数据通路,这种多时钟FPGA设计必须特别小心,需要注意最大时钟速率、抖动、最大时钟数、异步时钟

2020-04-26 07:00:00

1、高级FPGA设计技巧 有一个有趣的现象,众多数字设计特别是与FPGA设计相关的教科书都特别强调整个设计最好采用唯一的时钟域。换句话说,只有一个独立的网络可以驱动一个设计中所有触发器的时钟端口

2022-10-14 15:43:00

与FPGA中的普通路由相比,使用片上网络来互连DSP48A会降低性能吗?以上来自于谷歌翻译以下为原文Will the use of network on chip to interconnect

2019-06-28 09:39:03

有一个有趣的现象,众多数字设计特别是与FPGA设计相关的教科书都特别强调整个设计最好采用唯一的时钟域。换句话说,只有一个独立的网络可以驱动一个设计中所有触发器的时钟端口。虽然这样可以简化时序分析以及

2023-06-02 14:26:23

Multiple Clock System Design PLD设计技巧—多时钟系统设计

Information Missing

Max+Plus II does

2008-09-11 09:19:41 25

25 网络基础集+解决上网常见问题:

2009-06-11 15:15:47 25

25 一种FPGA时钟网络中锁相环的实现方案:摘 要:本文阐述了用于FPGA 的可优化时钟分配网络功耗与面积的时钟布线结构模型。并在时钟分配网络中引入数字延迟锁相环减少时钟偏差,探

2009-08-08 09:07:22 25

25 半导体技术的飞速发展推动了片上系统设计进入到片上网络阶段。为了进一步研究其结构及不同工艺对其的影响,文章分析了片上网络对于片上系统的优越性,并针对其重要组成

2009-08-21 09:03:08 12

12 该文建立了一种面向应用设计的片上网络的性能分析模型,并在此基础上提出了片上缓存优化策略和分配算法。在硬件实现平台上的仿真表明,该文建立的片上网络分析模型能很好

2009-11-18 15:20:06 9

9 随着芯片上晶体管数量发展到10亿数量级,功耗逐渐成为芯片设计的首要制约因素。本文分别从CMOS电路和网络通讯两个层面上来分析片上网络(NoC)的功耗,并给出了相应的功耗

2009-12-14 09:51:17 6

6 本文参照传统的OSI(Open Systems Interconnection)模型与TCP/IP 模型对片上网络系统模型层次结构进行了按照片上网络特点进行的划分。文中还对片上网络的网络层设计中的各种拓扑结

2009-12-14 09:54:49 8

8 半导体技术的快速发展以及芯片上系统应用复杂度的不断增长,使得片上互连结构的吞吐量、功耗、延迟以及时钟同步等问题更加复杂,出现了将通信机制与计算资源分离的片上网络。

2010-02-24 11:55:49 17

17 半导体技术的飞速发展推动了片上系统设计进入到片上网络阶段。为了进一步研究其结构及不同工艺对其的影响,文章分析了片上网络对于片上系统的优越性,并针对其重要组成部

2010-07-17 16:53:50 19

19 半导体技术的快速发展以及芯片上系统应用复杂度的不断增长,使得片上互连结构的吞吐量、功耗、延迟以及时钟同步等问题更加复杂,出现了将通信机制与计算资源分离的片上网络。

2010-07-17 16:56:32 33

33 针对片上网络的死锁问题,提出一种片上网络自适应路由算法——虚拟网络(VN)路由算法,该算法根据报文源地址和目的地址将网络分成4个虚拟网络。一旦报文在某个给定的虚拟

2010-07-21 16:09:40 13

13 本文阐述了用于FPGA的可优化时钟分配网络功耗与面积的时钟布线结构模型。并在时钟分配网络中引入数字延迟锁相环减少时钟偏差,探讨了FPGA时钟网络中锁相环的实现方案。

2010-08-06 16:08:45 12

12 大型设计中FPGA的多时钟设计策略

利用FPGA实现大型设计时,可能需要FPGA具有以多个时钟运行的多重数据通路,这种多时钟FPGA设计必须特别小心,需要注意最大时钟速率

2009-12-27 13:28:04 827

827

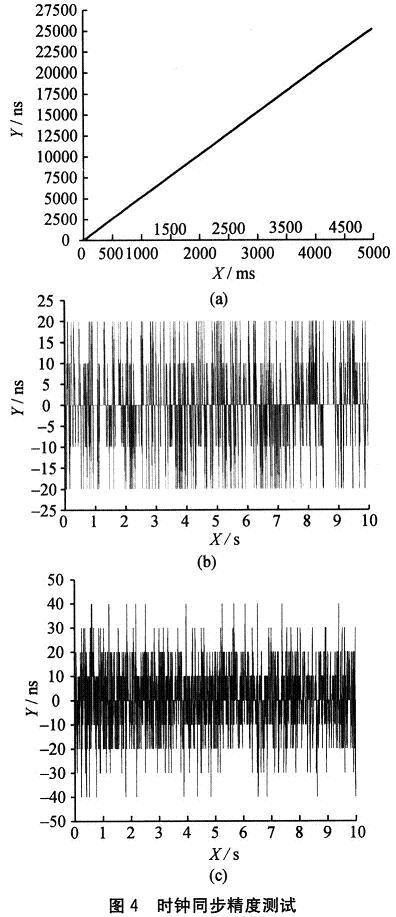

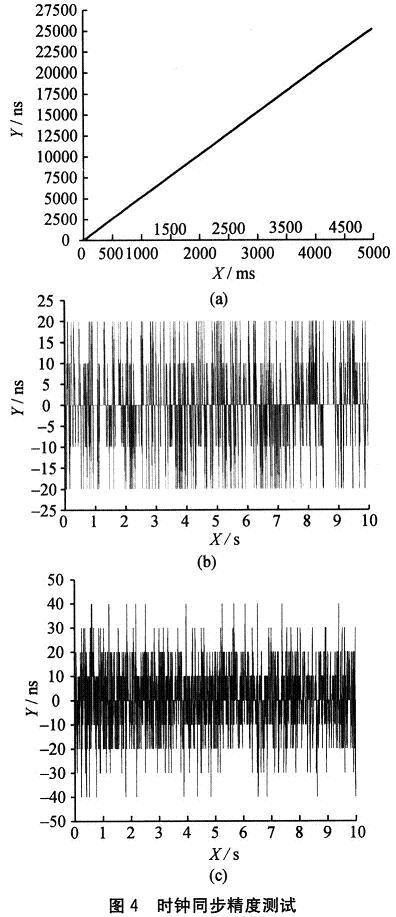

FPGA的时钟频率同步设计

网络化运动控制是未来运动控制的发展趋势,随着高速加工技术的发展,对网络节点间的时间同步精度提出了更高的要求。如造纸机械,运行速

2010-01-04 09:54:32 3161

3161

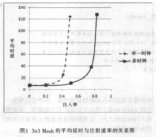

1 多时钟片上网络架构的分析

片上网络结构包含了拓扑结构、流量控制、路由、缓冲以及仲裁。选择合适网络架构方面的元素,将对片上网络的性能产生重大影响[2]

2010-09-02 09:43:47 1061

1061

为提高芯片验证与测试的可靠性,针对片上网络核心芯片的结构特点,设计出一种基于宿主机/目标机通信模式的测试系统。重点描述了测试系统软硬件的设计与实现,并采用Stratix系列FPGA芯片进行原型测试和验证。实验结果表明,该系统可对芯片的复位、实现功能及

2011-01-15 15:46:29 31

31 本文将探讨FPGA时钟分配控制方面的挑战,协助开发团队改变他们的设计方法,并针对正在考虑如何通过缩小其时钟分配网络的规模来拥有更多的FPGA I/O,或提高时钟网络性能的设计者们

2011-03-30 17:16:32 1241

1241

本内容介绍了分级环片上网络互连

2011-05-19 15:37:33 21

21 从建立功耗模型出发, 在集成电路不同的设计层次、片上网络通讯功耗以及NoC 映射问题等方面来讨论NoC 的低功耗设计, 综合了现有功耗解决的最新方案, 对NoC 的功耗研究做了一个比

2011-06-30 09:32:17 1471

1471 在FPGA设计中,为了成功地操作,可靠的时钟是非常关键的。设计不良的时钟在极限的温度、电压下将导致错误的行为。在设计PLD/FPGA时通常采用如下四种类型时钟:全局时钟、门控时钟

2011-09-21 18:38:58 4131

4131

世界头号片上通信IP供应商Sonics公司(R)今天面向高级并发应用处理和系统级设计推出了业内首款GHz级片上网络(NOC)SonicsGN(TM)(SGN)。

2011-09-22 18:09:17 2000

2000 基于AD9540产生多时钟输出

2011-11-25 00:02:00 31

31 麻省理工学院(MIT)的研究人员指出,今天我们都在使用片上总线和环状拓朴,但它们所带来的麻烦可能要比它们能贡献的价值还要多,这也推动了片上网状网络(on-chip mesh networ

2012-04-18 08:39:53 605

605 利用FPGA实现大型设计时,可能需要FPGA具有以多个时钟运行的多重数据通路,这种多时钟FPGA设计必须特别小心,需要注意最大时钟速率、抖动、最大时钟数、异步时钟设计和时钟/数

2012-05-21 11:26:10 1591

1591

通过分析流水线结构和单周期结构的片上网络路由器,提出了一种低延时片上网络路由器的设计,并在SMIC 0.13um Mixed-signal/RF 1.2V/3.3V工艺进行流片验证。芯片测试结果表明,该路由器可以

2013-06-25 16:25:01 40

40 为了实现软硬件协同设计和提高仿真速度的需求,采用SystemC语言的建模方法,通过对片上网络体系结构的研究,提出了一种片上网络的建模方案,并对一个mesh结构完成了SystemC的建模设

2013-07-30 11:46:44 42

42 FPGA学习资料,有兴趣的同学可以下载看看。

2016-04-07 16:33:47 0

0 多核密码处理器中的片上网络互连结构研究_杜怡然

2017-01-03 18:00:37 0

0 如何正确使用FPGA的时钟资源

2017-01-18 20:39:13 22

22 当Xilinx 7Series FPGA中,存在3种主要的时钟网络:BUFG,BUFR,BUFIO以及他们所衍生出的各种变种。那么他们有什么主要特点和区别呢? BUFIO是IO时钟网络,顾名思义,它

2017-02-08 05:31:40 3409

3409

片上网络Network-on-chip (NoC) 是一种应用于大规模集成电路(VLSI)系统中的,一种新的片上系统(System-on-chip)的设计方法。

2017-02-11 06:39:13 1952

1952

在一个SOC设计中,存在多个、独立的时钟,这已经是一件很平常的事情了。大多数的SOC器件都具有很多个接口,各个接口标准都可能会使用完全不同的时钟频率。

2017-02-11 15:07:11 1522

1522 网络拓扑:在设计中,选择Mesh拓扑结构。Mesh结构拥有最小的面积开销以及低功耗的特点。此外,Mesh的线性区的节点数量规模大以及通道较宽。同时,Mesh也能很好地映射到FPGA下的底层路由结构,降低了FPGA 逻辑拥塞和路由器的功耗。

2018-07-22 09:44:00 2593

2593

很大。 在设计PLD/FPGA时通常采用几种时钟类型。时钟可分为如下四种类型:全局时钟、门控时钟、多级逻辑时钟和波动式时钟。多时钟系统能够包括上述四种时钟类型的任意组合。

2017-11-25 09:16:01 5020

5020

上的设备在通信时对总线的独占性以及单一系统总线对同步时钟的要求,使得在片上IP核越来越多的芯片中,不可避免地存在通信效率低下、全局同步时钟开销大等问题。 片上网络NoC(Network on Chip)的提出有效地解决了上述问题。该系统借鉴了计算机网络中分组交换的通

2017-11-30 07:57:21 718

718

针对将计算任务合理地映射到三维片上网络( NoC)的问题,提出了一种基于遗传算法(GA)的改进算法。GA具有快速随机的搜索能力,Prim算法可在加权连通图内得到最小生成树,改进算法结合了两种算法

2017-12-07 14:40:49 0

0 根据计算趋近数据的原则,提出面向MPI集合操作的定制化片上网络设计方法,通过增强现有片上路由器的硬件功能实现MPI集合操作在网络层的加速。设计MPI归约操作,将其扩展至多种集合操作,并与一种针对

2018-02-02 15:46:50 0

0 在CPU-GPU异构系统架构中,由于GPU程序的多线程特点,大多数GPU程序会垄断系统中的共享资源,例如片上网络。这将给CPU程序的性能造成很大的损失。我们发现有一些GPU程序性能对网络延迟表现

2018-04-26 16:33:13 1

1 跨时钟域问题(CDC,Clock Domain Crossing )是多时钟设计中的常见现象。在FPGA领域,互动的异步时钟域的数量急剧增加。通常不止数百个,而是超过一千个时钟域。

2019-08-19 14:52:58 3895

3895 移动网络上网与WiFi连接上网,是移动设备上的两大高手。一个主室外, 一个主室内。WiFi上网是移动网络的室内覆盖补充。WiFi迟早将被淘汰的言论层出不穷。下面我们从耗电、速度、经济、安全等方面来说说。

2020-03-21 15:06:04 16654

16654 有一个有趣的现象,众多数字设计特别是与FPGA设计相关的教科书都特别强调整个设计最好采用唯一的时钟域。

2020-09-24 10:20:00 3603

3603

时钟网络反映了时钟从时钟引脚进入FPGA后在FPGA内部的传播路径。 报告时钟网络命令可以从以下位置运行: A,VivadoIDE中的Flow Navigator; B,Tcl命令

2020-11-29 09:41:00 3695

3695 利用 FPGA 实现大型设计时,可能需要FPGA 具有以多个时钟运行的多重数据通路,这种多时钟FPGA 设计必须特别小心,需要注意最大时钟速率、抖动、最大时钟数、异步时钟设计和时钟/数据关系。设计过程中最重要的一步是确定要用多少个不同的时钟,以及如何进行布线,本文将对这些设计策略深入阐述。

2021-01-15 15:57:00 14

14 AN-769: 基于AD9540产生多时钟输出

2021-03-18 23:03:12 2

2 引言:本文我们介绍一下全局时钟资源。全局时钟是一个专用的互连网络,专门设计用于到达FPGA中各种资源的所有时钟输入。这些网络被设计成具有低偏移和低占空比失真、低功耗和改进的抖动容限。它们也被设计成

2021-03-22 10:09:58 14973

14973

半导体制造工艺的快速发展使得片上可以集成更大规模的硬件资源,片上网络的研究试图解决芯片中全局通信问题,

2021-03-24 16:49:15 3700

3700 半导体制造工艺的快速发展使得片上可以集成更大规模的硬件资源,片上网络的研究试图解决芯片中全局通信问题,

2021-03-24 16:41:57 4779

4779 有一个有趣的现象,众多数字设计特别是与FPGA设计相关的教科书都特别强调整个设计最好采用唯一的时钟域。换句话说,只有一个独立的网络可以驱动一个设计中所有触发器的时钟端口。虽然这样可以简化时序分析以及

2021-05-10 16:51:39 4652

4652

三维片上网络是解决片上网络通讯瓶颈的重要途径,拓扑结构是三维片上网络研究中的关键问题。针对高维超立方拓扑结构节点度迅速増加,岀现通讯瓶颈的问题,提岀一种髙维超立方裂变拓扑结构,该拓扑在同等网络规模下

2021-05-11 17:00:54 9

9 三维混合无线片上网络架构及路由算法

2021-06-03 14:28:36 7

7 有一个有趣的现象,众多数字设计特别是与FPGA设计相关的教科书都特别强调整个设计最好采用唯一的时钟域。换句话说,只有一个独立的网络可以驱动一个设计中所有触发器的时钟端口。虽然这样可以简化时序分析以及

2021-09-23 16:39:54 3632

3632 1. 概述 Achronix 最新基于台积电(TSMC)的7nm FinFET工艺的Speedster7t FPGA器件包含了革命性的新型二维片上网络(2D NoC)。2D NoC如同在FPGA

2021-11-12 09:21:22 2972

2972

xilinx 的 FPGA 时钟结构,7 系列 FPGA 的时钟结构和前面几个系列的时钟结构有了很大的区别,7系列的时钟结构如下图所示。

2022-07-03 17:13:48 4699

4699 ASIC 和FPGA芯片的内核之间最大的不同莫过于时钟结构。ASIC设计需要采用诸如时钟树综合、时钟延迟匹配等方式对整个时钟结构进行处理,但是 FPGA设计则完全不必。

2022-11-23 16:50:49 1249

1249

假如给定FPGA内的时钟没有正确运行,那么我们多片FPGA系统的整体将不能同时启动,这将有可能是致命的。

2023-05-22 09:21:24 621

621

有一个有趣的现象,众多数字设计特别是与FPGA设计相关的教科书都特别强调整个设计最好采用唯一的时钟域。换句话说,只有一个独立的网络可以驱动一个设计中所有触发器的时钟端口。虽然这样可以简化时序分析以及

2023-08-23 16:10:01 1372

1372 FPGA 中包含一些全局时钟资源。以AMD公司近年的主流FPGA为例,这些时钟资源由CMT(时钟管理器)产生,包括DCM、PLL和MMCM等。

2024-04-25 12:58:30 3304

3304

电子发烧友App

电子发烧友App

评论