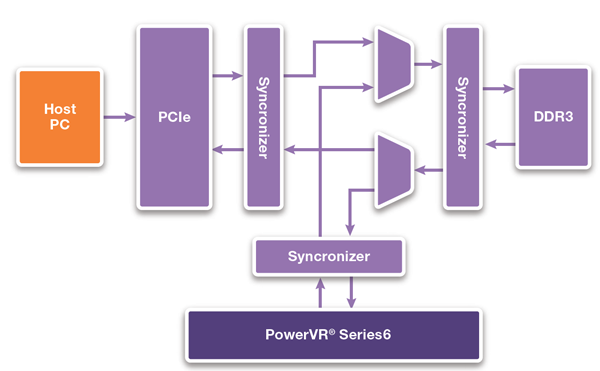

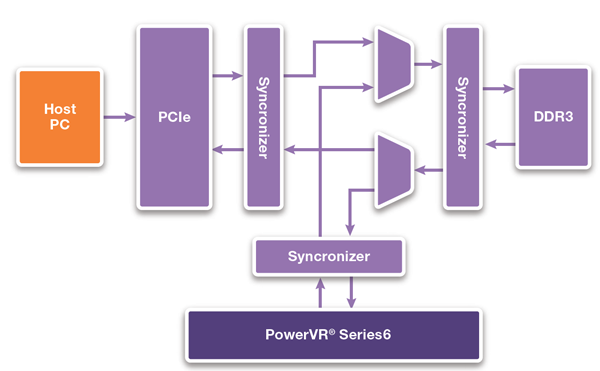

Synopsys所做的第一步是启动一个概念验证项目。这个项目为Imagination的PowerVR Series6 GPU展示了基于FPGA的原型设计。

2015-06-24 09:47:00 2022

2022

什么是FPGA原型? FPGA原型设计是一种成熟的技术,用于通过将RTL移植到现场可编程门阵列(FPGA)来验证专门应用的集成电路(ASIC),专用标准产品(ASSP)和片上系统(SoC)的功能

2022-07-19 16:27:29 2400

2400 FPGA原型在数字芯片设计中非常重要,因为相比用仿真器,或者加速器等来跑仿真,FPGA的运行速度,更接近真实芯片,可以配合软件开发者来进行底层软件的开发。这一流片前的软硬件的协同开发,是其最不可替代的地方。

2023-05-10 10:44:00 11197

11197

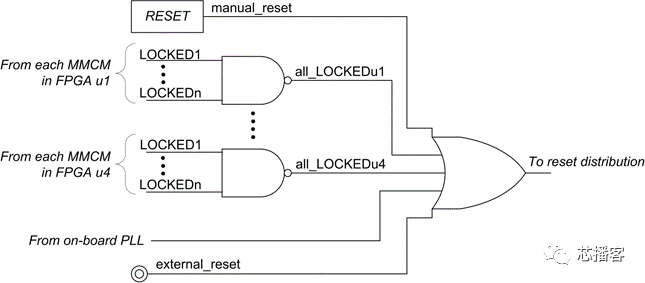

多片FPGA之间的互连,经常提到多路复用的概念,也经常提到TDM的概念,正确理解多路复用在多片FPGA原型验证系统中的机理,尤其是时序机制,对于我们正确看待和理解多片FPGA原型系统的性能有很好的促进作用。下图是一个使用多路复用器后接采样FF的多路复用解决方案的示例。

2023-06-06 10:04:35 2286

2286

16片ADS54J54多片如何同步,才能保证每个通道采集同一个目标的数据一一对应

2025-01-10 16:27:50

Tape Out并回片后都可以进行驱动和应用的开发。目前ASIC的设计变得越来越大,越来越复杂,单片FPGA已不能满足原型验证要求,多片FPGA验证应运而生。本文我就将与大家探讨FPGA原型验证的几个经典挑战性场景,(具体应对的办法,请戳原文。)容量限制和性能要求

2020-08-21 05:00:12

OpenFlow。研究人员可以在全国范围内在国家级测试平台上,比如美国的GENI和欧盟的FIRE上试验新型网络架构。 研究人员还越来越多地将NetFPGA开发板用于新理念的硬件原型设计,诸如新的转发模式、调度

2011-07-19 15:51:05

上面介绍的是整个 FPGA 固件系统的实现方法,为了验证设计的正确性,还需要编写一个测试平台对整个系统进行仿真。由于实际情况下 FPGA 是和 PDIUSBD12 进行通信,所以在测试平台中需要虚拟

2018-11-28 15:22:56

各位专家好:

关于多片C6678的同步调试问题想咨询下:

我打算做两个板子,每个板子上集成两片C6678的芯片,板间通信打算用光传输,现在想咨询的问题是在用CCS进行调试的时候,这个能不能实现同步调试,比如在某个时间一起停下来,去看看各自寄存器或者变量的值。谢谢。

2018-06-21 02:37:42

Hi,ADI我们现在在做一个5.8GHz的多通道接收机系统,需要多片AD9361之间载波相位同步我在AD9361的userguide UG570 page19,发现ad9361的external LO只能支持70MHz至4GHz?我的理解是否正确如果我希望使用5.8GHz的本振同步,有方法实现吗?

2018-10-08 10:51:27

多片AD9680如何同步?需要注意什么问题?

2023-12-08 08:02:57

用FPGA控制两片AD9739(以下简称A和B),其中A的SYNC_OUT接到了B的SYNC_IN,而A的SYNC_IN和B的SYNC_OUT接到了FPGA中。

现在配置0x10寄存器,采用无同步

2023-11-27 14:45:26

用4片AD9910,各种模式输出单片的调试都没有问题。现在要调多片同步,按照数据手册上的要求进行各个寄存器的配置,25M参考时钟输入,内部用锁相环陪频到1G,就是多片同步不了,12脚一直为高,检测

2018-11-20 09:11:33

用4片AD9910,各种模式输出单片的调试都没有问题。

现在要调多片同步,按照数据手册上的要求进行各个寄存器的配置,25M参考时钟输入,内部用锁相环陪频到1G,就是多片同步不了,12脚一直为高,检测不到有效地SYNC_IN信号,不知道原因,请技术支持帮助

2023-11-27 06:00:09

多片AFE5818的输入ADC时钟为同步时钟,不同的芯片上LVDS串行数据时钟(DCLKP、DCLKM)和帧时钟(FCLKP、FCLKM)是否是同步的

2024-11-18 07:29:50

笔者在多通道无源雷达信号处理机的设计中,采用了DSP芯片TMS320VC5409控制4片DDC芯片HSP50214B的接口电路,研究了同步控制多片HSP50214B等关键技术。DDC芯片

2019-06-04 05:00:17

官方应用笔记an605介绍了如何同步多片DDS9854, 上图是在倍频至300M时的需满足的时序图,要求EXT I/O UPDATE CLK的上升沿发生在REFCLK上升沿的前0.3ns和后

2018-09-29 15:36:31

实现通用的原型开发环境。功能包括:开发平台展示了跨转换器IC和跨板的多通道同步。在客户面前先在评估板环境中验证多通道性能,而不是仅仅为了同时测试多个通道而致力于生产设计。一定程度的集成和功能性,可以

2020-08-21 14:24:29

我有一个应用打算使用4片ADC3853进行4通道的信号同步采集,采样率为64Msps,我希望这4片ADC3583能在同一时刻采集信号(即采样同步),然后将采集到的原始数据(即不抽取)送给FPGA

2024-11-18 06:17:07

ADS131如何实现多片同步采集呢

2024-11-26 06:14:23

十、Kubernetes平台中日志收集

2019-11-04 09:19:30

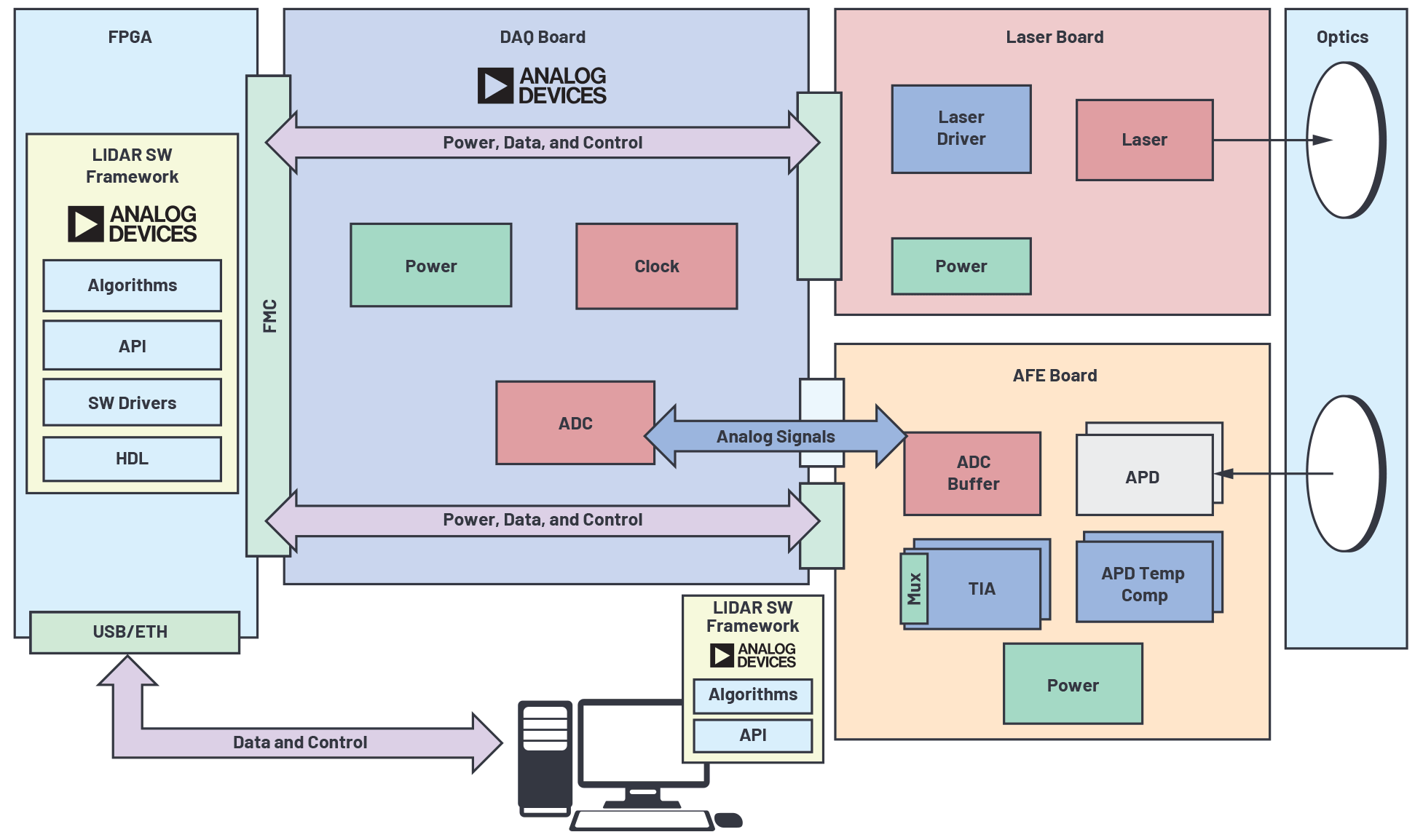

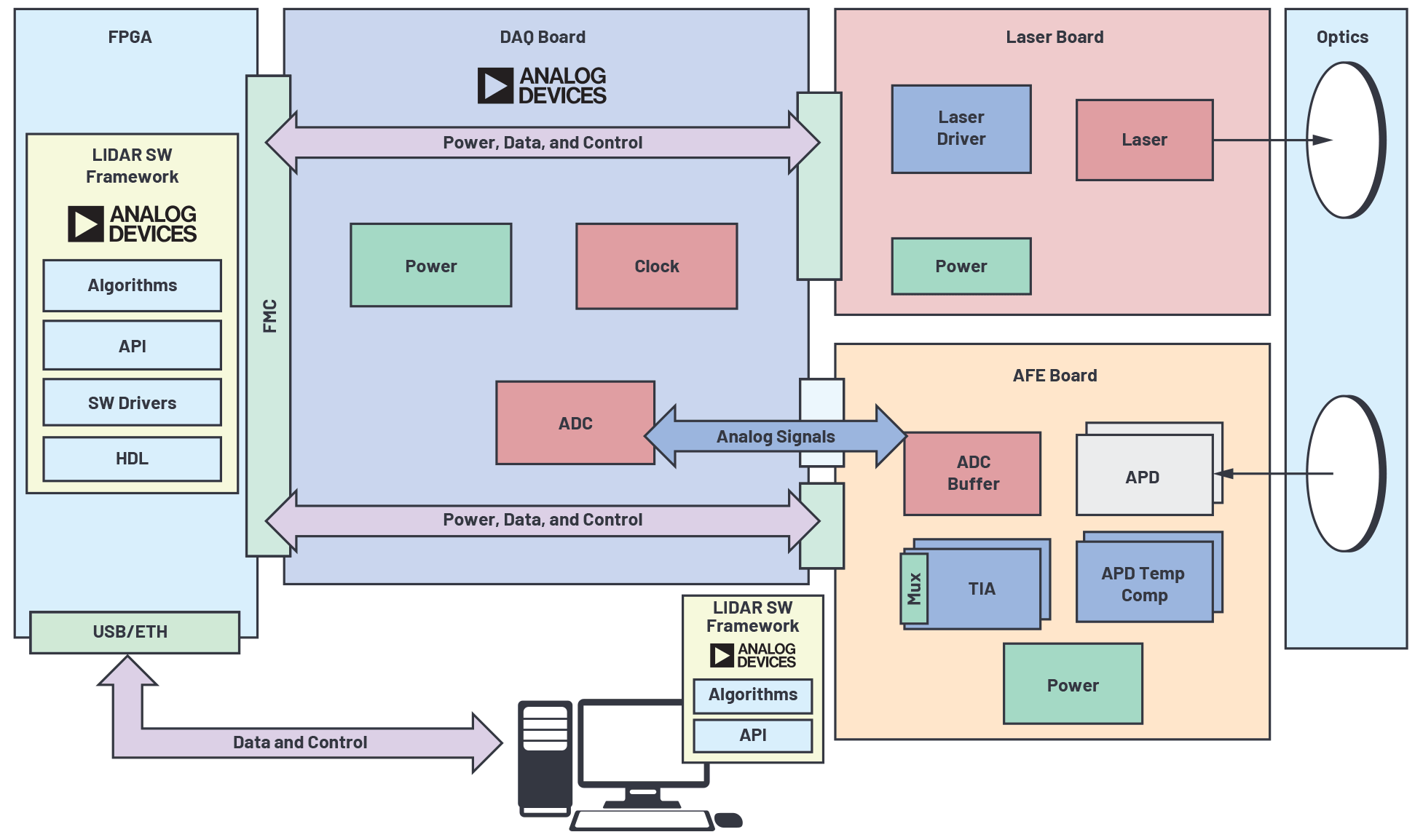

本文探讨ADI公司新推出且拥有广泛市场的LIDAR原型制作平台,以及它如何通过提供完整的硬件和软件解决方案,使得用户能够建立其算法和自定义硬件解决方案的原型,从而帮助客户缩短产品开发时间;详细介绍

2021-06-17 09:08:54

Thingy:91 X 为开发人员提供了一个经过全球认证的、多传感器、电池供电的蜂窝物联网原型平台

全球领先的低功耗无线连接解决方案提供商Nordic Semiconductor推出了其最新的物联网

2025-12-15 10:39:32

分割到24颗FPGA内。 此外, 实时运行功能还可以通过网络对多块基于FPGA的原型平台进行控制和监测。我非常高兴我们可以向客户提供这种新的能力。”

2019-07-02 06:23:44

斯坦福大学与赛灵思研究实验室(Xilinx Research Labs)联手开发专门面向研究社群的第二代高速网络设计平台 NetFPGA-10G。该新型平台采用最先进的技术,能够帮助研究人员迅速构建

2019-08-27 08:30:57

和使用SYSREF(AC-coupled)来进行同步,但两种方法都没能完成两片ADC之间的同步。

同一片ADC上2个通道的NCO是同步的。

在我的FPGA里面,我将给SYNC信号进行了与操作之后再分发到了两片ADC

2024-11-28 07:01:29

如果系统中使用多片功放芯片,如何实现时钟同步(例如TAS5622A)?

ST的芯片(如TDA7498)可以支持: Master芯片提供时钟给Slave芯片,从而实现多芯片同步。

2024-10-21 08:06:54

本文提出了一种基于FPGA的NoC验证平台。详细讨论了该验证平台中FPGA硬件平台和NoC软件的基本功能,并阐述了TG/R,MPU,MPI以及NoC软件的可重用性等特点。通过一个实例仿真验证的结果说明了该验证平台的基本功能和优越性。

2021-05-06 07:20:48

的设计和验证的复杂性需求。随着原型技术在设计分割以及多 FPGA 联 合调试领域的进步,基于FPGA 的原型系统不仅可以满足百万门级的设计需求,还可以实现设计规模高达15 亿门。基 于FPGA

2018-08-07 09:41:23

多片fpga组成jtag链的时候如何加载?

2023-08-11 09:10:26

求大神详细介绍一下基于FPGA的电子稳像平台的研究

2021-05-07 06:02:47

直线电机在平台中有哪些应用?

2021-10-29 06:39:19

评估新类别的元件。SDP连接至FPGA评估与原型制作平台,可以轻松创建并演示采用ADI元件通信的定制FPGA嵌入式设计。用户可以迅速建立定制评估与原型制作系统,还可以重复使用各种平台元件,演示各种丰富

2018-10-24 10:24:31

500MSPS的采样,但是没有提到任何多片同步的机制?有没有具体的实现多片ADCs(8路数据,最少4片)的同步实现操作?

2019-01-11 08:06:29

请教一下论坛里的诸位大牛; 我需要用多片AD9361接收5.8GHz的射频信号,如何保证多片AD9361的相位同步?因为AD9361的external LO只能支持70MHz至4GHz,不能满足

2019-02-15 14:55:35

如何将多片AD9361芯片进行相位同步,技术文档有说通过sync管脚进行MCS同步,但是仅仅只针对数据时钟完成同步。个人理解数据相位主要由RF混频处理以及后续数字处理决定,通过sync管教能够完成

2018-12-25 11:42:25

如何实现多片AD9361接收同步?每次上电周期的相位补偿是否可以通过软件自动补偿?

2019-02-18 07:58:53

。基于FPGA的原型验证方法凭借其速度快、易修改、真实性的特点,已经成为ASIC芯片设计中重要的验证方法[2].本文主要描述高频RFID芯片的FPGA原型验证平台的设计,并给出验证结果。

2019-06-18 07:43:00

。基于FPGA的原型验证方法凭借其速度快、易修改、真实性的特点,已经成为ASIC芯片设计中重要的验证方法。本文主要描述高频RFID芯片的FPGA原型验证平台的设计,并给出验证结果。1、RFID芯片的FPGA

2019-05-29 08:03:31

设计一种基于FPGA的多通道同步数据采集存储系统,分为多通道同步数据采集模块和数据存储模块。系统设计采用多通道数据的同步实时采集以及坏块检测技术。多通道同步数据采集

2010-12-27 15:31:33 70

70 《 FPGA的原型开发方法手册》(FPMM),这是一本介绍如何使用 FPGA 作为平台进行片上系统(SoC)开发的实用指南。FPMM 收录了众多公司的设计团队在设计和验证方面的宝贵经验,

2011-03-14 09:06:50 1099

1099 介绍了一种基于SRAM技术的FPGA可编程逻辑器件的编程方法,能在系统复位或上电时自动对器件编程。有效地解决了基于SRAM的FPGA器件掉电易失性问题,针对当前系统规模的日益增大,本文提出了一种用单片机对多片FPGA自动加载配置的解决方案.

2011-03-15 16:41:22 21

21 基于模糊PID多轴同步控制技术研究-2010。

2016-04-05 16:26:42 9

9 基于模糊PID控制的多电机同步控制研究-2009。

2016-04-05 16:36:48 22

22 自升式海洋平台多桩腿同步控制的研究_齐继阳

2017-01-16 14:04:30 0

0 如今,设计人员使用两种相对独立的方法进行 SoC 原型验证:以事务级模型为基础的虚拟原型验证和基于 FPGA 的原型验证。 虚拟原型验证执行快速的 TLM,并可提供更高效的调试和分析方案,非常适合

2017-02-08 14:32:11 572

572 完整原型设计平台便是当之无愧的大方案,该平台由现有的一些设备组成: Prodigy逻辑模块:基于FPGA的原型开发板。如,基于XilinxVirtex-72000T 3D FPGAs的TAI 逻辑模块

2017-02-09 03:49:04 917

917 效率。Protium S1与Cadence® Palladium® Z1企业级仿真平台前端一致,初始设计启动速度较传统FPGA原型平台提升80%。

2017-03-02 11:13:11 3210

3210 基于FPGA的MSK同步调谐研究_金国庆

2017-03-18 08:00:00 0

0 在校园信息化平台中研究与实现MVC2x框架_姚炼

2017-03-20 09:24:02 1

1 为了能在GPS接收端获取正确导航电文,研究了CJPS接收机位同步、帧同步的基本原理和实现方式。提出一种采用FPGA来实现位同步、帧同步系统的设计方案。使用Xilinx开发软件,通过Verilog代码

2017-11-07 17:13:39 12

12 利用Xilinx的FPGA设计了一个FPGA原型验证平台,用于无源高频电子标签芯片的功能验证。主要描述了验证平台的硬件设计,解决了由分立元件实现模拟射频前端电路时存在的问题,提出了FPGA器件选型

2017-11-18 08:42:22 4347

4347

门阵列(FPGA)做为安谋国际核心测试芯片,进而建构SoC原型制作平台。 验证SoC设计 FPGA原型最稳当 FPGA原型制作是在FPGA上实作SoC或特定应用集成电路(ASIC)设计的方法,并进行硬件验证和早期软件开发。

2018-05-11 09:07:00 3069

3069

随着新型SoC(片上系统)设计的成本和复杂性的不断提高,现场可编程门阵列(FPGA)原型技术正日益成为SoC新项目的重要组成部分,甚至是至关重要的组成部分。通过提供一种更快到达硬件的方法,FPGA

2019-06-25 08:00:00 2

2 Microchip启动了PolarFire片上系统(SoC)现场可编程门阵列(FPGA)早期使用计划(EAP)。

2019-12-16 15:16:21 1053

1053 Microchip启动了PolarFire片上系统(SoC)现场可编程门阵列(FPGA)早期使用计划(EAP)。

2019-12-26 15:39:03 1460

1460 FACE-VUP:大规模FPGA原型验证平台 FACE-VUP大规模FPGA原型验证平台是FACE系列的最新产品。FACE-VUP同时搭载16nm工艺的Virtex UltraScale+系列主器件

2020-05-19 10:50:05 3371

3371 其次,部分FPGA开发板也被用在IP和小型芯片设计的开发验证场景。这部分开发板配备大容量的FPGA芯片,甚至是单板配备多片FPGA芯片来适应开发验证场景,一般由用户自己负责手工实现从设计到FPGA功能原型的流程。

2022-04-28 09:38:33 3563

3563 从系统的特性上看,FPGA 原型系统支持多FPGA、自动分割;性能较高的情况下运行系统软件;仿真加速器的超大容量可以放全芯片的设计,进行全芯片的系统功能/性能/功耗验证。

2022-05-25 09:35:13 10849

10849 Corundum是一个基于FPGA的开源原型平台,用于高达100Gbps及更高的网络接口开发。Corundum平台包括一些用于实现实时,高线速操作的核心功能,包括:高性能数据路径,10G/ 25G

2022-11-03 10:02:14 3126

3126 本文讨论ADI公司新的广阔市场LIDAR原型设计平台,以及该平台如何通过提供完整的硬件和软件解决方案来帮助缩短客户的产品开发时间,客户可以使用该解决方案对其算法和定制硬件解决方案进行原型设计。它详细介绍了模块化硬件设计的细节,包括光接收和发射信号链、FPGA 接口和用于远距离检测的光学器件。

2022-12-20 14:49:02 3352

3352

FPGA原型验证在数字SoC系统项目当中已经非常普遍且非常重要,但对于一个SoC的项目而言,选择合适的FPGA原型验证系统显的格外重要

2023-04-03 09:46:45 2074

2074 FPGA原型平台的性能估计与应用过程的资源利用率以及FPGA性能参数密切相关,甚至FPGA的制程也是一个因素。

2023-04-04 09:49:04 3145

3145 FPGA原型设计是一种成熟的技术,用于通过将RTL移植到现场可编程门阵列(FPGA)来验证专门应用的集成电路(ASIC),专用标准产品(ASSP)和片上系统(SoC)的功能和性能。

2023-04-10 09:23:29 2664

2664 FPGA原型验证平台系统灵活性主要体现在其外部连接表现形式,由单片FPGA平台或者2片的FPGA,抑或是4片的FPGA组成一个子系统。

2023-04-11 09:50:03 1543

1543 FPGA原型验证平台系统灵活性主要体现在其外部连接表现形式,由单片FPGA平台或者2片的FPGA,抑或是4片的FPGA组成一个子系统。

2023-04-11 09:50:37 936

936 FPGA与FPGA之间互连对信号延迟的影响,两片FPGA的IO之间每一个额外的过渡,例如连接器、焊点甚至板内通孔,都会增加一些阻抗,从而降低信号质量,并增加信号之间串扰的概率。然而,经过仔细分析,发现这并不是一个想象中的大问题。主要矛盾是FPGA互连线的影响。

2023-04-16 10:21:51 1333

1333 FPGA原型验证系统要尽可能多的复用SoC相关的模块,这样才是复刻SoC原型的意义所在。

2023-04-19 09:08:15 1953

1953 在进行FPGA原型验证的过程中,当要把大型的SoC进行FPGA原型验证时,有时候会遇到一种情况,同样的接口分两组出去到不同的模块,而这两个模块规模较大,又需要分割在两片FPGA中,这时候就会像下图一样。

2023-05-04 16:21:34 1331

1331

多片FPGA原型验证系统的拓扑连接方式各不相同,理想的多片FPGA原型验证系统应该可以灵活配置,可以使用其相应的EDA工具

2023-05-08 11:51:40 891

891

当SoC的规模在一片FPGA中装不下的时候,我们通常选择多片FPGA原型验证的平台来承载整个SoC系统。

2023-05-10 10:15:16 689

689 当SoC的规模在一片FPGA中装不下的时候,我们通常选择多片FPGA原型验证的平台来承载整个SoC系统。

2023-05-23 15:31:10 1015

1015 FPGA原型验证系统要尽可能多的复用SoC相关的模块,这样才是复刻SoC原型的意义所在。

2023-05-23 16:50:34 1109

1109

多片FPGA的原型验证系统的性能和容量通常受到FPGA间连接的限制。FPGA中有大量的资源,但IO引脚的数量受封装技术的限制,通常只有1000个左右的用户IO引脚。

2023-05-23 17:12:35 2189

2189

多片FPGA之间的互连,经常提到多路复用的概念,也经常提到TDM的概念

2023-06-06 10:07:37 852

852

综合工具的任务是将SoC设计映射到可用的FPGA资源中。自动化程度越高,构建基于FPGA的原型的过程就越容易、越快。

2023-06-13 09:27:06 879

879

当SoC系统的规模很大的时候,单片FPGA验证平台已经无法容纳这么多容量,我们将采取将SoC设计划分为多个FPGA的映射。

2023-06-19 15:42:08 1081

1081 所有形式的原型都为验证硬件设计和验证软件提供了强大的方法,模型或多或少地模仿了目标环境。基于FPGA的原型设计在项目的关键后期阶段尤其有益。用户有几个原型设计选项根据他们的主要需求,可以选择各种基于软件和硬件的技术来原型他们的设计。

2023-10-11 12:39:41 1808

1808

FPGA原型设计是一种成熟的技术,用于通过将RTL移植到现场可编程门阵列(FPGA)来验证专门应用的集成电路(ASIC),专用标准产品(ASSP)和片上系统(SoC)的功能和性能。

2024-01-12 16:13:01 2194

2194 proFPGA是mentor的FPGA原型验证平台,当然mentor被西门子收购之后,现在叫西门子EDA。

2024-01-22 09:21:01 3230

3230

FPGA原型验证平台与硬件仿真器在芯片设计和验证过程中各自发挥着独特的作用,它们之间存在明显的区别。

2024-03-15 15:07:03 2340

2340 电子发烧友网站提供《实现多轴电机驱动系统内的多片C2000 PWM同步.pdf》资料免费下载

2024-09-03 09:25:17 2

2

电子发烧友App

电子发烧友App

评论