AMD 7nm Versal系列器件引入了可编程片上网络(NoC, Network on Chip),这是一个硬化的、高带宽、低延迟互连结构,旨在实现可编程逻辑(PL)、处理系统(PS)、AI引擎(AIE)、DDR控制器(DDRMC)、CPM(PCIe/CXL)等模块之间的高效数据交换。

2025-09-19 15:15:21 2366

2366

国际半导体技术蓝图(ITRS)持续寻找硅替代材料的行动备受全球瞩目,业界期望能找到一种能以2D实现超高速的理想导电材料。

2015-07-21 09:52:43 1846

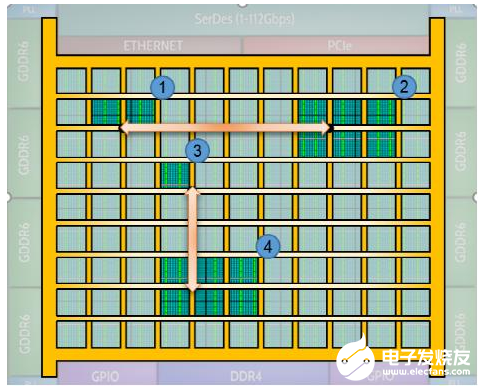

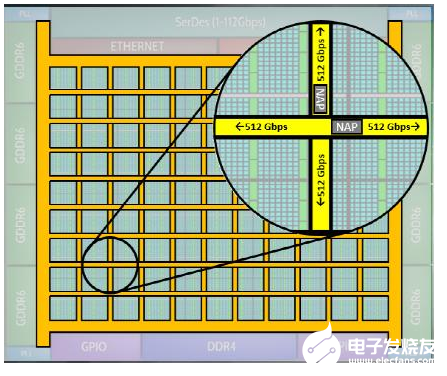

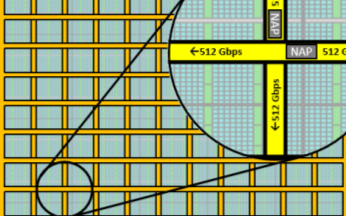

1846 NoC的内部由一组行和列组成,它们在整个FPGA逻辑阵列中将网络数据流量从水平和垂直方向上进行分发。

2020-06-03 16:55:08 1789

1789

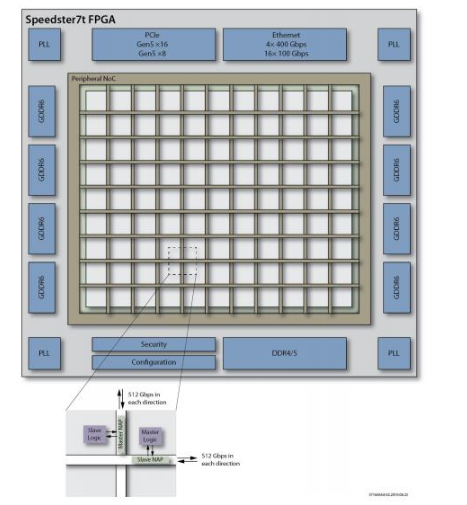

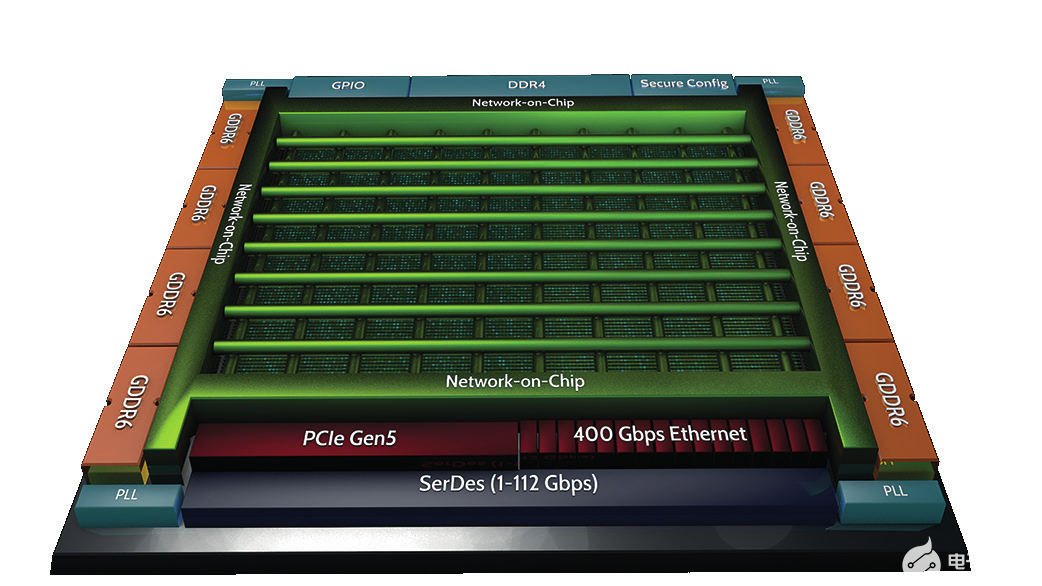

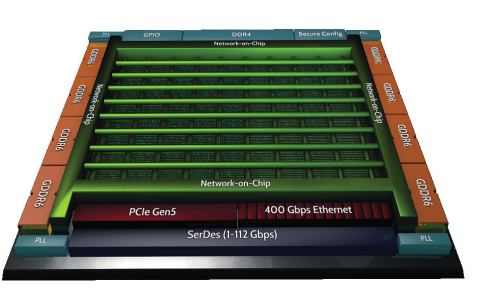

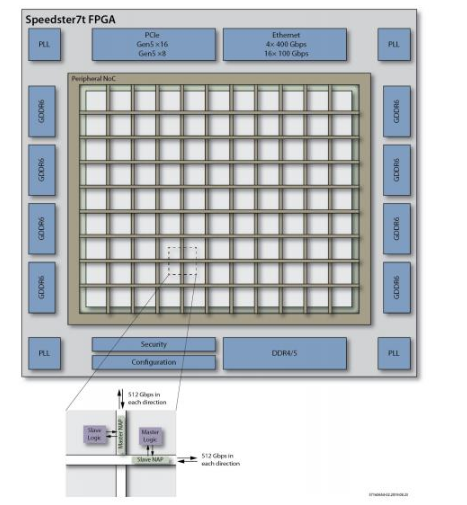

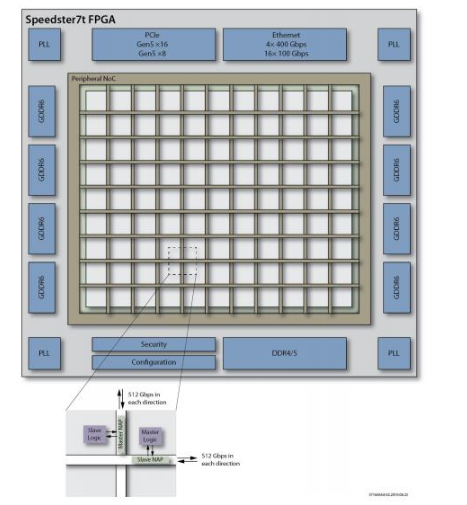

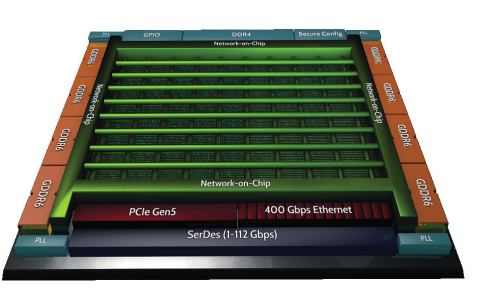

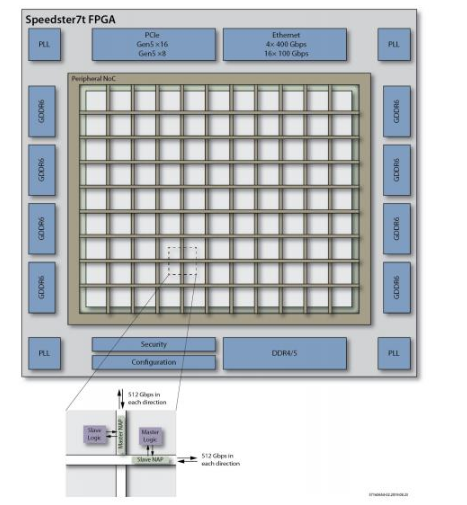

Achronix 在其最新基于台积电(TSMC)7nm FinFET工艺的Speedster7t FPGA器件中包含了革命性的创新型二维片上网络(2D NoC)。

2020-08-21 14:44:57 1082

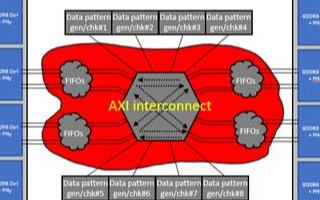

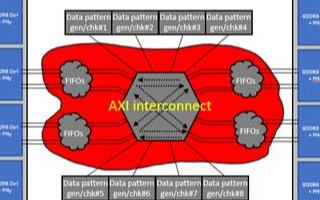

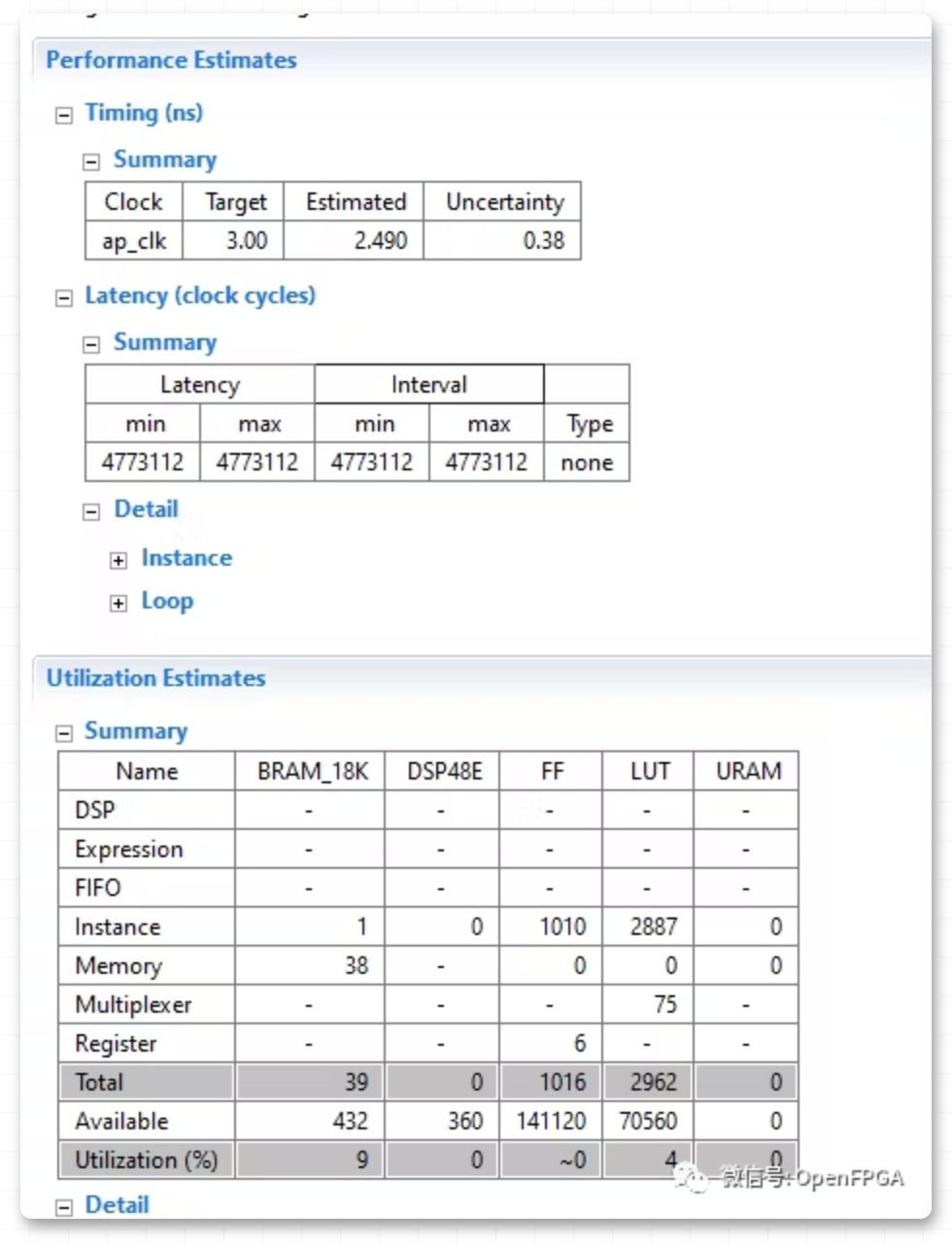

1082 对于AXI interconnect模块,我们采用Github上开源的AXI4总线连接器来实现,这个AXI4总线连接器将4个AXI4总线主设备连接到8个AXI4总线从设备,源代码可以在参考文献2

2020-09-03 12:39:38 1181

1181

Speedster7t架构中的2D NoC提供了从逻辑阵列的可编程逻辑到位于I/O环中的高速接口子系统的高带宽连接,用于连接到片外资源。

2021-07-07 16:31:31 2168

2168

创新的二维片上网络(2D NoC)来处理这些高带宽数据流。Achronix的FPGA中特有的2D NoC实现是一种创新,它与用可编程逻辑资源来实现2D NoC的传统方法相比,有哪些创新和价值呢?本白皮书讨论了这两种实现2D NoC的方法,并提供了一个示例设计,以展示与软2D NoC实现相比,

2022-04-21 18:02:56 6579

6579

流动提出了更高的要求。于是,在FPGA芯片中集成包括片上二维网络(2D NoC)和各种最新高速接口的新品类FPGA芯片应运而生,成为FPGA产业和相关应用的新热点。 拉开这场FPGA芯片创新大幕的是全球最大的独立FPGA技术和产品提供商Achronix半导体公司,

2022-07-06 15:48:52 1477

1477

只有在脑海中建立了一个个逻辑模型,理解FPGA内部逻辑结构实现的基础,才能明白为什么写Verilog和写C整体思路是不一样的,才能理解顺序执行语言和并行执行语言的设计方法上的差异。在看到一段简单程序的时候应该想到是什么样的功能电路。

2022-08-25 11:12:00 1318

1318 与HBM DRAM堆叠裸片之间对高带宽连接的需求。本文将深入探讨UCIe支持的不同接口,以实现片上网络(NoC)互连。

2025-08-04 15:17:24 2452

2452 2D NoC如同在FPGA可编程逻辑结构上运行的高速公路网络一样,为FPGA外部高速接口和内部可编程逻辑的数据传输提供了超高带宽。

2021-11-11 14:20:14 3561

3561

背光区域调节技术2D区域调光的优点2D区域调光面临的难题及机遇

2021-02-26 08:21:12

删除高扇出 nets。因此,如果您正在开发基于FPGA的高速设计,即使不是数字射频应用,您有必要尽快下载和阅读上述白皮书以开始您的设计—— “利用赛灵思All Programmable FPGA 和 SoC 实现高速无线电设计”。

2017-02-10 17:10:32

FPGA实现高速FFT处理器的设计介绍了采用Xilinx公司的Virtex - II系列FPGA设计高速FFT处理器的实现方法及技巧。充分利用Virtex - II芯片的硬件资源,减少复杂逻辑,采用

2012-08-12 11:49:01

FPGA(Field-Programmable Gate Array,现场可编程门阵列)是一种特殊的集成电路,其内部结构由大量的可配置逻辑块和互连线组成。FPGA可以通过编程来实现各种数字系统功能

2024-01-26 10:03:55

排列于芯片四周;可编程内部互连包括各种长度的连线线段和一些可编程连接开关,它们将各个可编程逻辑块或I/O块连接起来,FPGA在可编程逻辑块的规模,内部互连线的结构和采用的可编程元件上存在较大的差异.较

2020-08-28 15:41:47

可以执行各种逻辑操作(如与、或、非、异或等),将输入信号转换为输出信号。这些逻辑门通过FPGA内部的互连网络相互连接,从而形成一个复杂的逻辑电路。

在FPGA中,逻辑电路的设计和实现通常使用硬件描述

2024-04-29 23:26:51

NoC在高端FPGA的应用是什么?NoC给Speedster 7t FPGA带来的优势有哪些?

2021-06-17 11:12:26

。为了解决这一问题,Achronix 在其最新基于台积电(TSMC)7nm FinFET 工艺的 Speedster7t FPGA 器件中包含了革命性的创新型二维片上网络(2D NoC)。这种 2D

2020-09-07 15:25:33

在超高速数据采集方面,FPGA(现场可编程门阵列)有着单片机和DSP所无法比拟的优势。FPGA时钟频率高,内部时延小,目前器件的最高工作频率可达300MHz;硬件资源丰富,单片集成的可用门数达1000万门;全部控制逻辑由硬件资源完成,速度快,效率高;组成形式灵活,可以集成外围控制、译码和接口电路。

2019-08-02 06:51:33

ADSP-21065L的片内RAM来中转,然后再完成高速缓存到海量缓存的数据传输,具体做法如图4所示。 ADSP内部开设有1k32bit的RAM块构成中转区,可利用外部口DMA通道0进行A/D高速缓存到片内

2020-12-04 15:59:14

Arm®CoreLink™ NI‑710AE片上网络互连是一种高度可配置的AMBA®兼容系统级互连,可实现汽车和工业应用的功能安全。使用NI‑710AE,您可以创建一个非相干互连,该互连针对SoC

2023-08-08 06:24:43

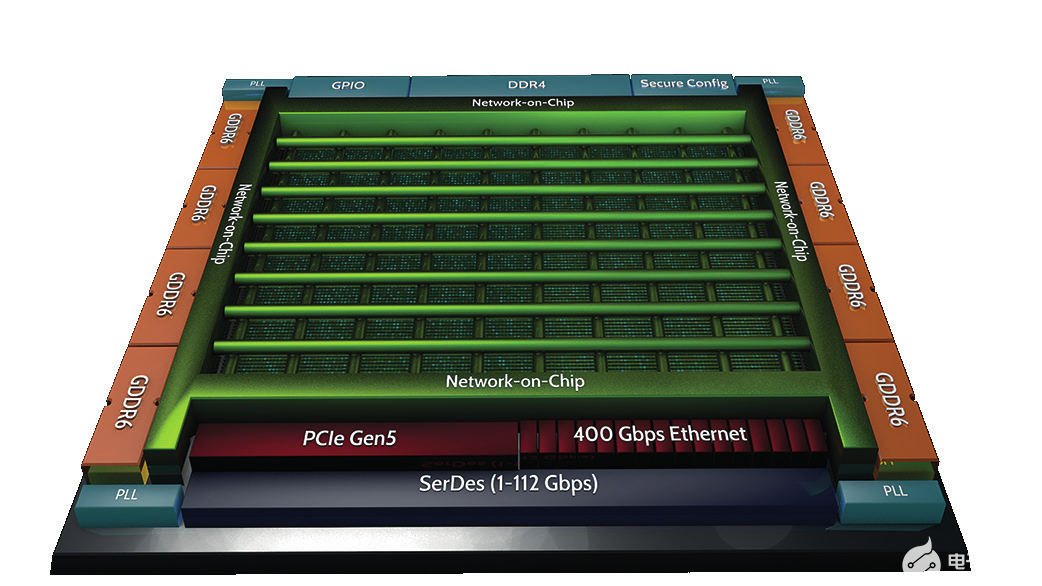

的7nmFinFET工艺,其架构采用革命性的新型2D片上网络(NoC),独创的机器学习处理器矩阵(MLP),并利用高带宽GDDR6控制器、400G以太网和PCIExpressGen5接口,在保障ASIC级别性能的同时

2021-07-07 08:00:00

第41章 STM32F429的LTDC应用之LCD汉字显示和2D图形显示本章教程为大家讲解LTDC应用中最基本的汉字显示和2D图形显示功能实现。目录第41章 STM32F429的LTDC应用之LCD

2021-08-10 07:24:07

【作者】:李旺远;王长山;【来源】:《计算机与现代化》2010年03期【摘要】:随着芯片集成度的提高,基于片上系统[1](SoC)的片上网络(NoC)已成为芯片设计的重点。随着IP核的增多,节点和链

2010-04-22 11:35:04

)来实现组合逻辑,每个查找表连接到一 个D触发器的输入端,触发器再来驱动其他逻辑电路或驱动I/O,由此构成了既可实现组合逻辑功能又可实现时序逻辑功能的基本逻辑单元模块,这些模块间利用 金属连线互相连接或

2019-08-11 04:30:00

你好,我正在使用带有AD6676-EBZ高速adc的定制FPGA平台。该逻辑包含JESD24B IP。我想将VIO范围用于眼图。但我真的不明白它是如何运作的。我发现2D眼睛扫描逻辑提供了通过axi4

2020-07-30 10:24:35

基于FPGA的超高速FFT硬件实现介绍了频域抽取基二快速傅里叶运算的基本原理;讨论了基于FPGA达4 096点的大点数超高速FFT硬件系统设计与实现方法,当多组大点数进行FFT运算时,利用FPGA

2009-06-14 00:19:55

在FPGA 上设计一个高性能、灵活的、面积小的通信体系结构是一项巨大的挑战。大多数基于FPGA 的片上网络都是运行在一个单一时钟下。随着FPGA 技术的发展,Xilinx 公司推出了Virtex-4

2019-08-21 06:47:43

机载视频图形显示系统主要实现2D图形的绘制,构成各种飞行参数画面,同时叠加实时的外景视频。由于FPGA具有强大逻辑资源、丰富IP核等优点,基于FPGA的嵌入式系统架构是机载视频图形显示系统理想的架构

2019-06-24 06:07:53

基于FPGA的通用高速串行互连协议设计基于FPGA的通用高速串行互连协议设计

2012-08-11 15:46:52

】:CNKI:SUN:HZLG.0.2010-03-010【正文快照】:为解决虫孔交换机制下的队列头阻塞问题,大多数片上网络(NoC)[1~3]采用了虚通道技术[4,5],利用该技术能减少队列头阻塞的次数

2010-04-22 11:34:25

高速连续数据采集系统的背景及功能是什么?如何利用FPGA实现高速连续数据采集系统设计?FPGA在高速连续数据采集系统中的应用有哪些?

2021-04-08 06:19:37

逻辑结构之上运行的高速公路网络一样,为FPGA外部高速接口和内部可编程逻辑的数据传输提供了大约高达27Tbps的超高带宽。作为Speedster7t FPGA器件中的重要创新之一,2D NoC为FPGA

2020-10-20 09:54:00

NoC为FPGA设计提供了哪些优势?NoC在FPGA内部逻辑互连中发挥的作用是什么?如何利用片上高速网络创新地实现FPGA内部超高带宽逻辑互连?

2021-06-17 11:35:28

前言FPGA 可以实现高速硬件电路,如各种时钟,PWM,高速接口,DSP计算等硬件功能。这是Cortex-M 处理器软件无法比拟的。要实现FPGA 的逻辑设计,对于嵌入式系统工程师又是比较复杂和具有

2021-12-21 06:13:49

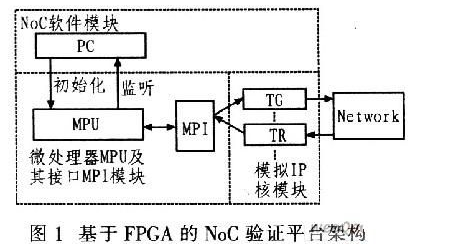

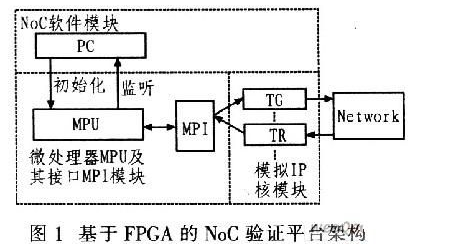

本文提出了一种基于FPGA的NoC验证平台。详细讨论了该验证平台中FPGA硬件平台和NoC软件的基本功能,并阐述了TG/R,MPU,MPI以及NoC软件的可重用性等特点。通过一个实例仿真验证的结果说明了该验证平台的基本功能和优越性。

2021-05-06 07:20:48

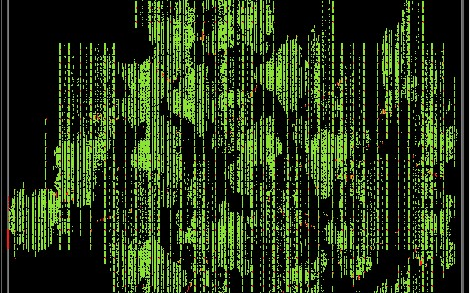

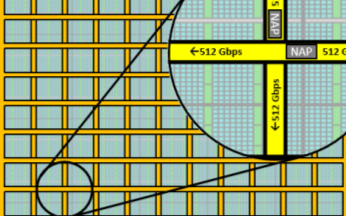

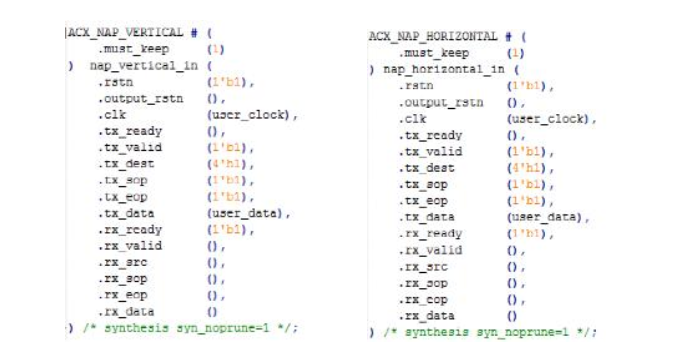

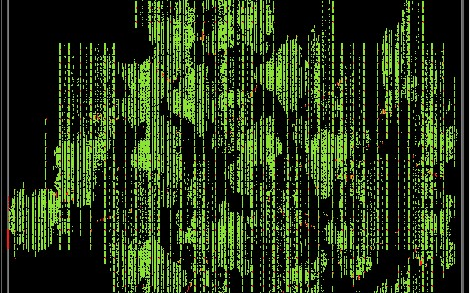

288bit的原始数据模式(Raw data mode)。 用户可以通过这288bit的信号进行逻辑直连或者自定义协议互连。图3利用2D NoC进行内部逻辑互连在NoC的每个交叉点上都有两个网络接入点

2020-05-12 08:00:00

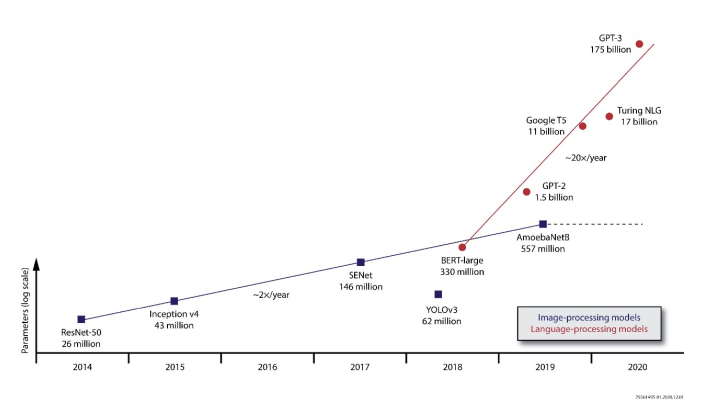

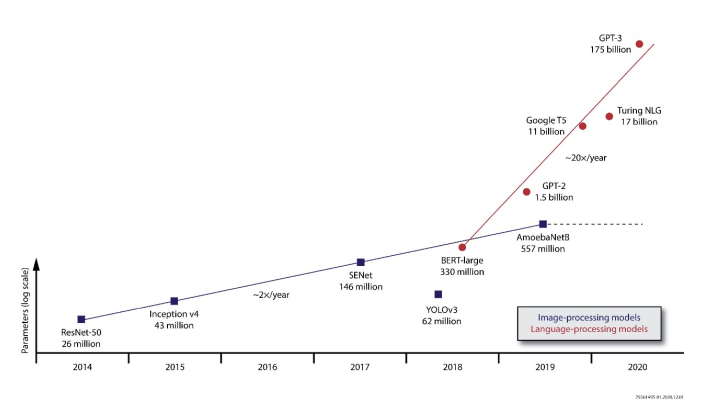

实时处理,因而带来了对FPGA等硬件数据处理加速器的需求。如图1所示。在这样的数据高速增长的情况下,用于传输数据的网络带宽和处理数据所需要的算力也必须急速增长。传统的CPU已经越来越不堪重负,所以用硬件加速

2021-12-21 08:00:00

的 7nm FinFET 工艺,其架构采用革命性的新型 2D 片上网络 (NoC),独创的机器学习处理器矩阵 (MP),并利用高带宽 GDDR6 控制器、400G 以太网和 PCI Express

2020-10-20 09:48:39

采用片上网络(NoC)的新型FPGA数据架构赋能5G网络和数据中心智能网卡(SmartNIC)设计方案

2021-02-22 08:01:25

,如果大家想在对话框上面绘制2D图形的话,可以将STemWin的2D绘制函数放在对话框回调函数中的WM_PAINT消息中实现。 这里跟大家讲一下如何利用uCGUIBulder4.0在对话框上面绘制简单的横线和竖线。60.1.1 第一步:建立如下界面

2016-10-18 11:33:49

与FPGA中的普通路由相比,使用片上网络来互连DSP48A会降低性能吗?以上来自于谷歌翻译以下为原文Will the use of network on chip to interconnect

2019-06-28 09:39:03

无误,则写入为该接口分配的PL4模块中的FIFO,否则丢弃。为了充分利用带宽,PL4接口把MAC帧划分为数据片(以64字节或MAC帧尾之前数据为一片)调度输出,并采用带内控制字的形式指示帧头、数据、帧尾

2019-04-29 07:00:07

基于VxWorks操作系统有多种2D 显示的解决方案,但由于种种原因,仅介绍基于VxWorks操作系统的WindML 2D显示解决方案,并着重讨论了WindML的体系结构,且介绍了2D文本显示。该方案已

2008-12-16 14:26:43 10

10 介绍了频域抽取基二快速傅里叶运算的基本原理;讨论了基于FPGA达4 096点的大点数超高速FFT硬件系统设计与实现方法,当多组大点数进行FFT运算时,利用FPGA内部大容量存储资源,采

2009-04-26 18:33:08 26

26 基于VxWorks操作系统有多种2D 显示的解决方案,但由于种种原因,仅介绍基于VxWorks操作系统的WindML 2D显示解决方案,并着重讨论了WindML的体系结构,且介绍了2D文本显示。该方案已被

2009-12-05 16:35:20 14

14 片上网络(Network-on-Chip, NoC)以网络互连结构代替传统总线结构,很好地解决了片上高性能计算资源之间的通信瓶颈问题。路由器是实现NoC 的重要基础部件,本文在分析国内外相关

2009-12-14 09:37:38 34

34 介绍了一种基于FPGA 的超高速数据采集与处理系统,给出了系统实现的方案,并详细阐述了各硬件电路的具体构成。对系统软件功能做了简要介绍,并利用嵌入式逻辑分析仪对该超高

2010-01-20 16:03:27 58

58 比较了多种DSP芯片的互连性能,给出了一种简单高性能DSP网络结构。针对构成DSP网络通讯接口的链路口,分析其基本特点,并且提出了在FPGA中实现的设计原理。最后给出了设计仿真图和

2010-07-27 16:46:46 24

24 分析当前高速互连网络中同时存在的TCP/IP, GAMMA, InfiniBand, SCI 等技术的实现机制,介绍RapidIO 高性能总线技术。研究RapidIO 协议和MPC8548 处理器的相关技术,提出在RapidIO 高速互连网

2010-09-22 08:35:11 20

20 在小尺寸DSP上实现2D条形码解码

2010-10-13 15:28:37 31

31 随着FPGA设计复杂度的增加,传统测试方法受到限制。在高速集成FPGA测试中,其内部信号的实时获取和分析比较困难。介绍了Quartus II中SingalTap II嵌入式逻辑分析器的使用,并给出一个

2010-12-17 15:25:17 16

16 针对基于软件仿真片上网络NoC(Network on Chip)效率低的问题,提出基于FPGA的NoC验证平台构建方案。该平台集成可重用的流量产生器TG(Traffic Generation),流量接收器TR(Traffic Receiver)

2011-01-04 16:24:38 12

12 本内容介绍了分级环片上网络互连

2011-05-19 15:37:33 21

21 基于FPGA的通用高速串行互连协议设计。

2016-05-11 09:46:01 18

18 2D仿真PPT培训,感兴趣的小伙伴们可以瞧一瞧。

2016-11-17 18:35:23 0

0 片上网络Network-on-chip (NoC) 是一种应用于大规模集成电路(VLSI)系统中的,一种新的片上系统(System-on-chip)的设计方法。

2017-02-11 06:39:13 1952

1952

DSP与FPGA高速的数据传输有三种常用接口方式: EMIF, HPI 和 McBSP 方式。而采用 EMIF 接口方式, 利用 FPGA ( 现场可编程逻辑门阵列) 设计 FIFO的接口电路,即可实现高速互联。

2017-02-11 14:16:10 2950

2950

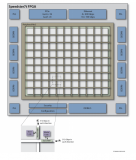

为了能够灵活地验证和实现自主设计的基于NoC的多核处理器,缩短NoC多核处理器的设计周期,提出了设计集成4片Virtex-6—550T FPGA的NoC多核处理器原型芯片设计/验证平台。分析和评估了

2017-11-22 09:15:01 5266

5266 。今天,英特尔披露了有关如何通过 EMIB 帮助全新 Stratix 10 MX FPGA(现场可编程逻辑门阵列)家族芯片实现带宽大涨的部分细节。

2017-12-20 12:51:10 7100

7100 研究和实现了一个基于OMAP3530的2D到3D视频自动转换系统,重点研究深度图获取和深度信息渲染等主要核心技术及其实现。该系统利用OMAP3530其特有的双核结构,进行系统优化:由其ARM处理器

2018-03-06 14:20:55 1

1 数据采集系统的总体架构如图1所示,其中PCI核、DMA控制器与A/D控制器均在FPGA内部实现。为实现多路并行采样,可选用多片A/D器件并行处理的方式,在FPGA的高速状态机控制下,完成模拟信号经过

2018-08-28 10:16:07 14862

14862

本视频介绍了Xilinx的28nm,20nm和16nm FPGA和MPSoC在2016年和2017年初发生的2D标记变化。

本概述提供了有用的信息,包括2D标记趋势,客户利益,标签

2018-11-26 06:24:00 3169

3169 英特尔近日向业界推出了首款3D逻辑芯片封装技术“Foveros”,据悉这是在原来的3D封装技术第一次利用3D堆叠的优点在逻辑芯片上进行逻辑芯片堆叠。也是继多芯片互连桥接2D封装技术之后的又一个颠覆技术。

2018-12-14 16:16:45 3316

3316 本文提出的基于FPGA的NoC验证平台在仿真速度方面是一般基于HDL的软件仿真的16 000倍,而基于PC机编写的NoC软件更增强了该平台的灵活性和实用性。

2019-04-13 11:33:47 2783

2783

的创新性片上网络(NoC)互连知识产权(IP)产品的全球领先供应商,宣布,MobileEye已购买Arteris IP 的NCore缓存一致性互连产品、flexNOC互连产品以及NCore和flexNOC Resilience软件包等多项产品。

2019-05-09 17:13:32 3760

3760 了革命性的新型二维片上网络(2D NoC)。2D NoC如同在FPGA可编程逻辑结构上运行的高速公路网络一样,为FPGA外部高速接口和内部可编程逻辑的数据传输提供了超高带宽(~27Tbps)。 图1

2020-03-04 15:59:39 2167

2167 Achronix 最新基于台积电(TSMC)的7nm FinFET工艺的Speedster7t FPGA器件包含了革命性的新型二维片上网络(2D NoC)。

2020-05-04 09:43:00 979

979 Achronix 最新基于台积电(TSMC)的7nm FinFET工艺的Speedster7t FPGA器件包含了革命性的新型二维片上网络(2D NoC)。

2020-05-28 10:27:12 837

837

谷歌发明的由2D图像生成3D图像的技术,利用3D估计神经网络图像信息的补全以及预测,融合了拍摄角度、光照等信息,让生成的3D图像看起来更加逼真,这种技术对于三维建模以及工业应用都具有极大的指导意义。

2020-12-24 12:55:23 5463

5463

可编程逻辑结构上运行的高速公路网络一样,为FPGA外部高速接口和内部可编程逻辑的数据传输提供了超高带宽。 2. 2D NoC给Speedster 7t FPGA带来的优势 日益增长的数据加速需求对硬件平台

2021-11-12 09:21:22 2972

2972

AD 2D标准封装库下载

2022-01-17 10:16:24 26

26 领先功能。在一系列产品视频中,Achronix 展示了 Speedster7t AC7t1500 的创新功能,包括 PCIe Gen5、400G 以太网、DDR4 和 GDDR6 内存接口以及 2D 片上网络 (2D NoC)。

2022-03-17 15:23:00 4455

4455 片上网络(2D NoC)来处理这些高带宽数据流。Achronix的FPGA中特有的2D NoC实现是一种创新,它与用可编程逻辑资源来实现2D NoC的传统方法相比,有哪些创新和价值呢?本白皮书讨论了

2022-04-21 09:27:35 2216

2216 Achronix Speedster7t FPGA除了在外围Hard IP上都采用目前业内领先的大带宽高速率IP,在内部的可编程逻辑的架构中也做了大量的优化去进一步提高内部可编程逻辑的性能,从而适配

2022-07-05 15:37:41 1777

1777 2d封装库Altium

2022-09-20 15:27:35 0

0 尺寸较小的2D纳米材料还可以提供更多的边缘活性位点,因此通过2D纳米材料的尺寸调控也能够提高催化性能。在2D氧化物纳米材料中引入缺陷

2022-11-03 09:22:10 2777

2777 自从几十年前首次推出FPGA 以来,每种新架构都继续在采用按位(bit-wise)的布线 结构。 虽然这种方法一直是成功的,但是随着高速通信标准的兴起,总是要求不断增加片上总线位宽,以支持这些

2023-04-03 14:57:57 1149

1149

的数据传输带宽以及 存储器 带宽。但是在FPGA内部,可编程逻辑部分随着工艺提升而不断进步的同时,内外部数据交换性能的提升并没有那么明显,所以FPGA内部数据的交换越来越成为数据传输的瓶颈。 为了解决这一问题,Achronix 在其 基于台积电(TSMC)7nm FinFET工艺

2023-04-18 11:30:06 945

945 电子发烧友网站提供《2D物理引擎开源分享.zip》资料免费下载

2023-07-12 11:17:01 0

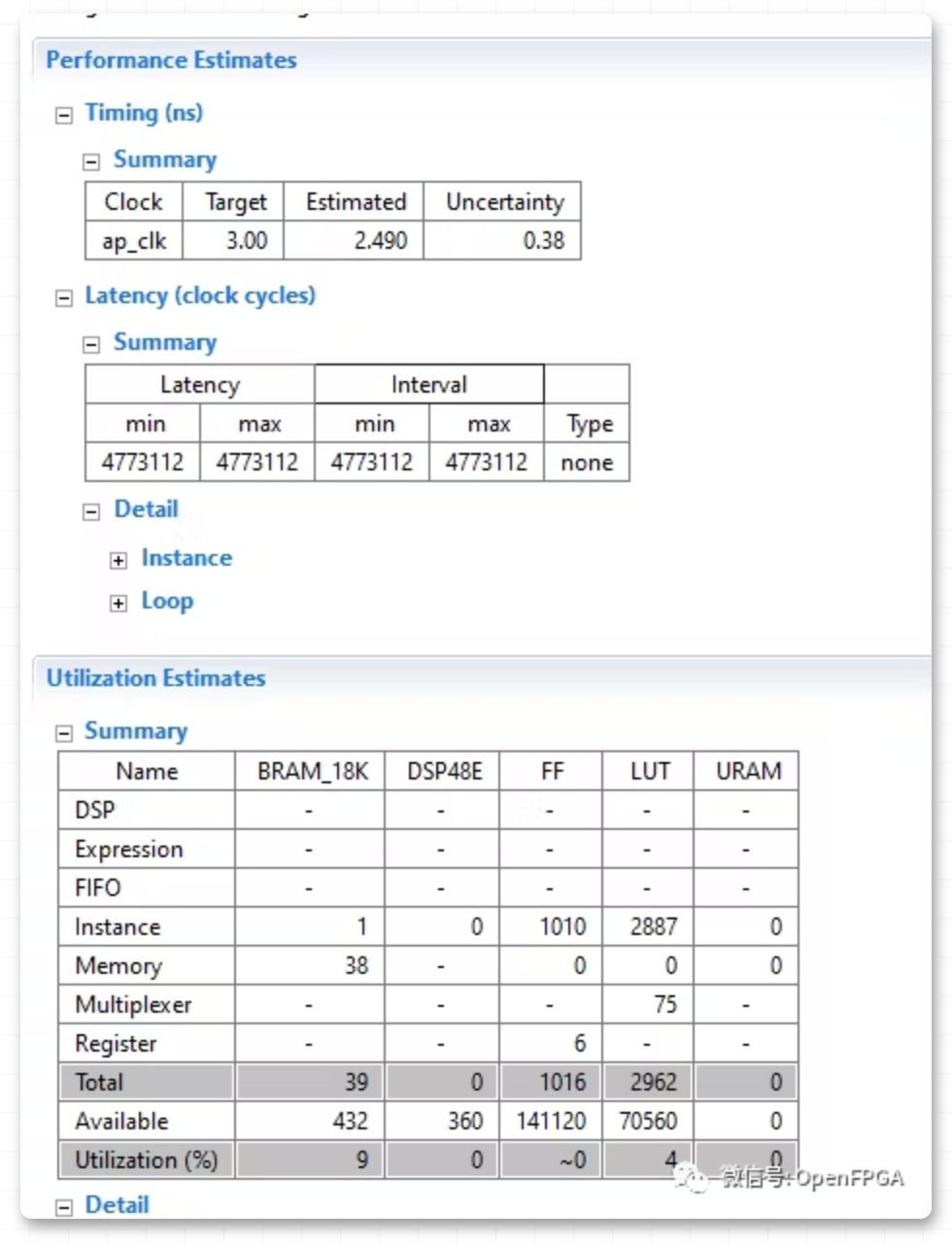

0 该项目包含使用高级综合 (HLS) 的 2D 中值滤波器算法的实现。该项目的目标是在不到 3 ms的时间内对测试图像进行去噪,同时消耗不到 25% 的可用 PL 资源。

2023-07-12 15:19:44 1540

1540

NoC是相对于SoC的新一代片上互连技术,从计算机发展的历史可以看到NoC 必将是SoC 之后的下一代主流技术,SoC 通常指在单一芯片上实现的数字计算机系统,总线结构是该系统的主要特征,由于其可以

2023-07-13 15:57:08 2181

2181

NoC是相对于SoC的新一代片上互连技术,从计算机发展的历史可以看到NoC 必将是SoC 之后的下一代主流技术

2023-07-13 15:56:43 1514

1514

Cadence员工MohamedNaeim博士曾在CadenceLIVE欧洲用户大会上做过一场题为《2D/3D热分析和三裸片堆叠设计实现》的演讲,本文将详细讲述该演讲内容。实验:两个裸片是否优于一个

2023-09-16 08:28:05 2057

2057

2023年9月18日, 由传智驿芯科技和Arteris联合举办的技术研讨会——“利用创新NoC技术驾驭复杂的片上系统(SoC)设计” 在深圳成功举办。西安交通大学任鹏举教授,Arteris中国区

2023-09-18 18:17:53 1403

1403

可以商用的集成全域硬2D NoC的FPGA器件,以每通道512Gbps的速率和超过2Tbps的总带宽来与所有系统接口和FPGA逻辑阵列互连。

2023-11-24 16:19:45 981

981 作为一个多年经验的机器视觉工程师,我将详细介绍2D和3D视觉技术的不同特点、应用场景以及它们能够解决的问题。在这个领域内,2D和3D视觉技术是实现自动化和智能制造的关键技术,它们在工业检测、机器人导航、质量控制等众多领域都有着广泛的应用。

2023-12-21 09:19:06 2688

2688 电子发烧友网站提供《利用Sitara AM57x处理器上的处理器SDK实现工业机器视觉的2D物体识别.pdf》资料免费下载

2024-10-10 09:36:06 0

0 本文介绍了一种利用液态金属镓(Ga)剥离制备二维纳米片(2D NSs)的方法。该方法在接近室温下通过液态镓的表面张力和插层作用破坏范德华力,将块体层状材料剥离成二维纳米片。此外,该过程还能在常温下

2024-12-30 09:28:08 1615

1615

亿源通科技在OFC 2025展会上展示了其最新研发的2D矩阵式M×N光纤阵列(2D FA)。这种高精度2D光纤阵列旨在满足对OCS(光路交换)系统日益增长的需求,OCS(光路交换)系统是下一代光网络

2025-04-03 11:25:58 918

918 随着台积电在 2011年推出第一版 2.5D 封装平台 CoWoS、海力士在 2014 年与 AMD 联合发布了首个使用 3D 堆叠的高带宽存储(HBM)芯片,先进封装技术带来的片上互连拓扑结构的改变和带来的集成能力的提升,成为当前片上互连技术发展的主要驱动因素。

2025-05-22 10:17:51 975

975

电子发烧友App

电子发烧友App

评论