zynq系列中的FPGA,都会自带两个iic设备,我们直接调用其接口函数即可运用。使用xilinx官....

为了尽快把新产品推向市场,数字系统的设计者需要考虑如何加速设计开发的周期。设计加速主要可以从“设计的....

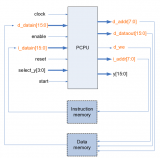

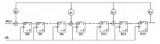

本文实现的CPU是一个五级流水线的精简版CPU(也叫PCPU,即pipeline),包括IF(取指令....

本文详细阐述了在一个testbench中,应该如何使用阻塞赋值与非阻塞赋值。首先说结论,建议在tes....

用最右边的字符下划线代表低电平有效,高电平有效的信号不得以下划线表示,短暂的有效信号建议采用高电平有....

DDR3 SDRAM(Double-Data-Rate ThreeSynchronous Dynam....

FIFO(First in First out)为先进先出队列,具有存储功能,可用于不同时钟域间传输....

AXI直接数值存取(Drect Memory Access,DMA)IP核在AXI4内存映射和AXI....

Video In to AXI4-Stream IP核用于将视频源(带有同步信号的时钟并行视频数据,....

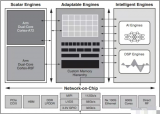

随着数字化时代的飞速发展,人工智能(AI)、大数据分析、自动驾驶等新兴领域的需求不断攀升。FPGA作....

本文简单介绍Zynq中的SPI控制器。本文将“master”称为“主机”;将“slave”称为“从机....

添加好ZYNQ7 Processing System IP核后,需要对其进行配置,双击弹出如下窗口。....

线网类型表示硬件电路元件之间实际存在的物理连线,有很多种:wire、tri、wor等等,当然日常使用....

CRC即循环冗余校验码:是数据通信领域中最常用的一种查错校验码,其特征是信息字段和校验字段的长度可以....

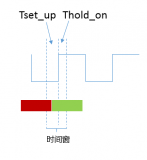

Vivado的时序约束是保存在xdc文件中,添加或创建设计的工程源文件后,需要创建xdc文件设置时序....

Verilog HDL(Hardware Description Language)是一种硬件描述语....

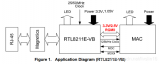

以太网MAC模块负责实现以太网MAC子层的功能,完成802.3ab的数据封装与解封。其同时负责适配硬....

本文将使用三段式状态机(Moore型)的写法来对DS18B20进行测温操作,以便了解DS18B20和....

AXI接口FIFO是从Native接口FIFO派生而来的。AXI内存映射接口提供了三种样式:AXI4....

ADC和DAC是FPGA与外部信号的接口,从数据接口类型的角度划分,有低速的串行接口和高速的并行接口....

复位电路也是数字逻辑设计中常用的电路,不管是 FPGA 还是 ASIC 设计,都会涉及到复位,一般 ....

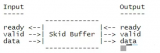

skid buffer(pipeline缓冲器)介绍 解决ready/valid两路握手的时序困....

DDR内存控制器是一个高度集成的组件,支持多种DDR内存类型(DDR2、DDR3、DDR3L、LPD....

调试,即Debug,有一定开发经验的人一定会明确这是设计中最复杂最磨人的部分。对于一个庞大复杂的FP....

增量式编码器是一种将位移信息转换成周期性电信号,再将电信号转换成脉冲计数的装置。

Xilinx的FIR IP核属于收费IP,但是不需要像 Quartus那样通过修改license文件....

1、在verilog中有时会用signed修饰符来修饰定义的数据,运算的时候也会用$signed()....

根据下面的时序图实现这个组合逻辑电路。

本文详细介绍了多种图像处理技术,包括RG/GB单通道提取、亮度和对比度调整、图像反转、均值滤波、高斯....

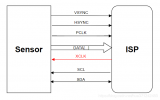

DVP(Digital Video Port) 是传统的sensor输出接口,采用并行输出方式,d数....