1、在verilog中有时会用signed修饰符来修饰定义的数据,运算的时候也会用$signed()任务来强制转换数据,那么signed的修饰是为什么呢,是为了区分有符号数和无符号数的加法和乘法吗?其实不是的,因为有符号数和无符号数据的加法强结果和乘法器结构是一样的,signed的真正作用是决定如何对操作数扩位的问题。

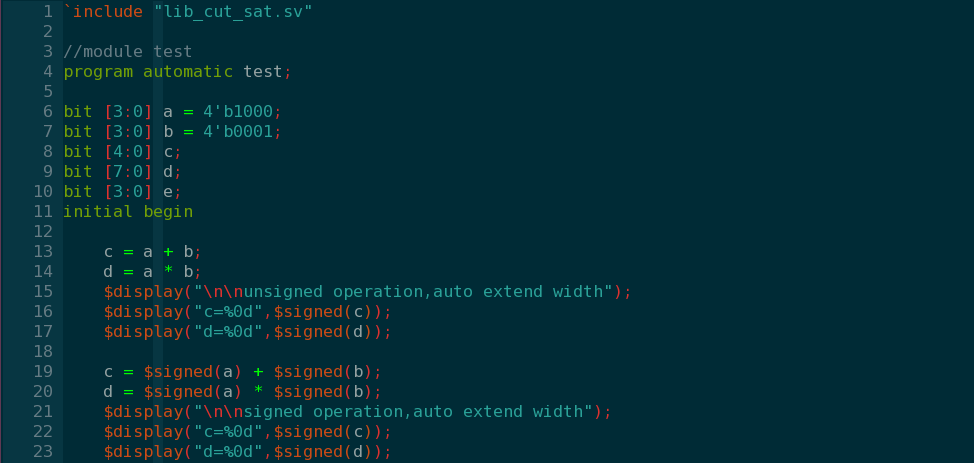

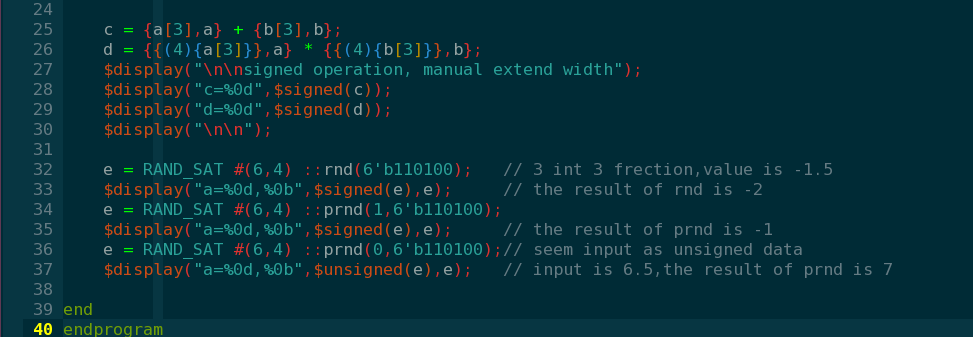

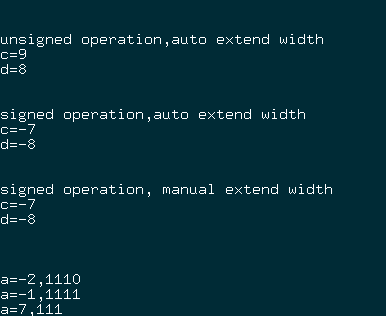

2、verilog中的加法和乘法操作前,会先对操作数据扩位成结果相同的位宽,然后进行加法或者乘法处理。比如a/b都为4位数据,c为5位数据,c = a + b,这个运算的时候会先把a和b扩位成5位,然后按照无符号加法进行相加。a/b没有被signed修饰的时候会按照无符号数的扩位方式进行扩位,即高位补0,加法的结果当然也是a、b为无符号数相加的结果。

3、如果想把a、b作为有符号数来相加,那么就得在a/b数据定义的时候用signed修改,或者在计算的时候用$signed()来修饰,这样在c = a + b,这个运算开始的扩位就会按照有符号数的方式进行扩位,在高位补符号位,加法得出的结果就是a、b视为有符号数的结果。当然c要视为有符号数据。

$signed()函数

返回有符号的值,值得注意的是verilog中的负数其实是{1’b1,pos_num},而并非高级语言中的补码。使用中最好通过增加$signed{1’b符号,正数}来实现转换以避免错误。

此外在对signed wire 或signed reg 赋值时,右侧的所有变量最好全部加上$signed函数转换,以防止遗漏,造成数据错误

signed变量移位操作时最好使用<<<和>>>,防止对符号位进行操作,导致数据出错

-

Verilog

+关注

关注

31文章

1374浏览量

114718

原文标题:Verilog 中signed和$signed()的用法

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

昉·星光开发板气压与高度测量

使用 VisionFive 2 上的气压传感器测量高度

变频器的特殊用法

通过2的幂次进行除法和取余数快捷方法优化

C语言的printf基本用法介绍

在verilog testbench中运行测试用例时,运行到make run_test出错怎么解决?

使用NucleiStudio生成tb仿真需要的.verilog文件

定点数表示实数的方法以及定点数在硬件上的运算验证

rt-thread studio怎么设置才能让char变量是真正的有符号类型?

【汇思博SEEK100开发板试用体验】3/第一次使用OpenHarmony

用TXT编辑器打开十六进制文件,如何知道校验和值?

UIAbility组件基本用法说明

verilog模块的调用、任务和函数

Verilog中signed和$signed()的用法

Verilog中signed和$signed()的用法

评论