点击上方 蓝字 关注我们 系统的复位对于系统稳定工作至关重要,最佳的复位方式为:异步复位,同步释放。....

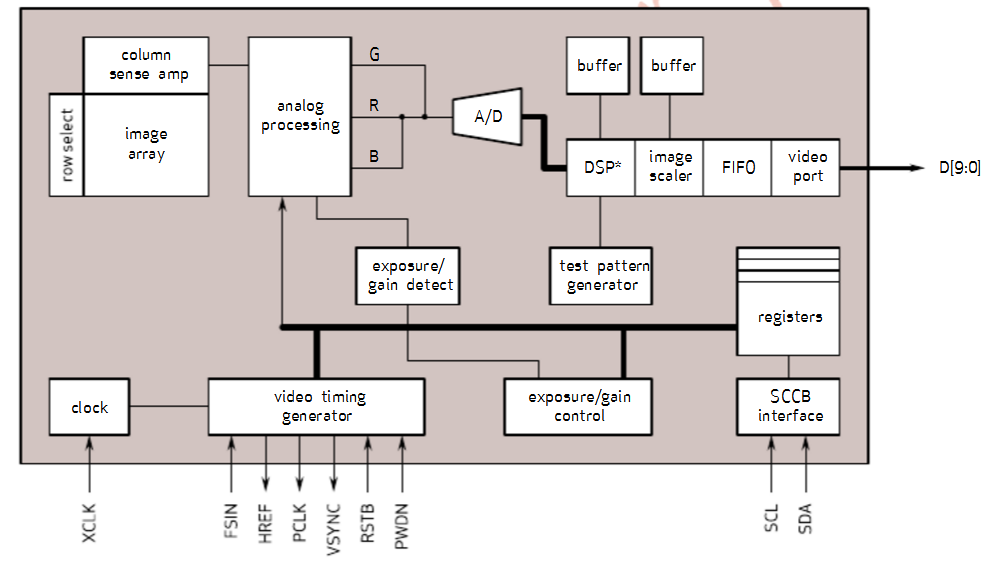

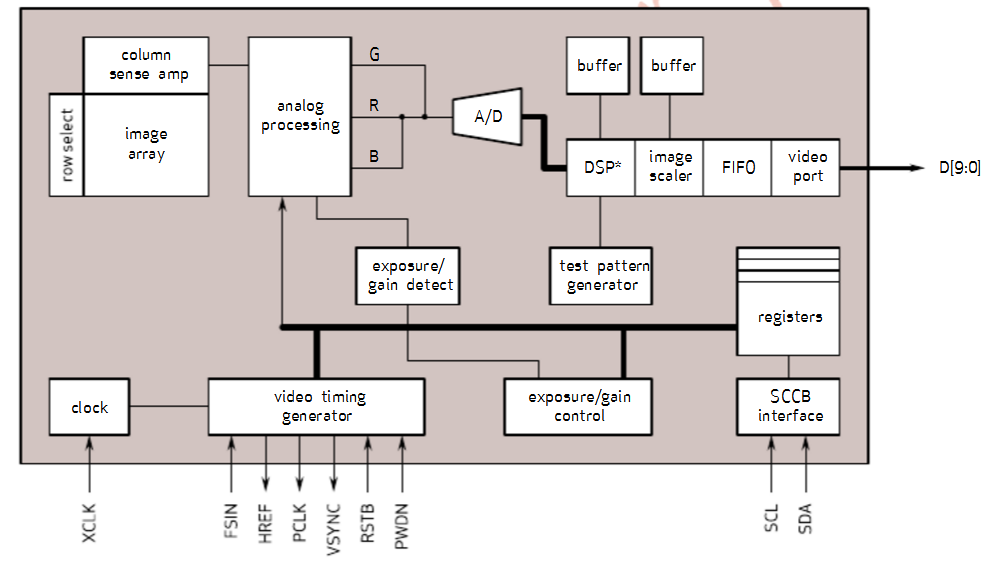

目前FPGA用于图像采集 传输 处理 显示应用越来越多,主要原因是图像处理领域的火热以及FPGA强大....

点击上方 蓝字 关注我们 1 数字IC(ASIC)设计流程: IC设计分为前端和后端。前端设计主要将....

FPGA以擅长高速并行数据处理而闻名,从有线/无线通信到图像处理中各种DSP算法,再到现今火爆的AI....

点击上方 蓝字 关注我们 一、前言 在数字电路中,序列检测器(Sequence Detector)是....

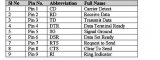

点击上方 蓝字 关注我们 ADC硬件特性分析 首先必须通过datasheet分析其核心参数、接口定义....

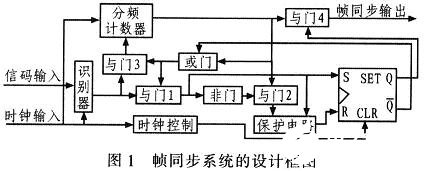

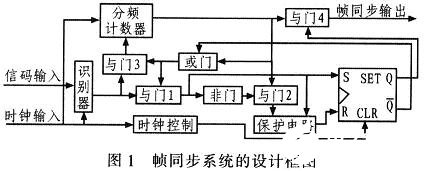

1、 引言 数字通信时,一般以一定数目的码元组成一个个“字”或“句”,即组成一个个“帧”进行传输,因....

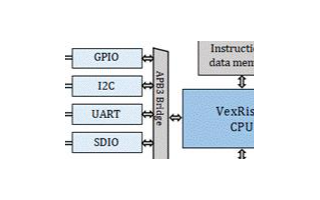

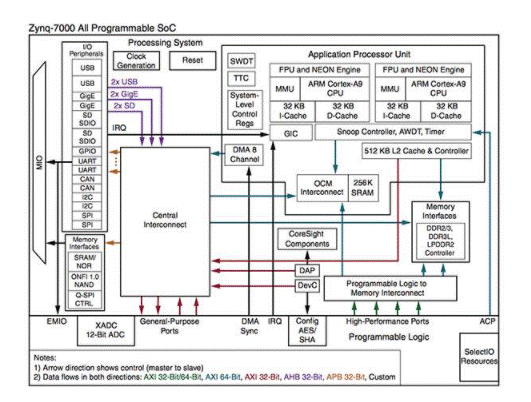

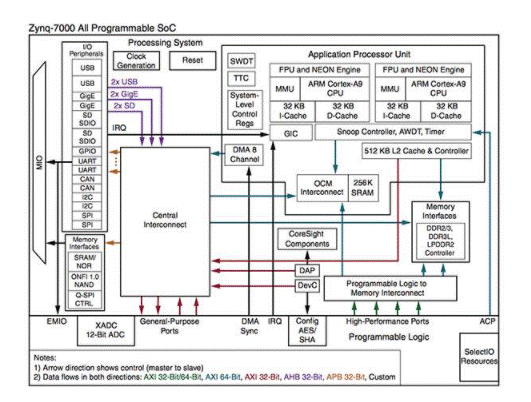

MCU 对应用主导地位的挑战已经开始。具有片上固定功能处理子系统的现场可编程逻辑器件 (FPGA),....

人工智能(AI)长期以来一直是科幻作家和学者的主题。将人脑的复杂性复制到计算机中的挑战催生了新一代的....

有一个有趣的现象,众多数字设计特别是与FPGA设计相关的教科书都特别强调整个设计最好采用唯一的时钟域....

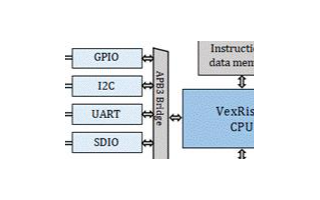

当今的设计工程师受到面积、功率和成本的约束,不能采用GHz级的计算机实现嵌入式设计。在嵌入式系统中,....

现场可编程门阵列(FPGA)具有低功耗、高性能和灵活性的特点。FPGA神经网络加速的研究正在兴起,但....

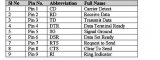

即使USB出现,串行端口也不会消亡。对于术语“串行端口”,我们通常指的是或多或少符合RS-2....

即使USB出现,串行端口也不会消亡。对于术语“串行端口”,我们通常指的是或多或少符合RS-232 标....

1 Overview 与传统的并行实现方法相比,基于串行I/O的设计具有很多优势,包括:器件引脚数较....

点击上方 蓝字 关注我们 NOR闪存已作为FPGA(现场可编程门列阵)的配置器件被广泛部署。其为FP....

点击上方 蓝字 关注我们 有时, 微控制器 本身可以完全吸收设计的所有功能要求。对于绝大多数嵌入式系....

点击上方 蓝字 关注我们 FPGA工作原理与简介 如前所述,FPGA是在PAL、GAL、E....

点击上方 蓝字 关注我们 随着软件定义无线电平台在军事航空航天领域以及近在一些消费无线电和 电子 ....

点击上方 蓝字 关注我们 FPGA(Field-Programmable Gate Array),即....

芯片设计和验证工程师通常要为在硅片上实现的每一行RTL代码写出多达10行测试平台代码。验证任务在设计....

点击上方 蓝字 关注我们 芯片设计和验证工程师通常要为在硅片上实现的每一行RTL代码写出多达10行测....

点击上方 蓝字 关注我们 荷图像可视化是深空探测任务中的重要需求,但受信道带宽的限制,无法实时传输所....

点击上方 蓝字 关注我们 任何信息需要借助声、光、电信 号进行传递,由于光信号和电信号在海水中的衰减....

点击上方 蓝字 关注我们 在电阻抗多频及参数成像技术中正交序列数字解调法的抗噪性能对信号每周期的采样....

现代飞机座舱显示技术的发展日新月异,需要显示各种传感器信息的数据已经达到海量规模。飞行员在不同飞行时....

串行接口常用于芯片至芯片和电路板至电路板之间的数据传输。随着系统带宽不断增加至多吉比特范围,并行....

点击上方 蓝字 关注我们 至芯科技FPGA就业培训班——助你步入成功之路 至芯科....

点击上方 蓝字 关注我们 医学超声诊断成像技术大多数采用超声脉冲回波法,即利用探头产生超声波进入人体....

点击上方 蓝字 关注我们 1 引言 DDS同DSP(数字信号处理)一样,是一项关键的数字化技术。DD....