本文详细介绍了多种图像处理技术,包括RG/GB单通道提取、亮度和对比度调整、图像反转、均值滤波、高斯滤波、图像锐化、中值滤波、阈值分割、边缘检测(Sobel算子)、图像膨胀与腐蚀、开运算与闭运算、Tophat形态学滤波、RAW8转RGB888、彩色图像均值滤波、Alpha背景叠加、直方图灰度拉伸算法以及自动白平衡算法。每种算法都提供了实现方法和相关公式,涵盖了图像处理的核心概念和技术。

1、RG/GB单通道提取,采用2x2阵列

其实现方法,用ram缓存两行图像数据,对缓存的数据进行间隔4个数据读取,以此一个固定的数据替换其余三个颜色值

2、亮度增加

其公式为:

Q = a * i + b

其中i为输入原像素值,a为调节对比度,b为调节亮度

实现方法为:只需将原像素值加上需要增加亮度的值即可(注:不要溢出)

3、对比度增加

其公式为:

Q = a * i +b

其中i为输入原像素值,a为调节对比度,b为调节亮度

实现方法:只需将原像素值乘上对比度值即可(注:不要溢出)

4、图像反转

其公式为:

Q = 255 - i;

其中i为原像素值

实现方法:将图像值的最大值减去原像素值

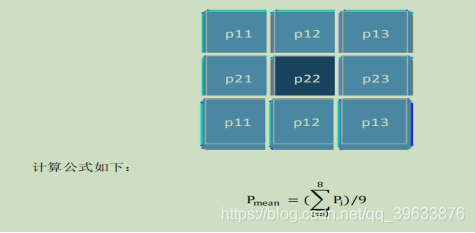

5、均值滤波

采用的3x3矩阵,先缓存三行图像数据,在对数据进行相加,取均值

其除法部分可以转化移位运算:

实现过程:

1024 / 9 = 113;

则可以让其矩阵取和值乘以113,在进行右移10位,则得出需要均值

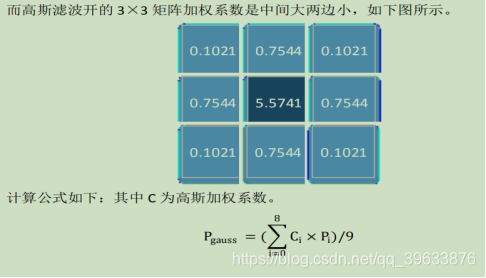

6、高斯滤波

实现方法:

对所有的权值乘以1024,在将权值与矩阵像素相乘并累加和,并在按照10249=113的原理,让其和乘以113,在对其值进行右移20位,则该值就是要求的最终值

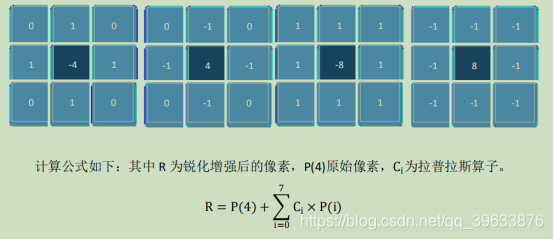

7、图像锐化

图像锐化,采用的是拉普拉斯算子,其算子模板如下:

采用第二个算子模板,其实现方法如下:

其实现方法:将算子模块中的值分成两部分,一部分是正值,另一部分是负值, 1、在将正值和负值进行比较,如果正值大于负值,则正值减去负值,在与p(4)像素加

2、在将正值和负值进行比较,如果正值小于负值,则负值减去正值,在p(4)像素值减去该值

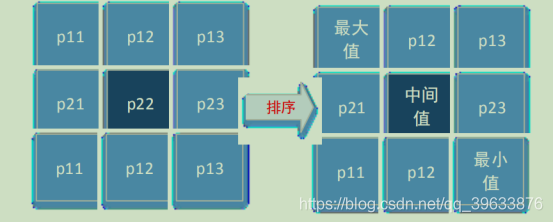

8、中值滤波

其模型如下:

其实现方法:

设置9个cnt值做排序标识,让矩阵中的值对另外8个值进行比较,其中标识值为4的,就代表其值为中间值

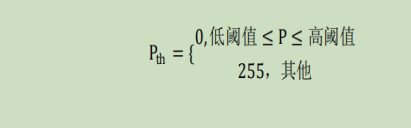

9、阈值分割

其公式如下:

设置阀值区间,当在这个阀值区间内,则该像素值转化为0输出,不在这个阀值区间内的像素则输出255或其他定义的值

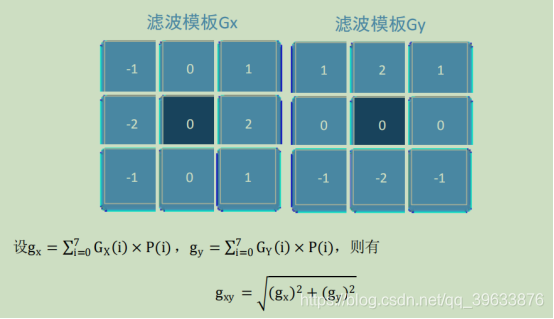

10、边缘检测(sobel)

其sobel算子3x3模型如下:

公式部分补充:

得到gxy值后,根据设置的阀值,当大于该阀值,则该像素输出为16’01,否则为8’hff,将像素二值化

其实现过程:

1、将模板Gx分为正值和负值累加,当正值大于负值时,则正值减去负值,否则是负值减去正值

2、同理模板Gy也是如此,然后在得出的值分别进行平方,在进行累加求和

3、最后对该值进行开平方(开平方可用cordic算法转化sqrt,也可以调用ip核)

4、得到开平方的值进行与阀值比较,将像素二值化

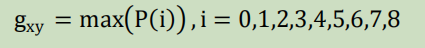

11、图像膨胀

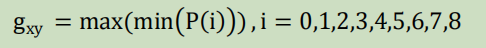

在sobel检测之下,其公式:

求像素的最大值,进行输出

其矩阵模型为3x3

实现方法:

设置9个cnt值做排序标识,让矩阵中的值对另外8个值进行比较,其中标识值为8的,就代表其值为最大值

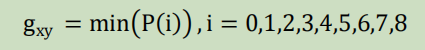

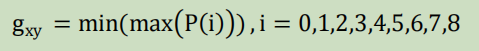

12、图像腐蚀

在sobel检测之下,其公式为:

求像素的最大值,进行输出

其矩阵模型为3x3

实现方法:

设置9个cnt值做排序标识,让矩阵中的值对另外8个值进行比较,其中标识值为0的,就代表其值为最小值

13、开运算

其原理过程是先腐蚀后膨胀的过程,其公式:

其实现过程:

在矩阵3x3中:

1、先进行缓存3行像素点(640)

2、在对3行像素点安顺序各取三个值进行取最小值输出像素

3、将输出最小值的像素在进行缓存3行(640)

4、在对这3行像素点安顺序各取三个值,进行取最大值,输出像素值,则该算法完成

14、闭运算

其原理过程是先膨胀后腐蚀的过程,其公式:

其实现过程:

在矩阵3x3中:

5、先进行缓存3行像素点(640)

6、在对3行像素点安顺序各取三个值进行取最大值输出像素

7、将输出最大值的像素在进行缓存3行(640)

8、在对这3行像素点安顺序各取三个值,进行取最小值,输出像素值,则该算法完成

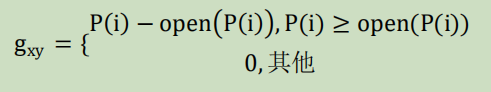

15、Tophat 形态学滤波

其公式为:

矩阵为:3x3

其工作原理是,先对3x3像素矩阵进行开运算,比较值取p(4),当p(4)>=open(p(i))时,则Gxy = p(4) - open(p(i)),否则Gxy = 0 或者其他定义值

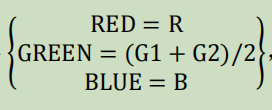

16、RAW8转RGB888

选取矩阵:2x2

Cmos像机结构:GB/RG

以G2为基准点,则该公式为:

则实现方法:

1、先缓存2行数据(640)

2、各读取2个数据

3、对值进行分配为:

偶数行偶数列、偶数行奇数列、奇数行偶数列、奇数行奇数列

4、输出各组8位颜色

17、彩色图形进行均值滤波

矩阵:3x3

先将RAW8转RGB888三原色输出,然后在对其每个原色进行缓存3行,在进行取和输出,该和值乘(1024/9)113值,最后将该值进行右移10位,则是最终像素输出

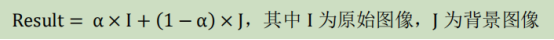

18、Alpha 背景叠加

其效果实现是出现背景半透明状态

公式为:

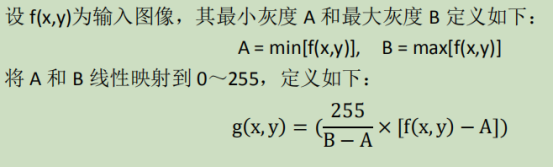

19、直方图灰度拉伸算法

矩阵:2x2

实现方法:

缓存2个小于255的数,为最小值;缓存2个大于0的数为最大值;进行比较,用最大值减去最小值。做为查找表的标号;255/(B-A)部分做成查找表e

最后g(x,y)= e * (f(x,y)-min值)

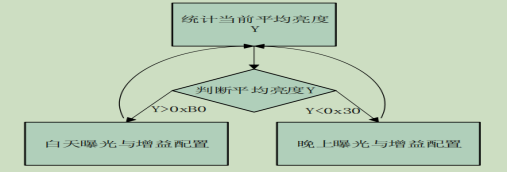

20、白/晚自动曝光与增益算法

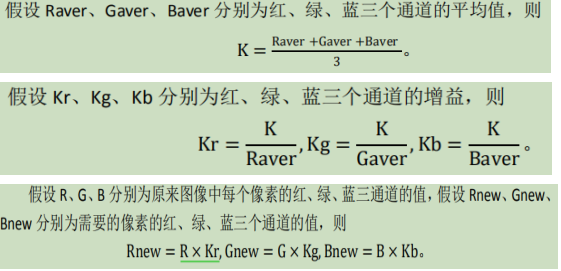

21、自动白平衡算法

百平衡算法有:灰度世界法、完美反射法、动态阀值法

现实现方法为:灰度世界法

原理:灰度世界法(Gray World)是以灰度世界的假设为基础的,假设一张图片具有大量的色彩变化,RGB 三分量的平均值趋于同一个灰度值 K。下面给出 K 的计算方法。

则公式为:

实现思路:

1、由于MT9V011摄像机有4个通道,将一帧的图像数据按照奇偶行列将4个通道进行分配累加取和

2、在对4个通道的数据进行取平均值,并且要除以4,每个通道的数据占一帧图像的四分之一

3、在将4个通道的数据累加取和,并对其进行取平均值K

4、将4个通道的数据,都进行取倒数的查找表s

5、输出最终值:

R = R(原)ks

G= G(原)ks

B = B(原)ks

原文:

https://blog.csdn.net/qq_39633876

-

FPGA

+关注

关注

1663文章

22494浏览量

638988 -

图像处理

+关注

关注

29文章

1344浏览量

59691 -

算法

+关注

关注

23文章

4800浏览量

98515

原文标题:FPGA图像处理算法整合

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

综合图像处理硬件平台设计资料:2-基于6U VPX的双TMS320C6678+Xilinx FPGA K7 XC7K420T的图像信号处理板

多场景智能拍摄实战:摄像头模块集成与调试指南!

【VPX650 】青翼凌云科技基于 VPX 系统架构的 VU13P FPGA+ZYNQ SOC 超宽带信号处理平台

中科亿海微Link-Sea-H6A图像处理套件

【VPX637】青翼凌云科技基于 XCKU115 FPGA+ZU15EG MPSOC 的 6U VPX 双 FMC 接口通用信号处理平台

【 VPX638】青翼凌云科技基于KU115 FPGA+C6678 DSP的6U VPX双FMC接口通用信号处理平台

FPGA上的图像处理算法集成与优化

FPGA上的图像处理算法集成与优化

评论