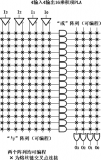

基于FPGA的电子按键密码锁设计

电子密码锁与传统密码锁相比,具有安全性高、成本低、易操作等诸多优点。正因如此,电子密码锁近年来发展迅....

FPGA管脚调整的注意事项

点击上方 蓝字 关注我们 随着FPGA的不断开发,其功能越来越强大,也给其布线带来了很大的便捷性—管....

基于FPGA的CAN总线通信节点设计

点击上方 蓝字 关注我们 摘要:以FPGA 代替传统的单片机和外围扩展芯片, 给出了CAN 总线通信....

安防领域典型AI芯片有三种,为何偏偏是FPGA称雄?

AI技术发展至今,安防行业热度毋庸赘言。在安防智能化进程中,摄像头、交换机、硬盘刻录机、各类服务器等....

从硬件角度讨论FPGA开发框架

点击上方 蓝字 关注我们 FPGA采用了逻辑单元阵列概念,内部包括可配置逻辑模块、输出输入模块和内部....

使用FPGA实现高效并行实时上采样

点击上方 蓝字 关注我们 采样就是采集模拟信号的样本。通常采样指的是下采样,也就是对信号的抽取。其....

基于FPGA的DDR3多端口读写存储管理系统设计

点击上方 蓝字 关注我们 机载视频图形显示系统主要实现2D图形的绘制,构成各种飞行参数画面,同时叠加....

基于FPGA的无线通信安全协议

点击上方 蓝字 关注我们 引言 小型机器人足球融合机械设计、自动控制、无线通信、图像识别、智....

FPGA工程师不得不知的FPGA设计经验

点击上方 蓝字 关注我们 在IC工业中有许多不同的领域,IC设计者的特征也会有些不同。在A领域的一个....

利用FPGA开发板进行ASIC原型开发的技巧

ASIC设计在尺寸和复杂性上不断增加,现代FPGA的容量和性能的新进展意味着这些设计中的2/3能够使....

FPGA系统中三种方式减少亚稳态的产生

点击上方 蓝字 关注我们 1.1 亚稳态发生原因 在 FPGA 系统中,如果数据传输中不满足 触发器....

使用混合信号示波器进行高效 I2C 总线调试

Inter-IC (I2C) 总线 4.0 版本广泛应用于嵌入式系统设计,并已在数以千计的 集成电路....

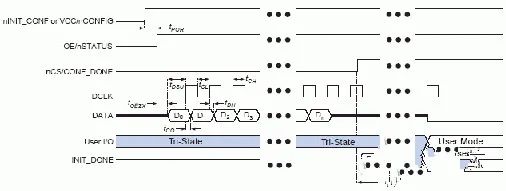

在微处理器系统里实现两种简单的FPGA配置方式

可编程逻辑器件 (PLD)广泛应用在各种电路设计中。基于查找表技术、SRAM工艺的大规模PLD/FP....

基于FPGA实现通用异步收发器基本功能的应用设计

点击上方 蓝字 关注我们 通用异步收发器(Universal Asynchronous Receiv....

采用FPGA和CMOS数字传感器实现图像监测系统的设计

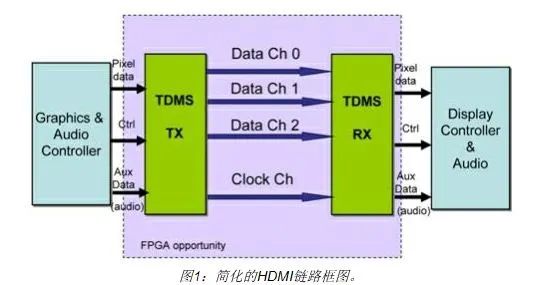

图像监测在许多领域有着广泛的应用,目前已经安装上的图像监测系统大约60%沿用早期的摄像头加电视....