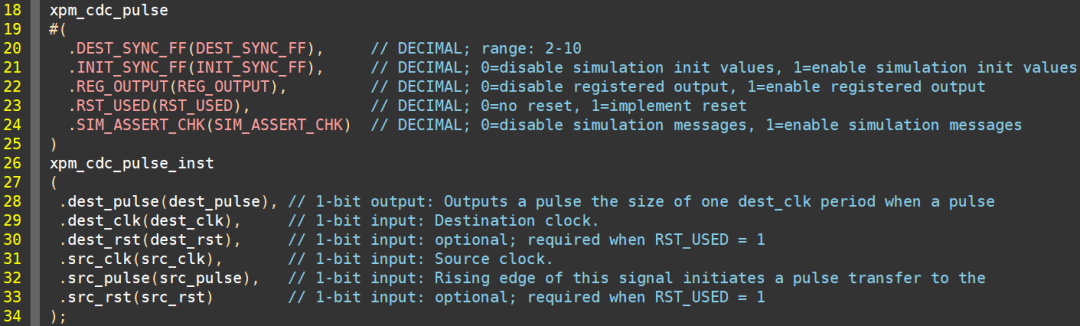

对于脉冲信号跨时钟域,XPM_CDC提供了模块xpm_cdc_pulse,如下图所示。该模块有5个参数,其中参数DEST_SYNC_FF用于确定级联触发器的个数;INIT_SYNC_FF用于确定仿真时是否使用触发器初始值;

参数REG_OUTPUT用于确定是否对最终输出信号寄存;参数RST_USED用于确定是否使用复位信号;参数SIM_ASSERT_CHK则用于确定是否显示仿真信息。从输入/输出端口来看,源端时钟域的输入信号为src_pulse和src_rst;

目的端时钟域的输入信号为dest_rst,输出信号为dest_pulse(src_pulse跨时钟域后的结果)。

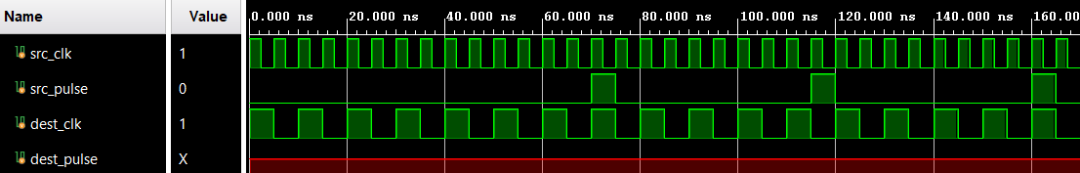

这些参数对仿真以及实际电路都有较大影响。如果参数INIT_SYNC_FF为0,同时RST_USED也为0,这就表明了仿真时不能使用同步寄存器链路的初始值,同时也没有复位信号对其复位,这样仿真时就会出现未知态,如下图所示。

审核编辑 :李倩

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

模块

+关注

关注

7文章

2849浏览量

53433 -

电路设计

+关注

关注

6745文章

2793浏览量

220206 -

触发器

+关注

关注

14文章

2065浏览量

63545 -

脉冲信号

+关注

关注

6文章

409浏览量

38679 -

时钟域

+关注

关注

0文章

53浏览量

10063

原文标题:跨时钟域电路设计(4):单周期脉冲信号如何跨时钟域

文章出处:【微信号:Lauren_FPGA,微信公众号:FPGA技术驿站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

跨时钟域电路设计:单周期脉冲信号如何跨时钟域

跨时钟域电路设计:单周期脉冲信号如何跨时钟域

评论