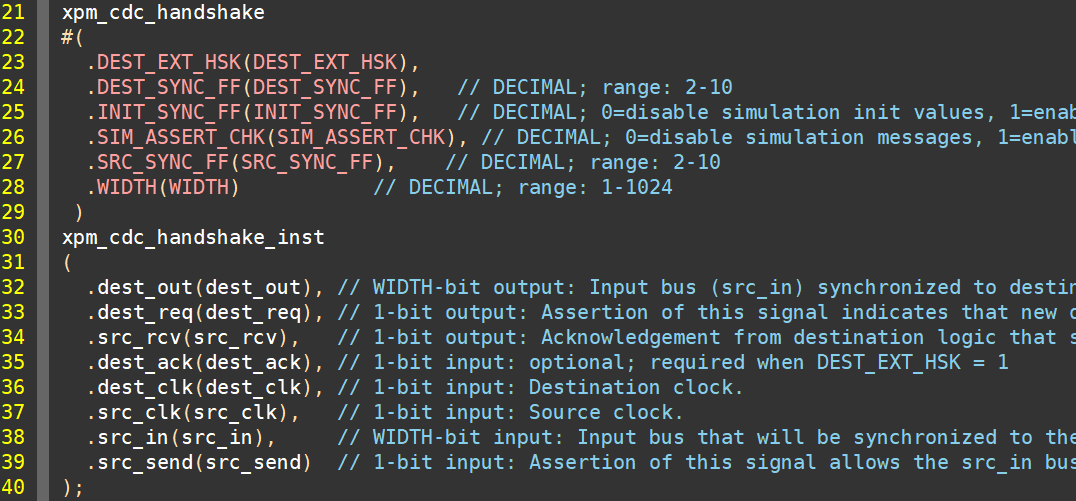

对于多位宽数据,我们可以采用握手方式实现跨时钟域操作。该方式可直接使用xpm_cdc_handshake实现,如下图所示。xpm_cdc_handshake提供了6个参数。

其中DEST_EXT_HSK用于决定握手信号是内部生成还是来自于该模块的外部;DEST_SYNC_FF决定了目的端控制信号对应的级联触发器个数;INIT_SYNC_FF决定了仿真时是否使用触发器的初始值;SIM_ASSERT_CHK用于判定是否检查仿真过程中可能的潜在问题;SRC_SYNC_FF决定了源端控制信号对应的级联触发器个数;WIDTH决定了传输数据的位宽。

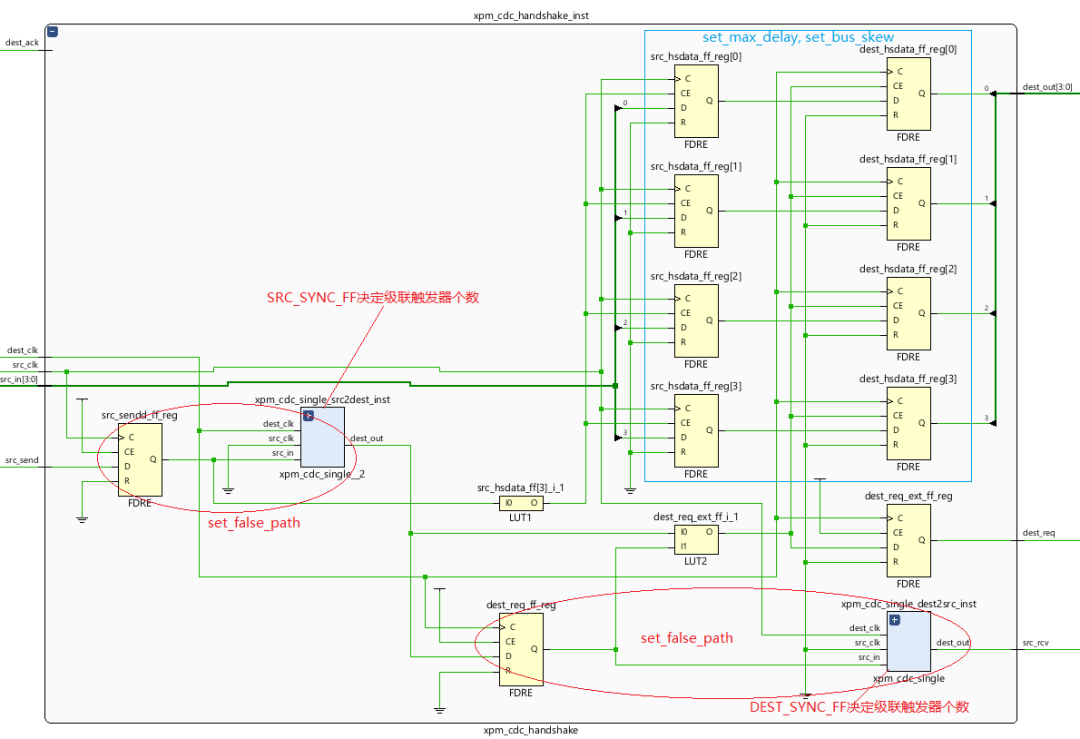

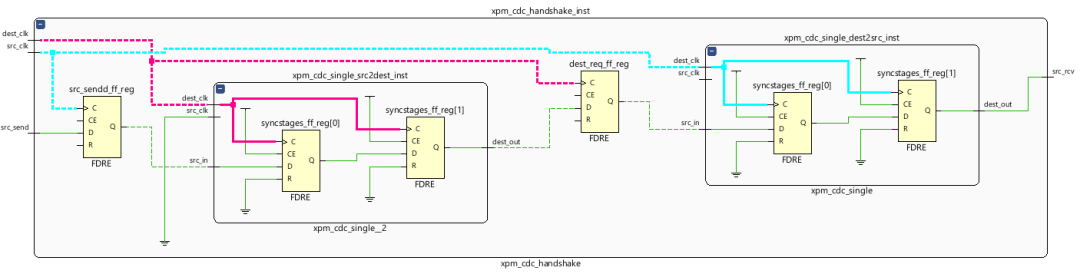

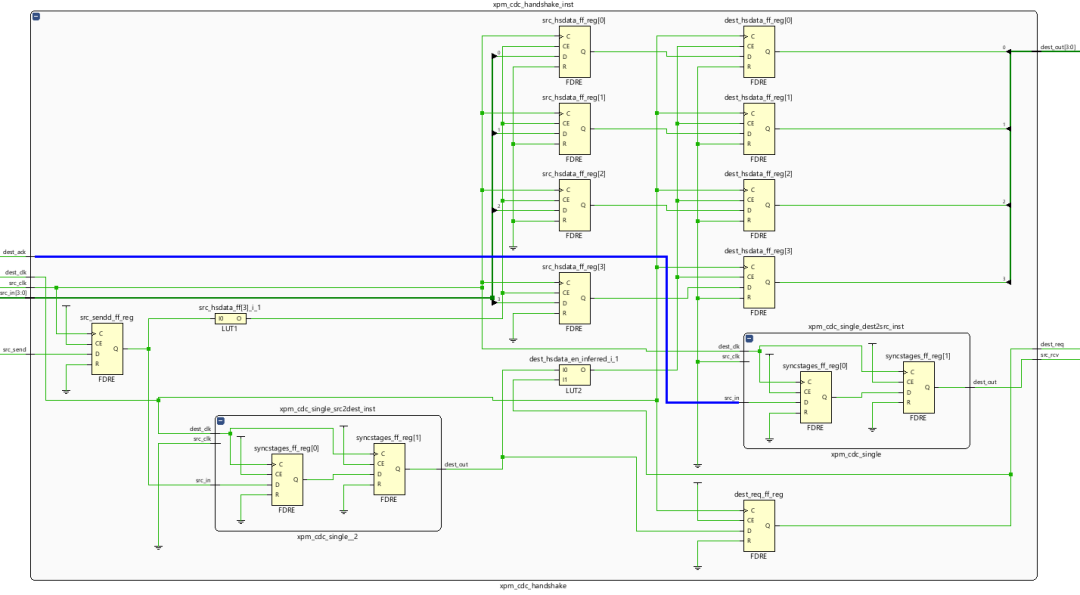

假定DEST_EXT_HSK为0(握手信号由内部生成),DEST_SYNC_FF和SRC_SYNC_FF均为2,WIDTH为4,综合后的电路结果如下图所示。可以看到设计使用了xpm_cdc_single,用于实现控制信号src_send的跨时钟域操作,这也就意味着src_send为高有效时要确保可以被接收端时钟稳定地采样到至少两次。

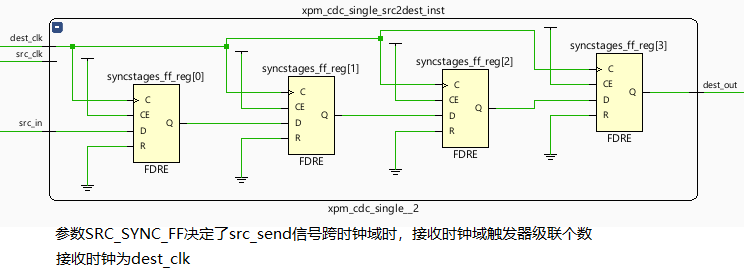

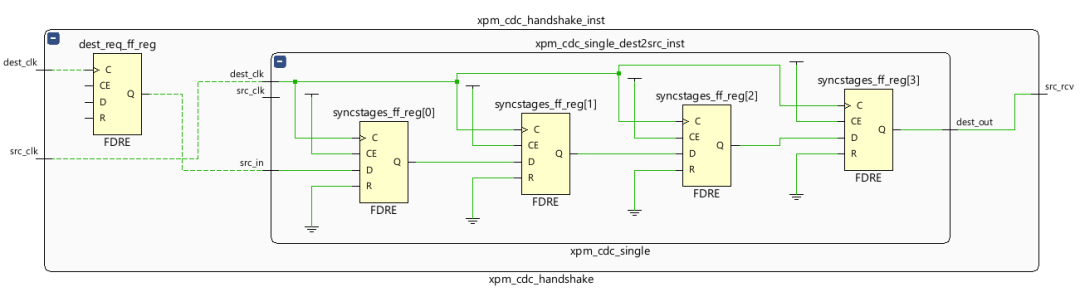

同时也不难理解SRC_SYNC_FF决定了src_send从发送时钟域到接收时钟域所需的级联触发器个数。下面第二张图片就显示了SRC_SYNC_FF为4时的电路。下面第三章图显示了DEST_SYNC_FF为4时的电路。

我们单独把控制信号src_send提取出来,看看src_send是如何从发送时钟域到接收时钟域然后又回到发送时钟域生成src_rcv信号,如下图所示。图中淡紫色为接收时钟,浅蓝色为发送时钟,src_send从输入到最终产生src_rcv信号共经历了6个触发器,两次跨时钟域操作。src_send为高时,表明发送端有待发送数据,src_rcv为高时表明接收端已接收到数据,意味着跨时钟域操作完成。

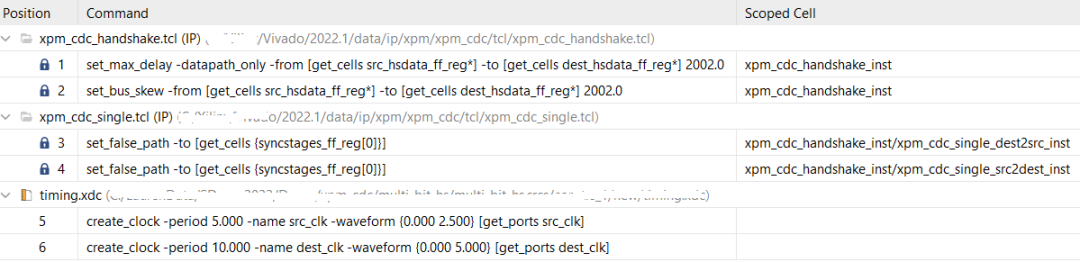

从约束层面看,该模块使用了set_false_path,set_max_delay和set_bus_skew三种约束,如下图所示。但其实set_max_delay和set_bus_skew的延迟值都很大,所以可以认为与set_max_delay等效。

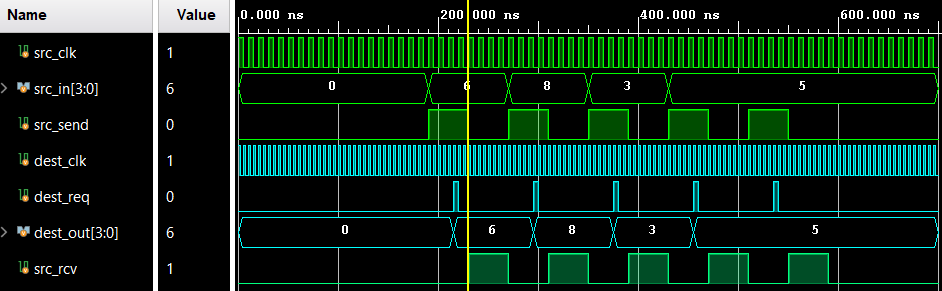

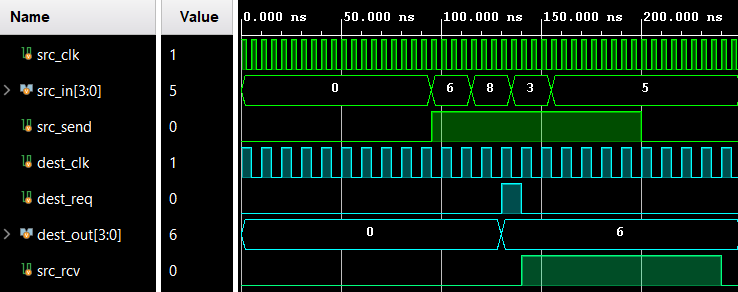

从仿真角度看,我们先看从慢时钟域到快时钟域,如下图所示。这里需要注意的是dest_req输出脉宽为一个接收时钟域脉宽,故该信号可用于最终数据(跨时钟域之后)的有效标记信号。

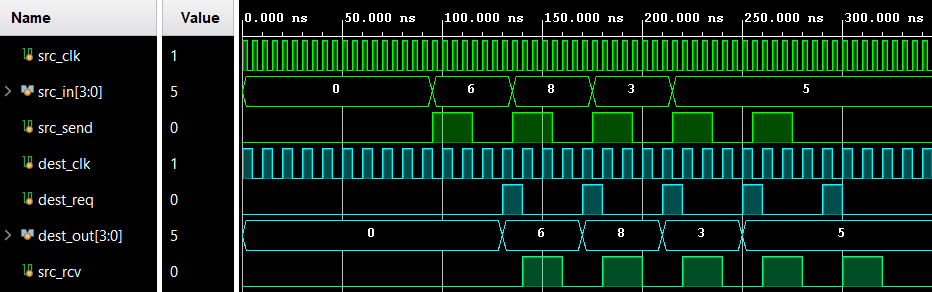

同样,该模块也支持从快时钟域到慢时钟域的跨时钟域的操作,如下图所示。

既然是握手方式,那么就意味着每发送一个数据,就要发送一个与之同步的有效标记信号(src_send),当接收端接收到该信号时,开始处理,接收完毕发送src_rcv给发送端,表明数据被接收到。这样看来,握手方式因为“握手”的存在而不能连续发送数据,如下图所示,可以看到连续发送造成数据丢失。

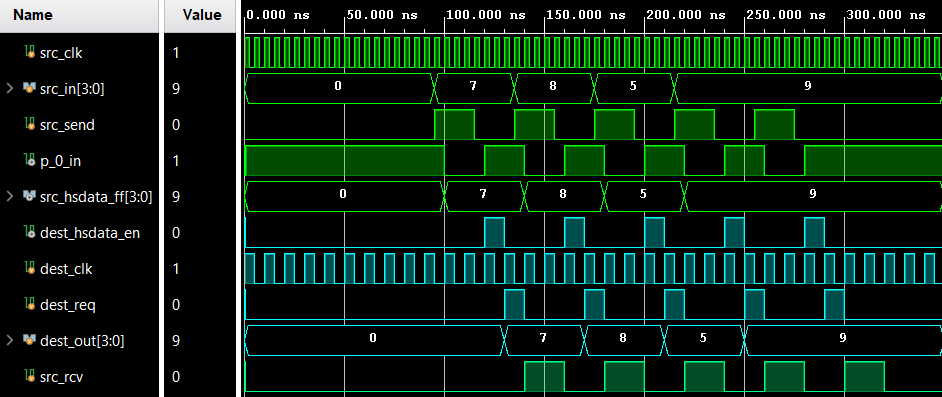

从综合后的仿真来看,进一步理解“握手”,如下图所示,我们将数据路径上发送端和接收端触发器的使能信号添加到波形窗口里。其中p_0_in为发送端使能信号,对应的输出数据为src_hsdata_ff,dest_hsdata_en为接收端使能信号。

如果参数DEST_EXT_HSK为1,表明外部提供接收应答信号,综合结果如下图所示。图中蓝色高亮为信号dest_ack,该信号经跨时钟域处理输出src_rcv给接收端,这正是与内部产生握手信号电路的区别。

综上所述,可以看到“握手”方式需要发送端和接收端通过握手信号src_send和src_rcv或dest_ack来表明发送端有数据等待发送或接收端已接收到数据,“握手”一来一回就意味着发送端不能每个时钟周期都发送数据,发送数据率必然低于时钟频率。同时,握手方式也无法对待发送数据进行缓存。好处是这种方式仅仅消耗触发器和查找表资源,资源用量比较少,电路比较简单。

审核编辑:刘清

-

FPGA

+关注

关注

1664文章

22503浏览量

639273 -

时钟

+关注

关注

11文章

1999浏览量

135236 -

触发器

+关注

关注

14文章

2065浏览量

63559 -

SRC

+关注

关注

0文章

63浏览量

18772 -

时钟域

+关注

关注

0文章

53浏览量

10063

原文标题:跨时钟域电路设计(6):多位宽数据通过握手方式跨时钟域

文章出处:【微信号:Lauren_FPGA,微信公众号:FPGA技术驿站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

多位宽数据通过握手方式跨时钟域

多位宽数据通过握手方式跨时钟域

评论