通常情况下,一旦创建好Vivado工程,添加了相应的RTL文件,Vivado会自动找到设计的顶层文件,正确地显示设计层次。在这个过程中,Vivado会自动分析文件的编译顺序。那么是否可以手动调整文件的编译顺序呢?答案是肯定的。

这里我们以调整仿真文件编译顺序为例进行说明。

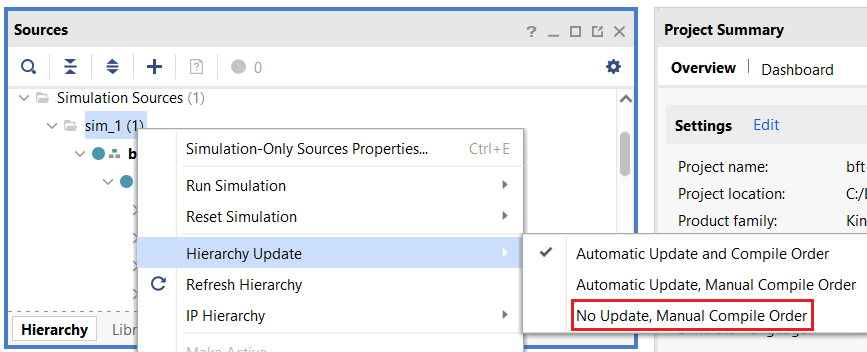

第一步:在Sources窗口中,选择sim_1文件夹,点鼠标右键,在弹出窗口中依次按如下方式选择。

No Update, Manual Compile Order。

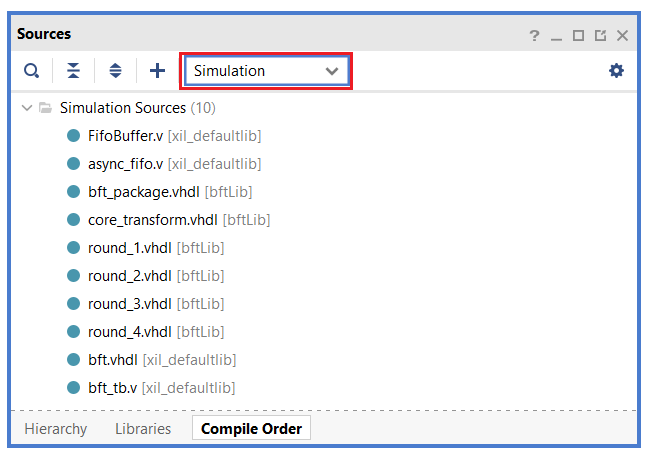

第二步:切换到Compile Order菜单下,并将下图红色方框中的内容切换为Simulation。

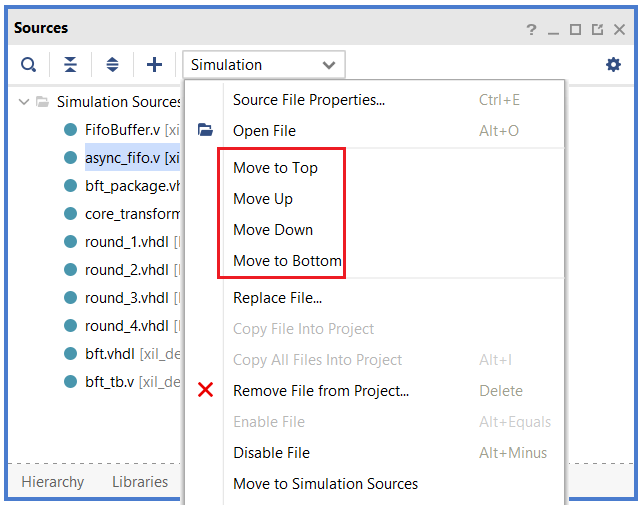

第三步:选中需要调整的文件,点击鼠标右键,在弹出窗口中根据需要选择相应的红色方框内的选项。位于最顶层的,将是第一个被编译的。至此,编译顺序调整完毕。

实际上,Vivado还提供了命令report_compile_order用于查看编译顺序。通过选项-used_in(该选项有3个可选值:synthesis、simulation和implementation)可查看综合、仿真或布局布线阶段的文件编译顺序,通过选项-constraints可查看约束文件的编译顺序。

审核编辑:汤梓红

-

文件

+关注

关注

1文章

598浏览量

26124 -

RTL

+关注

关注

1文章

395浏览量

62913 -

编译

+关注

关注

0文章

696浏览量

35298 -

Vivado

+关注

关注

19文章

860浏览量

71430

原文标题:Vivado里如何手动调整编译顺序

文章出处:【微信号:Lauren_FPGA,微信公众号:FPGA技术驿站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

怎么改变模拟编译顺序?

使用scons编译时,需要怎么做才能输出gcc的完整编译信息呢?

Vivado中的Incremental Compile增量编译技术详解

Vivado Design Suite 2015.3新增量编译功能介绍

讲述增量编译方法,提高Vivado编译效率

赛灵思软件通过调整编译参数以及运行并行编译来优化FPGA时序性能

Vivado中XDC文件的约束顺序

关于手动伺服优化调整思路分享

在Artix 7 FPGA上使用Vivado的组合逻辑与顺序逻辑

Vivado编译常见错误与关键警告梳理与解析

浅谈Vivado编译时间

每次Vivado编译的结果都一样吗

Vivado里如何手动调整编译顺序

Vivado里如何手动调整编译顺序

评论