解析TI ADS822和ADS825:高性能10位ADC的卓越选择

在电子设计领域,模数转换器(ADC)是连接模拟世界与数字世界的关键桥梁。而德州仪器(TI)推出的ADS822和ADS825这两款10位、40MHz采样的ADC,凭借其出色的性能和广泛的适用性,受到了众多工程师的青睐。下面就为大家详细介绍这两款产品。

文件下载:ads822.pdf

1. 核心特性与优势

高性能指标

ADS822和ADS825具有一系列令人瞩目的特性。高信噪比(SNR)达到60dB,无杂散动态范围(SFDR)高达72dBFS,这意味着在信号转换过程中,能够有效降低噪声和杂散信号的干扰,为后续的信号处理提供更纯净、准确的数字信号。同时,其低功耗设计,正常工作时仅需190mW的功率,还具备20mW的掉电模式,极大地降低了系统的整体功耗,对于需要长时间运行或对功耗敏感的应用场景尤为重要。

灵活的输入输出设计

这两款ADC支持单端或全差分模拟输入,并且输入范围可编程。这种灵活性使得它们能够适应不同类型的信号源和应用需求。此外,ADS825还兼容+3V或+5V逻辑I/O,方便与不同逻辑电平的系统进行接口。

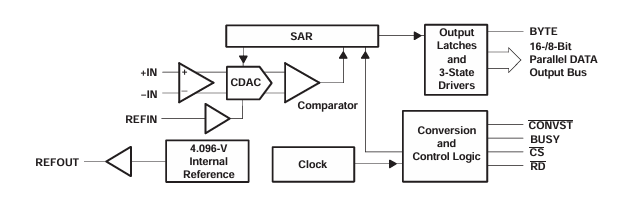

高精度转换

通过采用数字误差校正技术,ADS822和ADS825在10位分辨率下实现了出色的差分线性度,无漏码现象,能够满足对精度要求较高的成像、通信等应用场景。

2. 电气特性剖析

输入特性

在电气特性方面,ADS822和ADS825的模拟输入具有多种可选范围。标准单端输入范围为2Vp-p,对应电压为1.5V - 3.5V;也可选择1Vp-p的单端输入范围,电压为2V - 3V。输入阻抗为1.25MΩ,在3dBFS输入时,输入带宽可达300MHz,能够满足高频信号的采样需求。

转换特性

采样率最高可达40MSPS,数据延迟为5个时钟周期。在动态特性方面,差分线性误差(DNL)最大为±0.5LSB,积分非线性误差(INL)在f = 1MHz时最大为±0.5LSB,保证了转换的高精度。此外,SFDR在f = 1MHz时为72dBFS,在f = 10MHz时为66dBFS,能够有效抑制杂散信号。

数字输入输出特性

数字输入方面,支持TTL、+3V/+5V CMOS兼容的转换时钟上升沿触发。数字输出采用正直偏移二进制编码(SOB),可通过反转最高有效位(MSB)轻松转换为二进制补码。输出电容为5pF,推荐数据线上的电容负载 ≤ 15pF,以避免影响性能。

3. 引脚配置与功能

ADS822和ADS825采用SSOP - 28封装,引脚配置丰富且合理。各个引脚都有其特定的功能,例如:

- 电源与地引脚:+Vs为+5V电源引脚,GND为接地引脚,为芯片提供稳定的电源供应。

- 数据输出引脚:Bit1 - Bit10为10位数据输出引脚,输出转换后的数字信号。

- 控制引脚:OE为输出使能引脚,HI为高阻抗状态,LO为正常工作状态;PD为掉电引脚,HI为使能掉电模式,LO为正常工作。

- 参考与输入选择引脚:RSEL用于输入范围选择,HI为2V,LO为1V;INT/EXT用于参考选择,HI为外部参考,LO为内部参考。

通过合理配置这些引脚,工程师可以根据实际应用需求灵活调整芯片的工作模式和参数。

4. 应用电路设计

输入配置

ADS822和ADS825支持多种输入配置方式,以满足不同应用场景的需求。

- AC - 耦合、单电源接口:在单+5V电源供电的情况下,通过合理连接RSEL引脚和配置参考电压,可实现2Vp-p的满量程输入范围。利用两个1.62kΩ电阻创建约+2.5V的共模电压,为驱动放大器提供合适的偏置,无需在放大器和转换器之间使用耦合电容,简化了电路设计。

- AC - 耦合、双电源接口:当选择双电源供电的放大器时,如OPA642,可充分发挥其低失真的特性。通过电容耦合单端信号到ADC输入,并利用两个电阻连接上下参考电压,满足ADC的共模要求,降低失真。

- DC - 耦合与电平转换:对于信号路径包含直流分量的应用,需要采用DC - 耦合方式,并通过接口电路提供直流电平转换。使用双运放进行电平转换,使信号与所选输入范围兼容,同时可通过调整电阻值校正输入信号的直流偏移。

- 单端到差分转换(变压器耦合):在需要将单端信号转换为差分信号输入的应用中,RF变压器是一种不错的选择。选择具有中心抽头的变压器,可施加共模直流电压,实现差分信号转换,同时提高SFDR性能。

参考操作

ADS822和ADS825的内部参考电路由带隙电压参考、上下参考驱动和电阻参考梯组成。通过将RSEL引脚连接到低或高电位,可轻松设置模拟输入摆幅为1Vp-p或2Vp-p的满量程范围。在外部参考模式下,可断开REFT和REFB的缓冲放大器,提高设计的灵活性。同时,为确保参考配置的正常工作,需要在所有参考引脚提供可靠的旁路电容,以减少时钟馈通。

数字输入输出设计

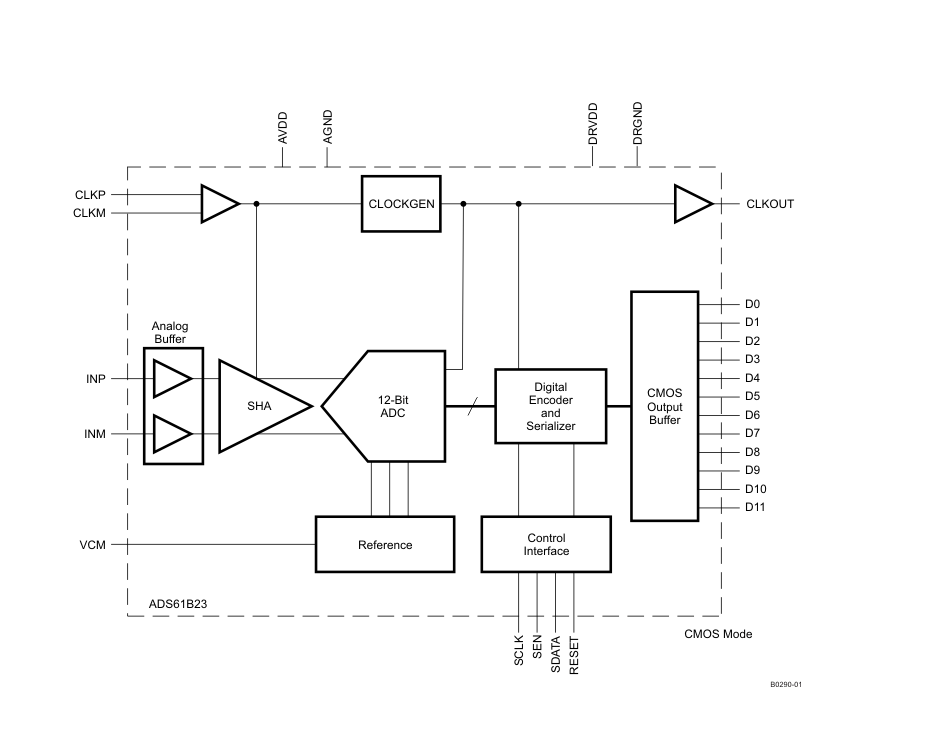

时钟输入要求

时钟抖动对高速、高分辨率ADC的SNR性能至关重要。ADS822和ADS825在CLK输入的上升沿采样输入信号,因此该边沿的抖动应尽可能小。在欠采样应用中,更要特别注意时钟抖动问题,将时钟输入视为模拟输入进行处理,确保时钟信号具有50%的占空比和快速的上升、下降时间。ADS825的时钟输入可驱动3V或5V逻辑电平,使用低电压逻辑(3V)可能会改善转换器的交流性能。

数字输出设计

建议将数据线上的电容负载保持在尽可能低的水平(≤15pF),以避免高电容负载导致的动态电流增大,影响ADC的性能。必要时,可在转换器输出引脚附近使用外部缓冲器或锁存器,减少电容负载并隔离数字噪声。

接地与去耦设计

在高频设计中,正确的接地和去耦设计对于保证ADS822和ADS825的性能至关重要。推荐使用多层PCB板,将芯片视为模拟组件,尽可能使用模拟电源供电,避免数字电源噪声的干扰。所有接地引脚应直接连接到模拟接地平面,模拟信号走线应与数字线路分离,防止噪声耦合。同时,在所有电源和参考引脚提供足够的旁路电容,如0.1µF陶瓷芯片电容和1µF - 22µF的双极性电容,降低阻抗,减少高频电流瞬变和时钟馈通噪声。

5. 封装与订购信息

ADS822和ADS825均采用SSOP - 28封装,具有良好的散热性能和较小的体积,适合高密度电路板设计。在订购时,有多种包装形式可供选择,如管装(TUBE)和卷带包装(Tape and Reel),数量分别为50和1000,满足不同生产规模的需求。

总结与思考

ADS822和ADS825以其高性能、灵活性和丰富的功能特性,为电子工程师在设计模数转换电路时提供了一个优秀的选择。无论是在医疗成像、测试设备、计算机扫描、通信还是视频数字化等领域,都能发挥出色的作用。

在实际应用中,工程师需要根据具体的应用需求和系统要求,合理选择输入配置、参考模式和时钟信号等参数,同时注意接地和去耦设计,以充分发挥这两款ADC的性能优势。那么,在你的项目中,你会如何运用ADS822和ADS825的这些特性来优化设计呢?欢迎在评论区分享你的想法和经验。

-

adc

+关注

关注

100文章

7450浏览量

553836 -

模数转换器

+关注

关注

26文章

3998浏览量

129729

发布评论请先 登录

深入解析ADS2806:高性能12位ADC的设计与应用

解析ADS1625与ADS1626:高性能18位ADC的卓越之选

德州仪器ADS1605/6:高性能16位ADC的设计与应用解析

深入解析ADS1625/6:高性能18位ADC的卓越之选

高性能14位210 MSPS ADC—ADS5547的深度解析

解析TI ADS822和ADS825:高性能10位ADC的卓越选择

解析TI ADS822和ADS825:高性能10位ADC的卓越选择

评论