在现代数字信号处理(DSP)应用中,FPGA(现场可编程门阵列)凭借其高度并行性、可定制性和灵活性,已成为加速信号处理任务的核心硬件平台之一。

作为在该领域具备领先技术的厂商,易灵思推出的 40nm Trion 系列与 16nm 钛金系列(TJ-Series)FPGA,分别面向不同性能层级的 DSP 应用需求,通过高效的 DSP 硬件原语为各类实时信号处理任务提供强大支持。FPGA 中的 DSP 原语是指其内部用于执行数字信号处理操作的基本构建模块,通常包含乘法、加法、累加及移位等专用硬件单元。

与传统的 CPU 相比,FPGA 能够以硬件方式并行处理多个信号流,在诸如音频处理、图像处理、通信系统、雷达与卫星系统等高吞吐、低延迟的应用场景中,展现出显著的性能与能效优势。

本文将重点解析易灵思 FPGA 中的 DSP 原语结构、功能特性及其在实际设计中的使用方法,帮助读者理解如何借助这些硬件资源构建高效的信号处理系统。

Part 01 一、Trion 系列 DSP 原语介绍

Trion 系列采用 40nm 工艺,其 DSP 模块最高运行频率可达 400MHz,具备 18×18 位硬件乘法能力,适用于中等复杂度的数字信号处理任务,下图展示了 Trion 系列 DSP 的运行频率。

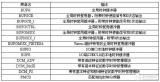

EFX_MULT 原语信号说明:

DSP 是 FPGA 中的一个模块,有输入和输出信号,同时还有一些参数,下图显示 Trion 源语的框图:

针对框图中的各个信号,具体的解释如下:

| Port Name | Direction | Description |

| A[17:0] | Input | Operand A |

| B[17:0] | Input | Operand B |

| CLK | Input | Clock |

| CEA | Input | Clock enable A |

| RSTA | Input | Set/reset A |

| CEB | Input | Clock enable B |

| RSTB | Input | Set/reset B |

| O[35:0] | Output | Multiplier output |

| CEO | Input | Clock enable O |

| RSTO | Input | Set/reset O |

另外在使用 DSP 模块的时候,还需要传递一些参数,如下所示:

总结:易灵思 40nm Trion 系列 FPGA 的一个 DSP 支持 18*18bit 的硬件乘法器,在使用的时候进需要根据原理框图进行例化即可。

在使用 DSP 源语的时候,如果现在数据超过 18*18bit,比如20*20bit 那我们应该怎么办呢?下推荐一种方法:

首先分割输入数据:

对于20位×20位的数据,可以将 20 位输入拆分成两个 18 位的数据进行多次计算。例如,假设输入数据分别为 A[19:0] 和 B[19:0],可以按如下方式拆分:

-> A[19:0]可以分解为:A[17:0](低18位)和 A[19:18](高2位)

-> B[19:0]可以分解为:B[17:0](低18位)和 B[19:18](高2位)

然后可以分别计算四个乘积:

低位乘积:A[17:0] * B[17:0]

高低位乘积:A[19:18] * B[17:0]

低高位乘积:A[17:0] * B[19:18]

高位乘积:A[19:18] * B[19:18]

最后,你可以通过加法操作将这些结果合并成一个 20位× 20位 的最终结果。至于采用一个 DSP 复用还是采用多个 DSP 分别计算提高时序,大家可以根据自己的需求自行设计。

Part 02 二、钛金系列 DSP 原语进阶特性

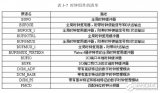

相信有了易灵思 Trion DSP 的源语知识,那么我们再来看钛金系列DSP 模块就会简单一些,易灵思钛金系列采用 16nm 工艺制造,因此其 DSP 的峰值频率可以到达 1000Mhz,如下所示:

与 Trion 的 DSP 相比,钛金系列 FPGA 具有高性能、复杂的 DSP 模块,能够执行乘法、加法、减法、累加以及4位可变右移操作,并支持多种工作模式,具备更强的运算灵活性与并行处理能力。每个DSP模块有四种工作模式,分别支持以下乘法操作:

正常模式(Normal):支持 19×18 位整数乘法和 48 位加法/减法。

双通道模式(Dual):支持 11×10 位整数乘法和1个 8×8 位整数乘法,并具有两个 24 位加法/减法。

四通道模式(Quad):支持 7×6 位整数乘法和三个 4×4 位整数乘法,并具有四个 12 位加法/减法。(注意:7×6 模式的输出会被截断为 12 位。)

浮点模式(Float):支持一个融合乘加/减/累加(FMA)BFLOAT16 浮点乘法。

这些整数乘法器可以表示带符号或无符号数,具体取决于SIGNED参数。当多个EFX_DSP12或EFX_DSP24原语映射到同一个 DSP 模块时,它们必须使用相同的SIGNED值。乘法器的输入数据可以是 A 和 B ,且输出结果可以用于加法或减法操作。

EFX_DSP48 结构简介

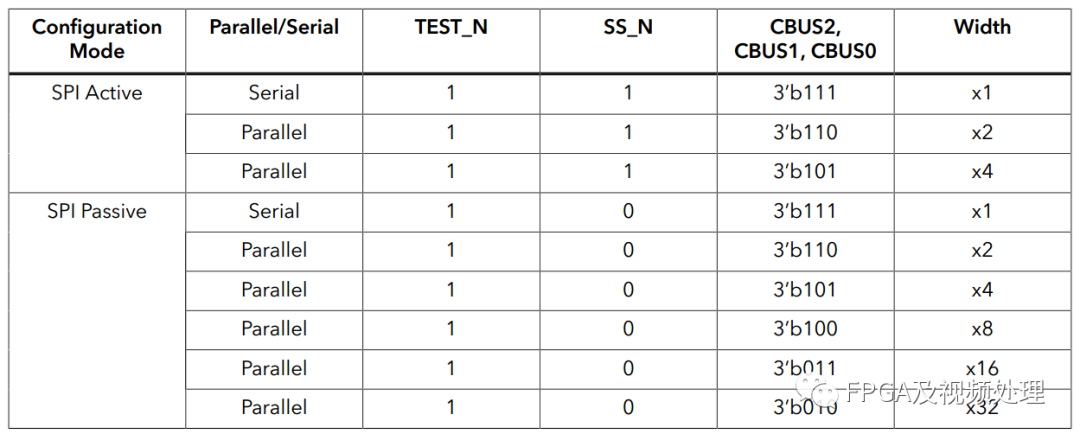

下图是钛金系列 FPGA DSP48 的源语框图:

图中显示了 DSP 中的整体原理。图中蓝色是对应的寄存器,我们可以看到一个 DSP48 有一个 19*18bit 的有符号的乘加器,输出 37 bit ,之后经过 P 寄存器(用户可以自己决定是否启用)到达 pext,pext 用于扩展 37bit 到 48bit,分为 ALIGN_LEFT:左对齐,右边的位补 0 ; ALIGN_RIGHT ,左边补符号位(取决于符号位是 0 还是1 ),pext 同时连接了多个输出,比如可以通过 M 二选一模块进入加法器模块,也可以通过 CASCOUT_SEL 选择 CASCOUT 输出。

如果选择了进入加法器模块,M_SEL 和 N_SEL 可以选择加法器的两个输入,同时 OP[1:0] 可以选择加法器的功能(如下图信号解释表格所示),加法器的结果可以通过 W_SEL 选择输出到 W 寄存器,最终通过 O 寄存器输出。

下面是 DSP48 模块的信号框图和信号详解,读者可以根据对应的解释和上面的原理框图进行理解:

钛金系列DSP48 工作模式详解:

1. Normal 模式

功能:实现 19×18 位整数乘法,产生 37 位结果(P),并可扩展至 48 位。乘法器支持有符号或无符号运算,具体由 SIGNED 参数控制。

扩展与移位:C 输入为 18 位,可通过 C_EXT 参数扩展至 48 位。逻辑移位器支持右移 0-15 位,移位方式(算术或逻辑)取决于 DSP 块的符号设置。移位值由 SHIFT_ENA 端口使能时从 C 输入捕获。

适用场景:需要高精度乘法的应用,如滤波器设计或大型累加运算。

2. Dual 模式

功能:同时执行一个 11×10 位乘法(21 位结果)和一个 8×8 位乘法(16 位结果),两个结果均扩展至 24 位。

数据路径:C 输入被分配到两个数据路径,每个路径可独立扩展。移位器功能与 Normal 模式类似,支持动态移位控制。

适用场景:中等并行度的信号处理,例如双通道音频处理或图像处理中的像素运算。

3. Quad 模式

功能:实现一个 7×6 位乘法(13 位结果,被截断为 12 位)和三个 4×4 位乘法(各 8 位结果,扩展至 12 位)。注意:7×6 乘法的输出会被截断,因此计算范围受限。

特殊处理:C 输入分为四个数据路径。移位器支持多通道独立移位,增强了灵活性。

适用场景:高并行低精度任务,如机器学习中的权重计算或多通道传感器数据处理。

4. Float 模式

功能:支持 BFLOAT16 格式的融合乘加(FMA)操作,输入为 BFLOAT16,输出为 FP32 格式。此模式专为 AI 和机器学习应用优化。

配置要求:必须启用 A_REG、B_REG、P_REG、OP_REG 和 W_REG 等寄存器参数,并设置 P_EXT 和 C_EXT 为 ALIGN_RIGHT。移位器被旁路。

输出格式:O 输出包含错误标志位(如溢出、无效操作),位 [31:0] 为 FP32 数据。

适用场景:浮点密集型应用,如神经网络推理或科学计算。

在使用易灵思钛金系列DSP源语的时候,读者需要根据自己的位宽灵活选择模式,达到最优的资源利用率和最少的 DSP 占用,DSP 更多的使用方法请查看源语手册。

Part 03 三、总结

易灵思 FPGA 的 DSP 原语从 Trion 系列的 18×18 定点乘法器到钛金系列支持 1000Mhz、多模式可配置的 DSP48 模块,均体现出其在硬件加速方面的持续优化与创新。

无论是中低复杂度的嵌入式处理,还是高吞吐、多通道的实时信号处理任务,设计师均可通过合理选用和配置相应的 DSP 原语,充分发挥易灵思 FPGA 在性能、功耗和灵活性方面的综合优势,构建出高效、可靠的数字信号处理系统。

通过本文对易灵思 DSP 原语结构、功能及使用方法的系统介绍,希望读者能够更深入地理解其工作原理,并将其灵活运用于实际项目设计中,以实现更优的信号处理解决方案。

易灵思公司介绍

易灵思是一家国产FPGA公司,总部位于深圳前海。公司凭借自主可控的Quantum硬件架构,采用逻辑和路由可以互换的XLR结构,实现了创新的产品设计与软件算法,使得FPGA产品具备低功耗、小体积、高密度、高性能等优势。已量产的40nm Trion系列及16nm钛金系列 FPGA产品,广泛应用于机器视觉、显示、工业控制、医疗、汽车、AI和通信等终端领域。

重要产品

钛金系列FPGA具有增强的Quantum架构,16nm工艺,35K 至 1,000K 逻辑单元,超高性能 300-500MHz,封装最小可至3.5mm*3.4mm@60K LE,功耗低至竞争对手的1/4,硬核资源丰富,最新产品TJ375现已量产。

-

dsp

+关注

关注

559文章

8219浏览量

364052 -

FPGA

+关注

关注

1656文章

22293浏览量

630436 -

数字信号

+关注

关注

2文章

1055浏览量

48968 -

易灵思

+关注

关注

6文章

63浏览量

5499

原文标题:易灵思FPGA DSP原语使用方法

文章出处:【微信号:易灵思官微,微信公众号:易灵思官微】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

易灵思(Elitestek)FPGA编程器功能特点及驱动安装方法

FPGA设计之浮点DSP算法实现【赛灵思工程师作品】

易灵思推Trion Titanium FPGA,采用 “Quantum™ 计算架构”

易灵思FPGA产品帮助安防领域创新和突破

易灵思FPGA软件更新的节奏,也许能磨出一个好产品

易灵思FPGA产品的主要特点

易灵思FPGA DSP原语使用方法

易灵思FPGA DSP原语使用方法

评论