FSW6820是四方杰芯研发的三通道差分 4:1高速双向无源开关,定位为 USB Type-C 生态的核心信号切换器件,可实现 “USB 3.1 Super Speed(5Gbps)+ USB 2.0(480Mbps)” 混合信号的切换需求。其采用自适应跟踪技术,确保 0~2V 共模电压范围内通道特性稳定,且具备低衰减、低抖动的动态性能,适用于对信号完整性和功耗敏感的高速接口场景。

关键特性(表格展示)

| 特性分类 | 关键参数 | 规格详情 | 备注 |

|---|---|---|---|

| 通道配置 | 通道数量 / 切换比例 | 3 组差分通道,支持4:1 Mux/DeMux | 可同时切换 3 路独立差分信号 |

| 带宽性能 | USB 3.1 带宽 | 6.2GHz@-3dB BW | 满足 USB 3.1 Gen 1(5Gbps)需求 |

| USB 2.0 带宽 | 1GHz | 兼容 USB 2.0 高速(480Mbps)信号 | |

| 信号隔离 | 关态隔离度 | -45dB@5GHz | 抑制未选通道信号泄漏 |

| 串扰 | -11dB@5GHz | 减少通道间信号干扰 | |

| 可靠性 | ESD 耐受 | 2kV HBM | 提升设备抗静电能力 |

| 功耗 | 工作功耗 | <2mW | 正常运行时低功耗 |

| 关断功耗 | <20uW | EN 引脚使能关断模式时 | |

| 其他 | 信号耦合 | 支持 AC 耦合、DC 耦合 | 设计灵活性高 |

| 导通电阻匹配 | ΔRON=0.1Ω(Typ.) | 保证多通道信号一致性 |

引脚配置(核心引脚表格)

| 引脚号 | 引脚名称 | 信号类型 | 关键描述 |

|---|---|---|---|

| 1 | EN1 | I | 使能引脚,低电平有效 |

| 2 | SEL1 | I | 通道选择引脚 1,配合 SEL2 确定通道 |

| 3-4 | COMAN/COMAP | I/O | USB 3.1 公共端 1 的差分信号对(负 / 正) |

| 5-6 | COMBN/COMBP | I/O | USB 3.1 公共端 2 的差分信号对(负 / 正) |

| 7-8 | COMCN/COMCP | I/O | USB 2.0 公共端 3 的差分信号对(负 / 正) |

| 13 | VCC | Power | 电源正极(1.8~4.5V) |

| 14 | 3EN | I | 使能引脚 3,低电平有效 |

| 28 | GND | Ground | 电源地(主接地引脚) |

| 37 | 2EN | I | 使能引脚 2,低电平有效 |

| 38 | SEL2 | I | 通道选择引脚 2,配合 SEL1 确定通道 |

| 39 | VCC | Power | 电源正极(辅助供电,增强稳定性) |

| 40 | GND | Ground | 电源地(辅助接地) |

真值表(通道选择逻辑)

| 使能状态(EN1&2EN&3EN) | SEL1 | SEL2 | 导通通道(公共端 ↔ 输入端口) |

|---|---|---|---|

| High(关断) | X | X | 所有通道呈 Hi-Z(高阻态) |

| Low(使能) | Low | Low | 公共端 ↔ 端口 A(DAxP/DAxN) |

| Low(使能) | Low | High | 公共端 ↔ 端口 B(DBxP/DBxN) |

| Low(使能) | High | Low | 公共端 ↔ 端口 C(DCxP/DCxN) |

| Low(使能) | High | High | 公共端 ↔ 端口 D(预留 / 扩展) |

注:x=1~4,对应 4 组输入信号的差分对。

最大额定值(表格展示)

| 参数名称 | 规格范围 | 单位 |

|---|---|---|

| 存储温度 | -65 ~ +150 | ℃ |

| 结温 | 125 | ℃ |

| 电源电压(VCC-GND) | -0.5 ~ +5.5 | V |

| 高速数据通道电压(TX/RX) | -0.5 ~ 3.8 | V |

| DC 输入电压 | -0.5 ~ VCC | V |

| DC 输出电流 | 50 | mA |

| 功率损耗 | 300 | mW |

注:超出额定值可能导致芯片永久损坏,仅为应力参考,非工作参数。

电气特性(TA=25℃,VCC=3V,表格展示)

| 特性分类 | 参数符号 | 测试条件 | 最小值 | 典型值 | 最大值 | 单位 |

|---|---|---|---|---|---|---|

| 电源特性 | IQ(静态电流) | SEL=0/VCC,EN1~3=0 | - | - | 100 | uA |

| IPO(关断电流) | SEL=0/VCC,EN1~3=VCC | - | - | 3 | uA | |

| DC 特性 | VIH(输入高电平) | VCC=1.8~4.5V | 1.6 | - | - | V |

| VIL(输入低电平) | VCC=1.8~4.5V | - | - | 0.4 | V | |

| RUP(EN 内部上拉电阻) | - | - | 2 | - | MΩ | |

| RDN(SEL 内部下拉电阻) | - | - | 2 | - | MΩ | |

| RON_HS(导通电阻) | V_IS=1.5V,I_ON=10mA | - | 13.4 | - | Ω | |

| AC 特性 | tEN(使能时间) | RL=50Ω,CL=0pF,V_IS=0.6V | - | 80 | 150 | uS |

| tDIS(关断时间) | RL=50Ω,CL=0pF,V_IS=0.6V | - | 40 | 250 | nS | |

| tON(开启时间) | RL=50Ω,CL=0pF,V_IS=0.6V | - | 400 | 1200 | nS | |

| tOFF(关闭时间) | RL=50Ω,CL=0pF,V_IS=0.6V | - | 130 | 800 | nS | |

| tBBM(先断后合时间) | RL=50Ω,CL=0pF,V_IS=0.6V | - | 250 | 800 | nS | |

| BW(-3dB 带宽) | RL=50Ω,CL=0pF,0dBm 信号 | - | 6.2 | - | GHz | |

| IL(插入损耗) | f=5GHz | - | -2.76 | - | dB | |

| 电容特性 | CON(导通电容) | V_Bias=0.2V,f=1.5GHz | - | 1.5 | - | pF |

| COFF(关断电容) | V_Bias=0.2V,f=1.5GHz | - | 1.0 | - | pF |

应用场景

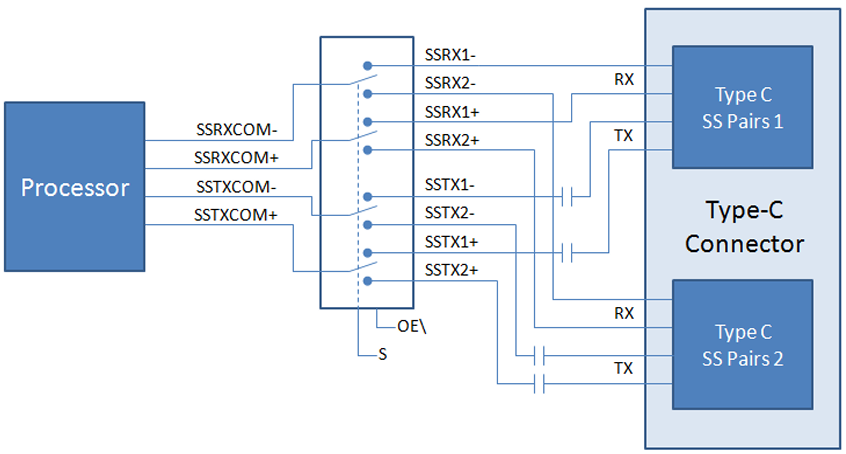

USB Type-C 生态系统:如 USB-C 集线器、扩展坞,实现多设备共享一个 USB-C 接口;

台式机 / 笔记本 PC:用于内部 USB 3.1/2.0 信号的路径切换(如主机与外设间切换);

服务器 / 存储区域网络:PCI Express 背板的高速信号共享,或存储设备的 I/O 端口切换;

其他高速接口:FPD LinkII/III 视频信号切换(如车载显示、工业摄像头)。

PCB 设计要点

AC 耦合电容选择:

封装优先0402,其次0603,严禁使用 0805 或 C-packs;

容值推荐0.1μF,且同一差分对的电容容值需完全匹配;

放置位置:仅能在开关的单侧边放置(避免隔断偏置电压),若系统共模电压 > 2V,需在开关两侧放置电容并额外提供 < 2V 的 VBIAS 偏置电压。

信号布线:

差分信号对需等长、平行、紧密耦合,减少信号 skew;

高速信号(USB 3.1)远离数字控制引脚(SEL1/SEL2、EN1~3),降低串扰。

电源与接地:

VCC 引脚旁需紧靠放置0.1μF 去耦电容,且电容接地路径最短;

多 GND 引脚需均良好接地,形成完整地平面,提升信号稳定性。

封装与包装信息

封装类型:QFN5x5-40L(5mm×5mm,40 引脚无铅方型扁平封装);

包装方式:卷带包装(Tape and Reel),每卷5000 颗;

顶部丝印:格式为 “FXX YYWW”,其中 YY 为年份(如 24=2024)、WW 为周数(01~53)、FXX 为内部 ID 码。

版本修改记录

| 版本号 | 修订内容 |

|---|---|

| first edition | 初始版本 |

| V1.0 | 1. 更新第 5 页 “电气特性” 的测试条件及 “TX/RX 导通电阻” 参数 |

| V2.0 | 1. 更新第 5-6 页 “电气特性”;2. 更新第 1 页 “关键特性” |

| V3.0 | 1. 更新第 12 页 “重要声明与免责条款” |

关键问题

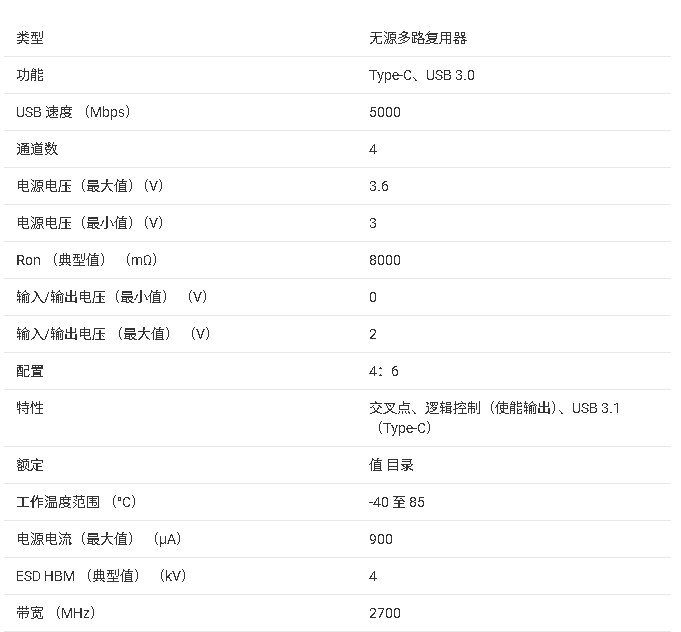

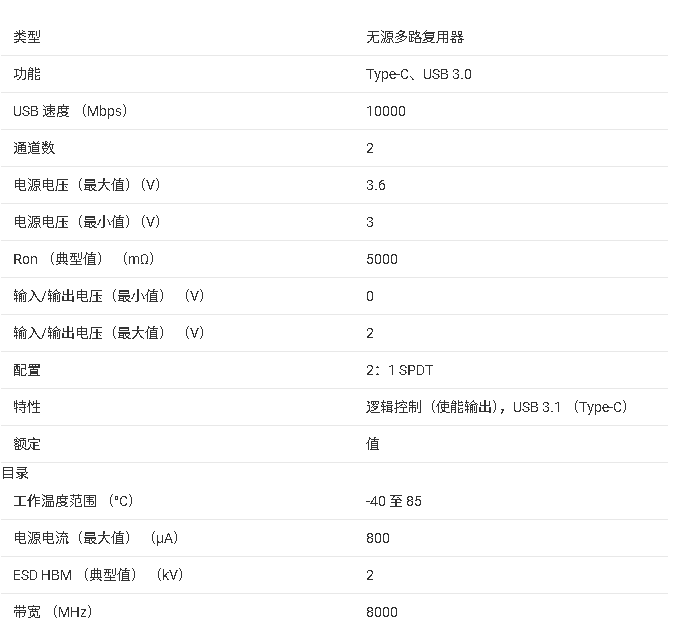

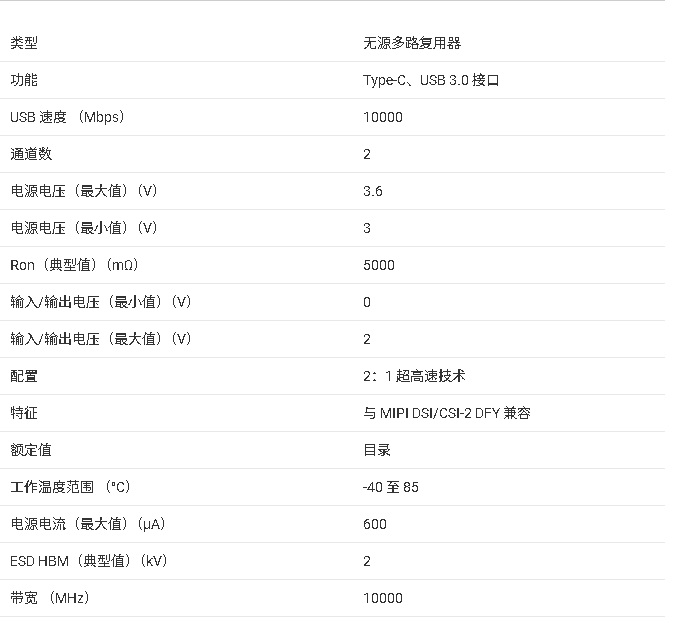

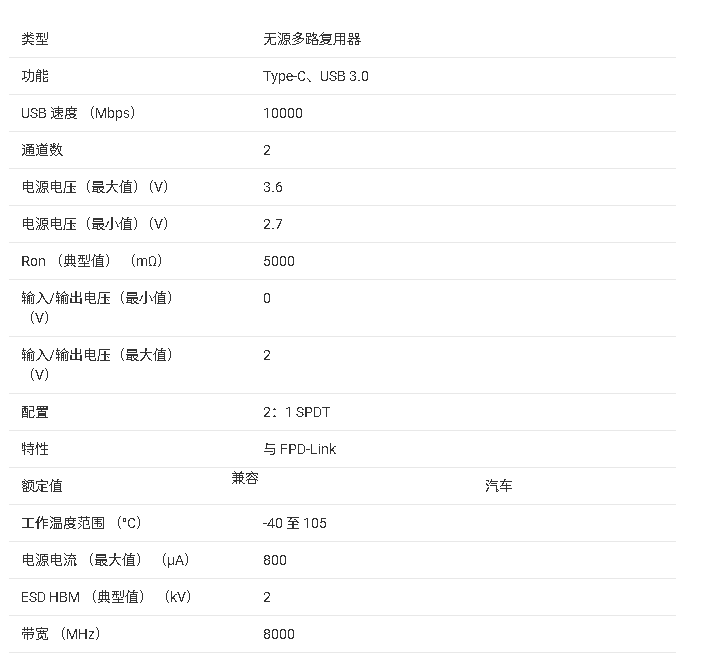

问题 1:FSW6820 与四方杰芯的 FSW3410(双通道 2:1)、FSW3820(四通道 2:1)相比,核心差异是什么?适合哪些特定场景?

答案:三者核心差异集中在通道数量和切换比例,决定了适用场景的不同,具体对比如下:

| 芯片型号 | 通道数量 | 切换比例 | 核心优势 | 适用场景 |

|---|---|---|---|---|

| FSW3410 | 2 组差分 | 2:1 | 体积小(QFN2.8x2.0-18L)、带宽高(11GHz) | 简单 2 选 1 场景(如单 USB 3.1 接口切换) |

| FSW3820 | 4 组差分 | 2:1 | 多通道同步切换(4 组) | PCIe 背板、服务器多设备 2 选 1 |

| FSW6820 | 3 组差分 | 4:1 | 支持 USB 3.1+USB 2.0 混合切换、4 选 1 灵活性 | USB-C 扩展坞(多设备共享 1 个 C 口)、复杂 I/O 共享 |

结论:FSW6820 的 “4:1 切换” 和 “USB 3.1+2.0 兼容” 是核心差异化优势,更适合需要连接多个 USB 设备(如 4 个外设共享 1 个主机接口)的场景。

问题 2:FSW6820 为何能同时支持 USB 3.1 Super Speed(5Gbps)和 USB 2.0(480Mbps)信号切换?硬件设计上如何实现两者兼容?

答案:FSW6820 通过 “专用信号通道分配” 和 “带宽分级设计” 实现双标准兼容,具体原理如下:

信号通道独立分配:

芯片的 3 组公共端中,COMAN/COMAP、COMBN/COMBP专为 USB 3.1 Super Speed 设计(支持差分信号传输),COMCN/COMCP专为 USB 2.0 设计(兼容 USB 2.0 的 DP/DM 差分对);

输入端口对应分为 A/B/C/D 四路,每路同时包含 USB 3.1 和 USB 2.0 的差分信号引脚(如 DA1P/DA1N 为 USB 3.1,DC1P/DC1N 为 USB 2.0),切换时两组信号同步选通。

带宽分级匹配:

USB 3.1 通道带宽设计为6.2GHz,满足 5Gbps 传输的信号完整性需求;

USB 2.0 通道带宽设计为1GHz,远超 USB 2.0 480Mbps 的速率要求,同时避免高带宽带来的额外功耗;

电气参数适配:

导通电阻(RON_HS=13.4Ω Typ.)和隔离度(-45dB@5GHz)兼顾两种速率的信号损耗需求,既保证 USB 3.1 的低衰减,也满足 USB 2.0 的抗干扰要求。

问题 3:设计中使用 FSW6820 的 EN1/EN2/EN3 使能引脚时,需注意哪些关键要点?如何避免功能异常?

答案:EN1/EN2/EN3 是芯片的核心使能引脚(低电平有效),设计时需关注 3 个要点:

引脚有效电平与内部电阻特性:

引脚为低电平有效(电压≤0.4V 时使能),高电平(≥1.6V)时芯片关断(所有通道 Hi-Z);

芯片内置2MΩ 的 EN 引脚内部上拉电阻,若外部未驱动 EN 引脚,引脚会被拉至 VCC(关断状态),需通过外部 GPIO 主动拉低才能使能,避免 “悬空导致的不确定状态”。

多 EN 引脚的协同作用:

EN1/EN2/EN3 需同时为低电平才能使能芯片(文档真值表中 “EN1&2EN&3EN=Low” 为使能条件),任意一个为高电平则芯片关断;

设计时建议将 3 个 EN 引脚连接到同一 GPIO(或同一控制信号),避免单独控制导致的误关断。

关断模式的功耗与信号隔离:

关断模式下电流仅3uA(Max.),适合低功耗场景(如设备休眠时);

关断时所有通道呈 Hi-Z,隔离度保持 - 45dB@5GHz,可有效切断未使用通道的信号泄漏,需确保关断时外部设备不会通过 Hi-Z 通道产生漏电流(如避免 USB 设备的 VBUS 通过信号引脚供电)。

审核编辑 黄宇

-

芯片

+关注

关注

462文章

53559浏览量

459333 -

usb

+关注

关注

60文章

8373浏览量

281772 -

高速信号

+关注

关注

1文章

263浏览量

18462

发布评论请先 登录

四方杰芯 FSW3820 芯片简介:高速差分信号切换芯片替代 TI HD3SS3212

四方杰芯FSW7227芯片简介:USB2.0二切一开关芯片替代SGM7227

四方杰芯 FSW6860 芯片简介:五通道高速差分 + 低速模拟混合信号切换芯片 功能替代 ASW3642

HD3SS460芯片技术文档总结

HD3SS3212芯片技术文档总结

HD3SS3220 USB Type-C DRP端口控制器技术文档总结

HD3SS3202芯片技术文档总结

HD3SS3212-Q1 产品技术文档总结

HD3SS3220/HD3SS3220L USB Type-C控制器技术文档总结

芯详EMS4100: USB 3.1高速模拟开关芯片,替代ASW3410方案

四方杰芯 FSW6820 芯片简介:USB 高速信号切换芯片替代 HD3SS6126

四方杰芯 FSW6820 芯片简介:USB 高速信号切换芯片替代 HD3SS6126

评论