1. 核心概述

FSW3820是一款由四方杰芯推出的四通道差分2:1/1:2高速无源开关,专为USB 3.1 Gen 1(5Gbps) 等高速接口设计。它通过SEL引脚在A/B 两个端口之间切换信号,并由**_EN引脚(低电平有效)控制开关的整体使能。其核心优势在于7.8GHz**的高带宽、6.7Ω的低导通电阻和 **-31dB** 的高隔离度,同时功耗极低(工作 <2mW,关断 <20uW)。

2. 关键特性与电气性能

| 特性分类 | 关键参数 | 规格 | 备注 |

|---|---|---|---|

| 基本功能 | 通道配置 | 4-Differential Channel 2:1/1:2 | 可同时切换 4 组差分信号 |

| 数据速率 | USB 3.1 Gen 1 (5Gbps) | 兼容多种高速接口标准 | |

| 性能指标 | 带宽 | 7.8GHz@-3dB | 确保高速信号完整性 |

| 导通电阻 (RON) | 6.7Ω(Typ.) | 低损耗,减少信号衰减 | |

| 隔离度 | -31dB@ 5GHz | 抑制串扰,保证信号纯净 | |

| 串扰 (Crosstalk) | -21dB@ 5GHz | 同上 | |

| 插入损耗 | -2.51dB @ 5GHz | 信号功率损失小 | |

| 功耗控制 | 工作电流 | 28uA(Max.) | 极低功耗,适合便携设备 |

| 关断电流 | 1uA(Max.) | 深度休眠,节省能源 | |

| 信号兼容性 | 共模电压范围 | 0 to 2V | 适应多种高速接口 |

| 信号耦合方式 | 支持 AC 和 DC 耦合 | 设计灵活性高,但需注意偏置 |

3. 引脚配置与功能

芯片采用QFN4x4-32L封装,关键引脚功能如下:

信号路径引脚:

D0±,D1±,D2±,D3±: 4 组公共端(COM)差分信号对。

D0±A...D3±A: A 端口的 4 组差分信号对。

D0±B...D3±B: B 端口的 4 组差分信号对。

控制引脚:

SEL(Pin 5): 路径选择。低电平选 A,高电平选 B。

_EN(Pin 6): 使能,低电平有效。高电平则所有通道高阻。

电源引脚:

VCC(Pin 15): 电源正极 (1.5V ~ 5.5V)。

GND(Pin 14): 电源地。

路径选择真值表:

| _EN | SEL | 信号路径 |

|---|---|---|

| High | X | Hi-Z(所有通道高阻) |

| Low | Low | Dx± ↔ Dx±A(选择 A 端口) |

| Low | High | Dx± ↔ Dx±B(选择 B 端口) |

4. 应用场景

USB Type-C生态系统(集线器、扩展坞)

台式机和笔记本电脑

服务器 / 存储区域网络

PCI Express背板

共享 I/O 端口

FPD LinkII/III 视频信号切换

5. PCB 设计要点

AC 耦合电容:

位置:必须只放在开关的一侧,以保证开关获得正确的直流偏置。

选型:推荐0.1µF,优先用0402或0603封装,避免 0805。

匹配:同一差分对的两个电容必须容值和封装完全一致。

高速信号布线:

差分对需等长、平行、紧密耦合。

高速走线远离数字控制信号线(SEL,_EN)。

电源与地:

VCC引脚旁紧靠放置0.1µF去耦电容。

确保良好的地平面和散热焊盘连接。

审核编辑 黄宇

-

差分信号

+关注

关注

4文章

405浏览量

28873

发布评论请先 登录

MD6639高速DAC芯片替代TI、ADI

四方杰芯FSW7227芯片简介:USB2.0二切一开关芯片替代SGM7227

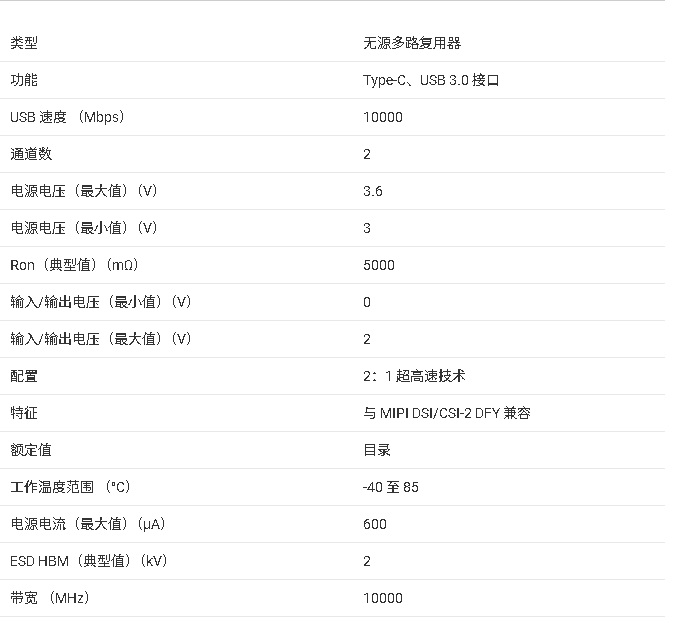

四方杰芯 FSW6860 芯片简介:五通道高速差分 + 低速模拟混合信号切换芯片 功能替代 ASW3642

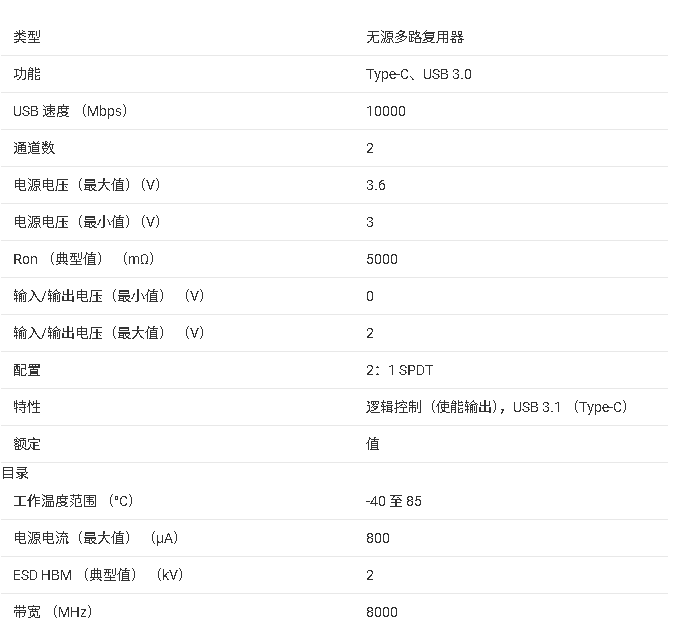

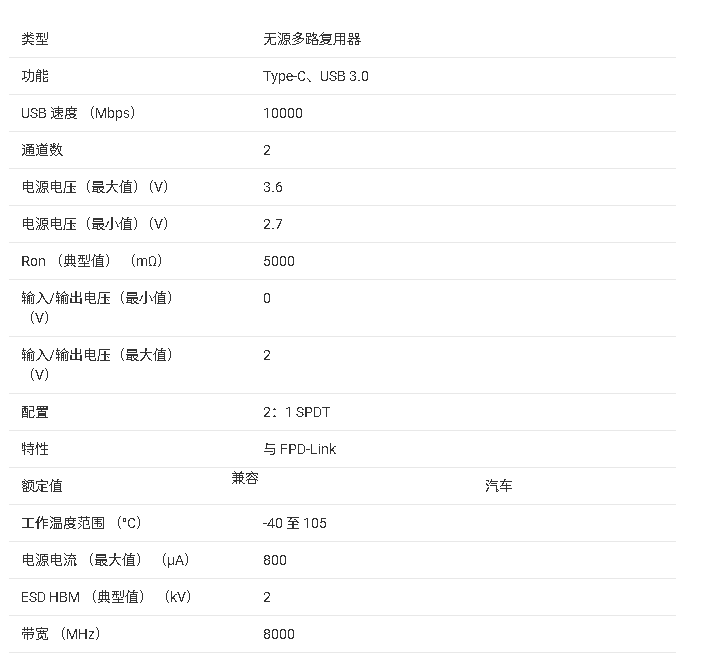

四方杰芯 FSW6820 芯片简介:USB 高速信号切换芯片替代 HD3SS6126

HD3SS3212芯片技术文档总结

HD3SS3212-Q1 产品技术文档总结

四方杰芯 FSW3820 芯片简介:高速差分信号切换芯片替代 TI HD3SS3212

四方杰芯 FSW3820 芯片简介:高速差分信号切换芯片替代 TI HD3SS3212

评论